xilinx IP核之ROM

背景

xilinx的IP核中比较常用的还有ROM核,同CMT IP核一样,xilinx也提供了用于实现ROM功能的IP核较Block Memor Generator IP 核,这个IP核继承了单/双端口的ROM和RAM IP核。这里我们就以单端口ROM IP核为例子。

应用

1、coe文件的创建方法

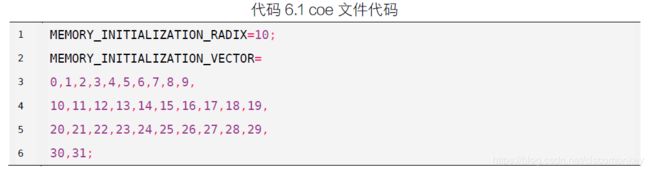

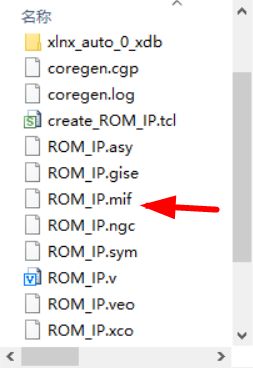

在开始创建工程之前,先介绍一下coe文件的创建方法,它是用来配置RAM或者ROM中的数据。但是与Alteral公司的Quartus II 软件使用的HEX和MIF文件相比,Xilinx ISE软件使用的coe文件不支持matlab等软件直接生成,只能通过文本编辑器人工输入。coe文件与HEX文件实质上是相同数据的不同表达方式,都只在IP核新建时起作用。IP核生成以后,ISE软件会生成与之命名相同的MIF文件,利用modelsim软件仿真时只识别调用mif文件。总之,coe文件与mif文件只是格式上的区别,仿真只使用mif文件,原先导入数据的ce文件不再发挥作用。

我们可以使用下面的方法来建立.coe格式文件;

1、利用C语言、matlab或者一些实用的软件工具生成我们想要的波形的数据。

2、新建一个txt文本文件,双击打开;

3、在第一行写入“MEMORY_INITIALIZATION_RADIX=10;”,表示ROM里的数据以10进制表示。

4、在第二行写入“MEMORY_INITIALIZATION_VECTOR=",在这之后就可以写入波形的数据了。

5、保存txt文本文件,将文件的后缀名改为.coe

其实,说白了,其实我们可以继续使用mif文件,然后把生成的数据都拷贝出来。

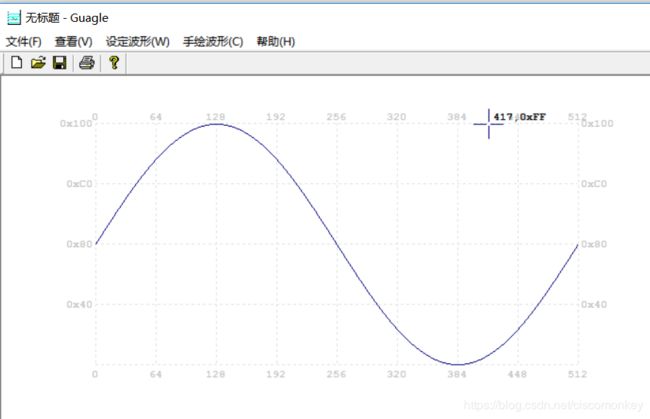

比如说如上图所示,我们可以生成一个正弦波信号。

2、使用ISE软件创建ROM IP核

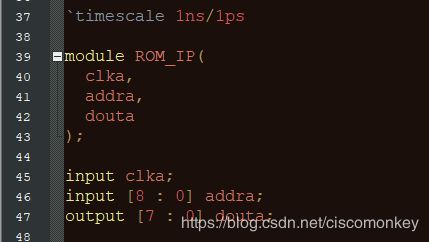

创建好了coe文件,接下来我们就来创建ROM IP核。

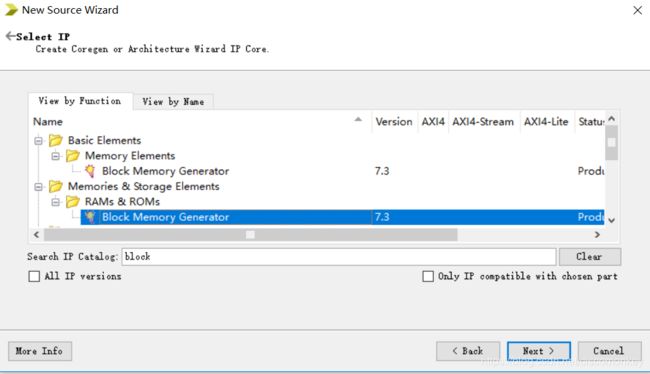

在该页面中,我们在“search IP catalog”栏中输入“BLOCK”,然后在“VIEW by Function”中可以看到“Block Memory Generator”了,选中“Block Memory Generator”后点击next,启动IP配置

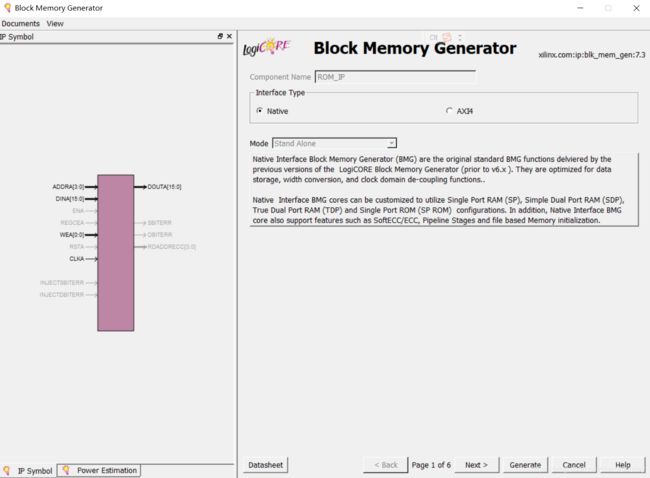

配置页面1

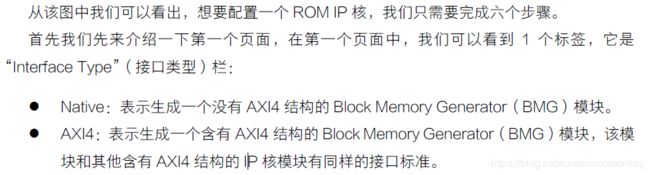

配置页面2

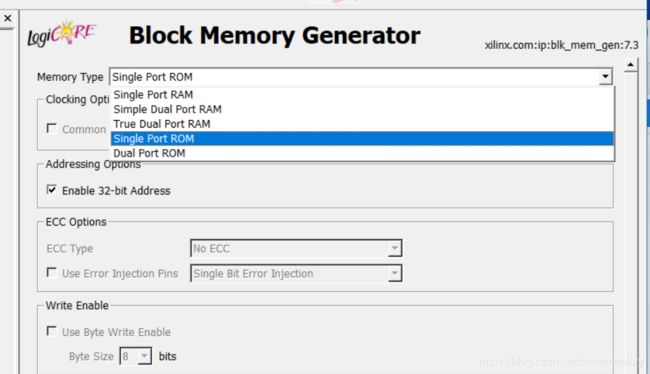

在这个页面中,我们首先需要选择存储器的类型为“Single Port ROM”。然后还有2个可供修改的标签“Addressing Option”(寻址选项)和“Algorithm”(算法)。关于“Addressing Options”栏,我们可以选择是否使能32bit的地址长度。在“Algorithm”栏,有以下三种选项;

在这个页面中,我们选择存储器的类型为“single port ROM”,然后点击next进入第三个页面

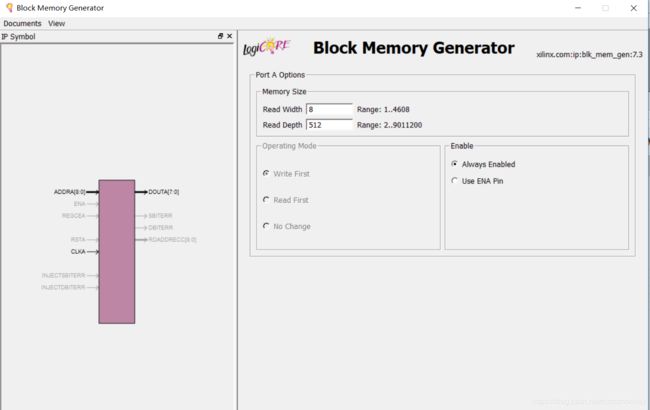

配置页面3

在这个页面中,我们设置“Read width”为8bits,“Read Depth”为512个,设置“Enable”栏为“Always Enabled”。然后点击【next】进入第四个页面。

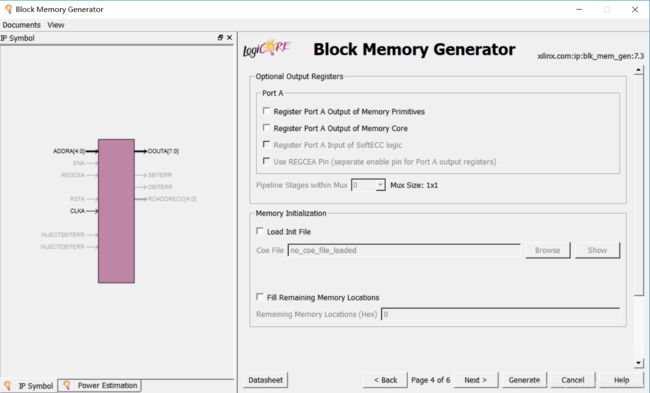

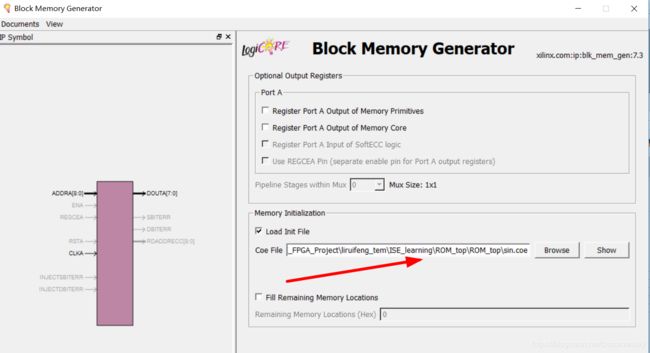

配置页面4

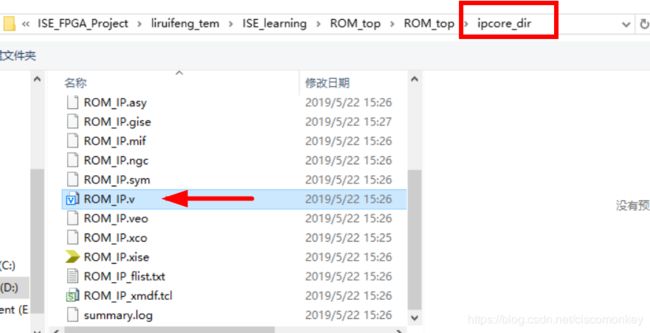

在这个页面中,我们选中load init file 栏,设置“coe file”栏的路径。然后其余的页面我们使用默认设置即可。创建好了ROM IP核之后,我们需要在顶层模块中实例化我们的ROM IP核。如果coe文件正常无误,那么路径是黑色,否则是红色。

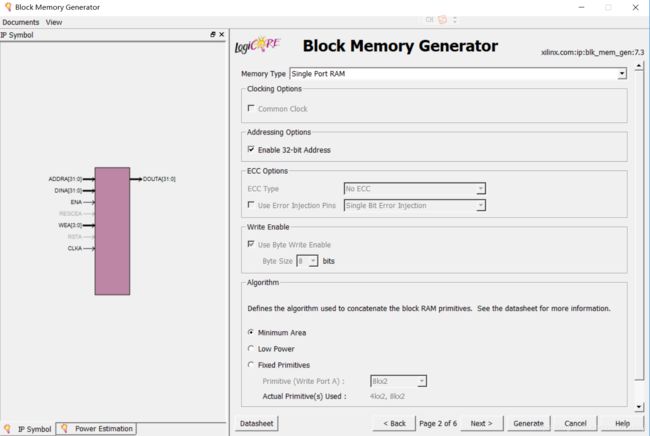

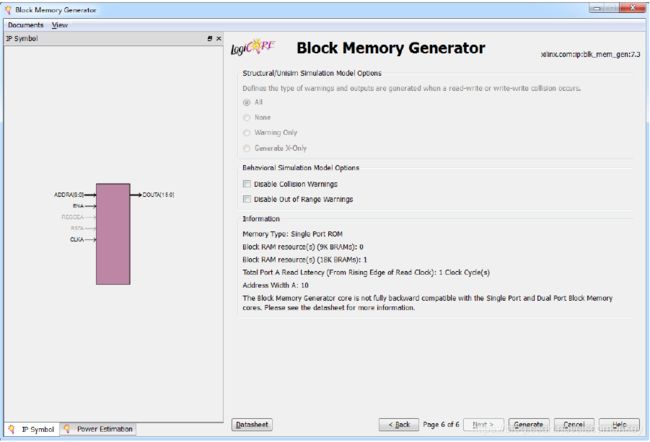

配置页面5

配置页面6

在这个页面中,只有1个可供修改的标签“ower estimate option”(功耗估计选项)的“output reset option”(输出复位选项)的“port A”(端口A)可以选择是否添加一个“RSTA”引脚。

最终我们可以看到本质上,ISE软件又将其coe文件转换成了mif文件