前言

FPGA主要运用于芯片验证、通信、图像处理。显示VGA接口的显示器是最基本的要求了。

原理

首先需要了解 :

(1)VGA接口协议:VGA端子_维基百科 、VGA视频传输标准_百度

| 引脚1 | RED | 红色视频 | |

|---|---|---|---|

| 引脚2 | GREEN | 绿色视频 | |

| 引脚3 | BLUE | 蓝色视频 | |

| 引脚4 | ID2/RES | 过去为屏幕ID比特2;自DDC2起保留 | |

| 引脚5 | GND | 接地(水平同步) | |

| 引脚6 | RED_RTN | 红色接回 | |

| 引脚7 | GREEN_RTN | 绿色接回 | |

| 引脚8 | BLUE_RTN | 蓝色接回 | |

| 引脚9 | KEY/PWR | 过去为key;现为 +5V DC | |

| 引脚10 | GND | 接地(垂直同步,DDC) | |

| 引脚11 | ID0/RES | 过去为屏幕ID比特0;自E-DDC起保留 | |

| 引脚12 | ID1/SDA | 过去为屏幕ID比特1;自DDC2起为I²C数据 | |

| 引脚13 | HSync | 水平同步 | |

| 引脚14 | VSync | 垂直同步 | |

| 引脚15 | ID3/SCL | 过去为屏幕ID比特3;自DDC2起为I²C时钟 | |

| 图表中详叙了较新的15针VESA DDC2连接头。图标中的针脚编号是显卡常见的母接头;在公接头上的针脚相当于图例的左右镜像。 | |||

最主要的几根线:

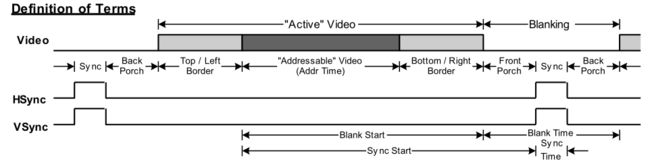

(2)VGA时序

各种分辨率的显示器时序参数:http://tinyvga.com/vga-timing

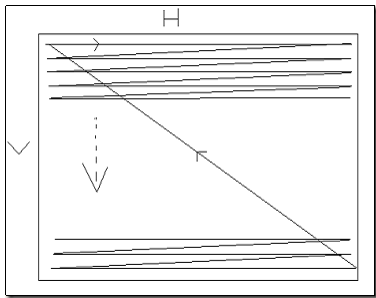

a、扫描轨迹

扫描从屏幕左上方开始,从左至右,从上到下,进行扫描。

每扫描完一行,电子束(CRT)回到屏幕的左边下一行起始位置,在此期间对电子束进行消隐,每行结束时,用行同步信号进行同步。

扫描完所有行,用场同步信号进行场同步,并使扫描回到屏幕的左上方,同时进行消隐,预备下一行的扫描。

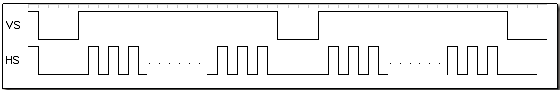

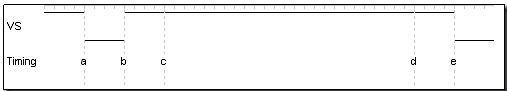

b、行场扫描(工业标准为负,大部分显示器HS、VS可正可负,显示器自动调整,此处为正极性)

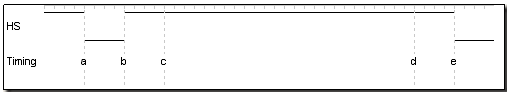

c、HS时序深入分析

可见时序的循环,可被划分为a,b,c,d4个时期。这四个时期定义如下:

A~B:行消隐期 即同步,相当于还原扫描坐标吧

B~C:行消隐后肩 相当于准备开始扫描吧

C~D:行显示期 扫描中,数据有效区域

D~E:行消隐前肩 完成扫描,相当于准备同步

d、VS时序深入分析

可见时序的循环,可被划分为a,b,c,d4个时期。这四个时期定义如下:

A~B:场消隐期 即同步,相当于还原扫描坐标吧

B~C:场消隐后肩 相当于准备开始扫描吧

C~D:场显示期 扫描中,数据有效区域

D~E:场消隐前肩 完成扫描,相当于准备同步

综上描述,我们只要知道每个时期的时间,便可以表示出VGA的时序。而FPGA的工作是由固定频率的时钟触发的,因此某固定时间可以用n次触发来表示。因此我们很容易就想到了FPGA常用的计数方法:比如说行扫描,我们计数0~H_total-1。用另一个进程将其划分为4个时期,按标注分配。其实这相当于状态机。

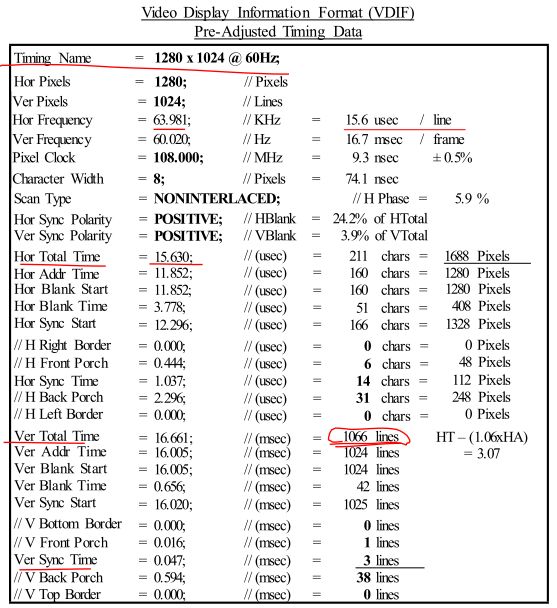

以下是固定分辨率1280*1024 60fps下HS,VS的标准:

有图可得:

①各个时期像素数:

// Horizontal Parameter( Pixel )

H_DISP = 11'd1280,

H_FRONT = 11'd48,

H_SYNC = 11'd112,

H_BACK = 11'd248,

H_TOTAL = 11'd1688,

// Virtical Parameter( Line )

V_DISP = 11'd1024,

V_FRONT = 11'd1,

V_SYNC = 11'd3,

V_BACK = 11'd38,

V_TOTAL = 11'd1066;

②像素时钟频率(即所需的VGA时钟频率)

(H_DISP + H_BACK + H_SYNC + H_FRONT)×(V_DISP + V_BACK + V_SYNC + V_FRONT)× REFRESH_RATE

在此为(1280 + 248 + 112 + 48)×(1024 + 38 + 3 + 1)× 60 = 1688 × 1066 × 60 = 107.964480 MHz (工业标准为 108.000 MHz ,当然都是能正常显示的,推荐用工业标准。)

③一帧图像的数据量(以RGB565 格式为例)

H_DISP × V_DISP × (5 + 6 + 5)bit = [H_DISP × V_DISP × (5 + 6 + 5)bit ] ÷ 8 B = [H_DISP × V_DISP × (5 + 6 + 5)bit ] ÷ 8 ÷ 1024 K

在此为 1280 × 1024 × 16 bit = 20971520 ÷ 8 B = 2621440 ÷ 1024 K = 2560 ÷ 1024 M = 2.5 M

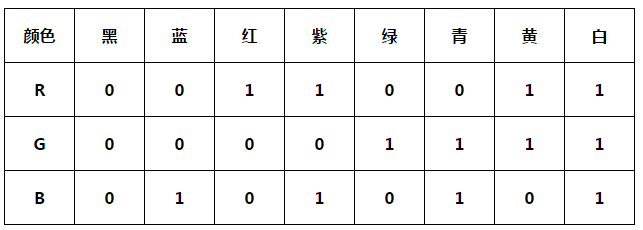

(3)三基色原理

常见的彩色显示器一般都是由CRT (阴极射线管) 构成,每一个像素的色彩由R ( 红, Red) 、G( 绿,Green) 、B(蓝,Blue) 三基色构成。显示时采用的是逐行扫描的方式。由VGA 显示模块产生的水平同步信号和垂直同步信号控制阴极射线管中的电子枪产生电子束,轰击涂有荧光粉的屏幕,产生RGB 三基色,于显示屏上合成一个彩色像素点。

像素是产生各种颜色的基本单元。根据物理学中的混色原理,三色发光的亮度比例适当,可呈现白色。适当的调整发光比例可以出现不同的颜色。

程序设计

显示模块(顶层):

1 /************************************************************************ 2 * Author : yllinux 博客:http://www.cnblogs.com/yllinux/ 3 * Module Name : vga_color_line.v 4 * Tool versions : Quartus II 12.1;Cyclone IV E(EP4CE6F17C8) 5 * Create Date : 2017-7-21 6 * Revision : v1.0 7 * Description : 使1280*1024@60HZ的VGA显示器显示竖彩条 8 ************************************************************************/ 9 10 module VGA_color_line (clk, rst_n, hs_vga, vs_vga, r_vga, g_vga, b_vga); 11 12 input clk, rst_n; //系统时钟和低电平复位 13 output hs_vga, vs_vga; //行同步hs_vga,场同步vs_vga 14 output r_vga, g_vga , b_vga; //像素三基色输出R、G、B 15 reg [2:0] rgb_vga; //相当于输入信号了 16 wire clk_vga; //像素时钟 1688 * 1066 * 60 MZ (工业标准 108 MHZ) 17 18 // VGA_1280_1024_60fps_50MHz 19 // Horizontal Parameter( Pixel ) 20 parameter 21 H_DISP = 11'd1280, 22 H_FRONT = 11'd48, 23 H_SYNC = 11'd112, 24 H_BACK = 11'd248, 25 H_TOTAL = 11'd1688, 26 // Virtical Parameter( Line ) 27 V_DISP = 11'd1024, 28 V_FRONT = 11'd1, 29 V_SYNC = 11'd3, 30 V_BACK = 11'd38, 31 V_TOTAL = 11'd1066; 32 33 //调用IP核ALTPLL,像素频率108 MHZ 34 pll_pixel_clock pll_pixel_clock_inst ( 35 .inclk0 ( clk ), 36 .c0 ( clk_vga ) //例化端口必须是网线型 37 ); 38 39 //行同步计数器(信号发生器) 40 reg [10:0] hcnt; 41 reg hs_vga; 42 always @ (posedge clk_vga or negedge rst_n) 43 begin 44 if (!rst_n) 45 hcnt <= 0; //复位后计数清零 46 else 47 begin 48 if (hcnt < H_TOTAL - 1'b1) //判断扫描完一行,像素区间为[0, H_TOTAL - 1'b1] 49 hcnt <= hcnt + 1'b1; 50 else 51 hcnt <= 0; 52 end 53 end 54 //行同步 55 always @ (posedge clk_vga or negedge rst_n) 56 begin 57 if (!rst_n) 58 hs_vga <= 0; //因为复位后计数器置零,而0 ~ (H_DISP - 1)区间为显示区,此处必为 0 59 else 60 begin 61 //像素(H_DISP + H_FRONT - 1, H_DISP + H_FRONT + H_SYNC - 1]区间同步 62 if (hcnt >= (H_DISP + H_FRONT - 1'b1) && hcnt < (H_DISP + H_FRONT + H_SYNC - 1'b1)) 63 hs_vga <= 1; //在同步区置1,行同步 64 else 65 hs_vga <= 0; 66 end 67 end 68 69 //场同步计数器(信号发生器) 70 reg [10:0] vcnt; 71 reg vs_vga; 72 always @ (posedge clk_vga or negedge rst_n) //异步复位 73 begin 74 if (!rst_n) 75 vcnt <= 0; //复位后计数清零 76 else 77 begin 78 if (hcnt == H_DISP - 1'b1) //判断显示区扫面完一行,此处也可判断整个一行扫描完 79 begin 80 if (vcnt < V_TOTAL - 1'b1) //判断扫面完一场 81 vcnt <= vcnt + 1'b1; 82 else 83 vcnt <= 0; 84 end 85 else 86 vcnt <= vcnt; 87 end 88 end 89 //场同步 90 always @ (posedge clk_vga or negedge rst_n) 91 begin 92 if (!rst_n) 93 vs_vga <= 0; 94 else 95 begin 96 if (vcnt >= (V_DISP + V_FRONT - 1'b1) && vcnt < (V_DISP + V_FRONT + V_SYNC - 1'b1)) 97 vs_vga <= 1; 98 else 99 vs_vga <= 0; 100 end 101 end 102 103 //在显示期坐标根据显示的扫描而改变,在非显示期,坐标置零 104 wire [10:0] xpos_vga, ypos_vga; 105 assign xpos_vga = (hcnt < H_DISP) ? (hcnt + 1'b1) : 11'd0; //在显示区横坐标 + 1(即1~H_DISP) 106 assign ypos_vga = (vcnt < V_DISP) ? (vcnt + 1'b1) : 11'd0; //在显示区竖坐标 + 1(即1~V_DISP) 107 108 //竖彩条显示 109 always @ (posedge clk_vga or negedge rst_n) 110 if (!rst_n) 111 rgb_vga <= 3'b000; 112 else 113 begin 114 /*if (xpos_vga > 0 && xpos_vga < 80) rgb_vga <= 3'b010; 115 else if (xpos_vga < 160) rgb_vga <= 3'b011; 116 else if (xpos_vga < 240) rgb_vga <= 3'b100; 117 else if (xpos_vga < 320) rgb_vga <= 3'b101; 118 else if (xpos_vga < 400) rgb_vga <= 3'b110; 119 else if (xpos_vga < 480) rgb_vga <= 3'b111; 120 else if (xpos_vga < 560) rgb_vga <= 3'b001; 121 else if (xpos_vga < 640) rgb_vga <= 3'b010; 122 else if (xpos_vga < 720) rgb_vga <= 3'b011; 123 else if (xpos_vga < 800) rgb_vga <= 3'b100; 124 else if (xpos_vga < 880) rgb_vga <= 3'b101; 125 else if (xpos_vga < 960) rgb_vga <= 3'b110; 126 else if (xpos_vga < 1040) rgb_vga <= 3'b111; 127 else if (xpos_vga < 1120) rgb_vga <= 3'b001; 128 else if (xpos_vga < 1200) rgb_vga <= 3'b010; 129 else if (xpos_vga <= 1280) rgb_vga <= 3'b011; 130 else rgb_vga <= 3'b000;*/ 131 132 if (xpos_vga > 0 && xpos_vga <= 80) rgb_vga <= 3'b111;//white 133 else if (xpos_vga > 80 && xpos_vga <= 160) rgb_vga <= 3'b100;//red 134 else if (xpos_vga > 160 && xpos_vga <= 240) rgb_vga <= 3'b101;//mangenta 135 else if (xpos_vga > 240 && xpos_vga <= 320) rgb_vga <= 3'b110;//yellow 136 else if (xpos_vga > 320 && xpos_vga <= 400) rgb_vga <= 3'b010;//green 137 else if (xpos_vga > 400 && xpos_vga <= 480) rgb_vga <= 3'b001;//blue 138 else if (xpos_vga > 480 && xpos_vga <= 560) rgb_vga <= 3'b011;//cyan 139 else if (xpos_vga > 560 && xpos_vga <= 640) rgb_vga <= 3'b000; 140 141 else if (xpos_vga > 640 && xpos_vga <= 720) rgb_vga <= 3'b111;//white 142 else if (xpos_vga > 720 && xpos_vga <= 800) rgb_vga <= 3'b100; 143 else if (xpos_vga > 800 && xpos_vga <= 880) rgb_vga <= 3'b101; 144 else if (xpos_vga > 880 && xpos_vga <= 960) rgb_vga <= 3'b110; 145 else if (xpos_vga > 960 && xpos_vga <= 1040) rgb_vga <= 3'b010; 146 else if (xpos_vga > 1040 && xpos_vga <= 1120) rgb_vga <= 3'b001; 147 else if (xpos_vga > 1120 && xpos_vga <= 1200) rgb_vga <= 3'b011; 148 else if (xpos_vga > 1200 && xpos_vga <= 1280) rgb_vga <= 3'b111; 149 else rgb_vga <= 3'b000;//black,这个很重要,不然颜色不怎么正常 150 151 end 152 153 //三基色分离(可省,直接用 rgb_vga) 154 assign r_vga = rgb_vga[2]; 155 assign g_vga = rgb_vga[1]; 156 assign b_vga = rgb_vga[0]; 157 158 endmodule

调用的锁相环 IP 核 ALTPLL:

1 // megafunction wizard: %ALTPLL% 2 // GENERATION: STANDARD 3 // VERSION: WM1.0 4 // MODULE: altpll 5 6 // ============================================================ 7 // File Name: pll_pixel_clock.v 8 // Megafunction Name(s): 9 // altpll 10 // 11 // Simulation Library Files(s): 12 // altera_mf 13 // ============================================================ 14 // ************************************************************ 15 // THIS IS A WIZARD-GENERATED FILE. DO NOT EDIT THIS FILE! 16 // 17 // 12.1 Build 177 11/07/2012 SJ Full Version 18 // ************************************************************ 19 20 21 //Copyright (C) 1991-2012 Altera Corporation 22 //Your use of Altera Corporation's design tools, logic functions 23 //and other software and tools, and its AMPP partner logic 24 //functions, and any output files from any of the foregoing 25 //(including device programming or simulation files), and any 26 //associated documentation or information are expressly subject 27 //to the terms and conditions of the Altera Program License 28 //Subscription Agreement, Altera MegaCore Function License 29 //Agreement, or other applicable license agreement, including, 30 //without limitation, that your use is for the sole purpose of 31 //programming logic devices manufactured by Altera and sold by 32 //Altera or its authorized distributors. Please refer to the 33 //applicable agreement for further details. 34 35 36 // synopsys translate_off 37 `timescale 1 ps / 1 ps 38 // synopsys translate_on 39 module pll_pixel_clock ( 40 inclk0, 41 c0); 42 43 input inclk0; 44 output c0; 45 46 wire [4:0] sub_wire0; 47 wire [0:0] sub_wire4 = 1'h0; 48 wire [0:0] sub_wire1 = sub_wire0[0:0]; 49 wire c0 = sub_wire1; 50 wire sub_wire2 = inclk0; 51 wire [1:0] sub_wire3 = {sub_wire4, sub_wire2}; 52 53 altpll altpll_component ( 54 .inclk (sub_wire3), 55 .clk (sub_wire0), 56 .activeclock (), 57 .areset (1'b0), 58 .clkbad (), 59 .clkena ({6{1'b1}}), 60 .clkloss (), 61 .clkswitch (1'b0), 62 .configupdate (1'b0), 63 .enable0 (), 64 .enable1 (), 65 .extclk (), 66 .extclkena ({4{1'b1}}), 67 .fbin (1'b1), 68 .fbmimicbidir (), 69 .fbout (), 70 .fref (), 71 .icdrclk (), 72 .locked (), 73 .pfdena (1'b1), 74 .phasecounterselect ({4{1'b1}}), 75 .phasedone (), 76 .phasestep (1'b1), 77 .phaseupdown (1'b1), 78 .pllena (1'b1), 79 .scanaclr (1'b0), 80 .scanclk (1'b0), 81 .scanclkena (1'b1), 82 .scandata (1'b0), 83 .scandataout (), 84 .scandone (), 85 .scanread (1'b0), 86 .scanwrite (1'b0), 87 .sclkout0 (), 88 .sclkout1 (), 89 .vcooverrange (), 90 .vcounderrange ()); 91 defparam 92 altpll_component.bandwidth_type = "AUTO", 93 altpll_component.clk0_divide_by = 25, 94 altpll_component.clk0_duty_cycle = 50, 95 altpll_component.clk0_multiply_by = 54, 96 altpll_component.clk0_phase_shift = "0", 97 altpll_component.compensate_clock = "CLK0", 98 altpll_component.inclk0_input_frequency = 20000, 99 altpll_component.intended_device_family = "Cyclone IV E", 100 altpll_component.lpm_hint = "CBX_MODULE_PREFIX=pll_pixel_clock", 101 altpll_component.lpm_type = "altpll", 102 altpll_component.operation_mode = "NORMAL", 103 altpll_component.pll_type = "AUTO", 104 altpll_component.port_activeclock = "PORT_UNUSED", 105 altpll_component.port_areset = "PORT_UNUSED", 106 altpll_component.port_clkbad0 = "PORT_UNUSED", 107 altpll_component.port_clkbad1 = "PORT_UNUSED", 108 altpll_component.port_clkloss = "PORT_UNUSED", 109 altpll_component.port_clkswitch = "PORT_UNUSED", 110 altpll_component.port_configupdate = "PORT_UNUSED", 111 altpll_component.port_fbin = "PORT_UNUSED", 112 altpll_component.port_inclk0 = "PORT_USED", 113 altpll_component.port_inclk1 = "PORT_UNUSED", 114 altpll_component.port_locked = "PORT_UNUSED", 115 altpll_component.port_pfdena = "PORT_UNUSED", 116 altpll_component.port_phasecounterselect = "PORT_UNUSED", 117 altpll_component.port_phasedone = "PORT_UNUSED", 118 altpll_component.port_phasestep = "PORT_UNUSED", 119 altpll_component.port_phaseupdown = "PORT_UNUSED", 120 altpll_component.port_pllena = "PORT_UNUSED", 121 altpll_component.port_scanaclr = "PORT_UNUSED", 122 altpll_component.port_scanclk = "PORT_UNUSED", 123 altpll_component.port_scanclkena = "PORT_UNUSED", 124 altpll_component.port_scandata = "PORT_UNUSED", 125 altpll_component.port_scandataout = "PORT_UNUSED", 126 altpll_component.port_scandone = "PORT_UNUSED", 127 altpll_component.port_scanread = "PORT_UNUSED", 128 altpll_component.port_scanwrite = "PORT_UNUSED", 129 altpll_component.port_clk0 = "PORT_USED", 130 altpll_component.port_clk1 = "PORT_UNUSED", 131 altpll_component.port_clk2 = "PORT_UNUSED", 132 altpll_component.port_clk3 = "PORT_UNUSED", 133 altpll_component.port_clk4 = "PORT_UNUSED", 134 altpll_component.port_clk5 = "PORT_UNUSED", 135 altpll_component.port_clkena0 = "PORT_UNUSED", 136 altpll_component.port_clkena1 = "PORT_UNUSED", 137 altpll_component.port_clkena2 = "PORT_UNUSED", 138 altpll_component.port_clkena3 = "PORT_UNUSED", 139 altpll_component.port_clkena4 = "PORT_UNUSED", 140 altpll_component.port_clkena5 = "PORT_UNUSED", 141 altpll_component.port_extclk0 = "PORT_UNUSED", 142 altpll_component.port_extclk1 = "PORT_UNUSED", 143 altpll_component.port_extclk2 = "PORT_UNUSED", 144 altpll_component.port_extclk3 = "PORT_UNUSED", 145 altpll_component.width_clock = 5; 146 147 148 endmodule 149 150 // ============================================================ 151 // CNX file retrieval info 152 // ============================================================ 153 // Retrieval info: PRIVATE: ACTIVECLK_CHECK STRING "0" 154 // Retrieval info: PRIVATE: BANDWIDTH STRING "1.000" 155 // Retrieval info: PRIVATE: BANDWIDTH_FEATURE_ENABLED STRING "1" 156 // Retrieval info: PRIVATE: BANDWIDTH_FREQ_UNIT STRING "MHz" 157 // Retrieval info: PRIVATE: BANDWIDTH_PRESET STRING "Low" 158 // Retrieval info: PRIVATE: BANDWIDTH_USE_AUTO STRING "1" 159 // Retrieval info: PRIVATE: BANDWIDTH_USE_PRESET STRING "0" 160 // Retrieval info: PRIVATE: CLKBAD_SWITCHOVER_CHECK STRING "0" 161 // Retrieval info: PRIVATE: CLKLOSS_CHECK STRING "0" 162 // Retrieval info: PRIVATE: CLKSWITCH_CHECK STRING "0" 163 // Retrieval info: PRIVATE: CNX_NO_COMPENSATE_RADIO STRING "0" 164 // Retrieval info: PRIVATE: CREATE_CLKBAD_CHECK STRING "0" 165 // Retrieval info: PRIVATE: CREATE_INCLK1_CHECK STRING "0" 166 // Retrieval info: PRIVATE: CUR_DEDICATED_CLK STRING "c0" 167 // Retrieval info: PRIVATE: CUR_FBIN_CLK STRING "c0" 168 // Retrieval info: PRIVATE: DEVICE_SPEED_GRADE STRING "8" 169 // Retrieval info: PRIVATE: DIV_FACTOR0 NUMERIC "1" 170 // Retrieval info: PRIVATE: DUTY_CYCLE0 STRING "50.00000000" 171 // Retrieval info: PRIVATE: EFF_OUTPUT_FREQ_VALUE0 STRING "108.000000" 172 // Retrieval info: PRIVATE: EXPLICIT_SWITCHOVER_COUNTER STRING "0" 173 // Retrieval info: PRIVATE: EXT_FEEDBACK_RADIO STRING "0" 174 // Retrieval info: PRIVATE: GLOCKED_COUNTER_EDIT_CHANGED STRING "1" 175 // Retrieval info: PRIVATE: GLOCKED_FEATURE_ENABLED STRING "0" 176 // Retrieval info: PRIVATE: GLOCKED_MODE_CHECK STRING "0" 177 // Retrieval info: PRIVATE: GLOCK_COUNTER_EDIT NUMERIC "1048575" 178 // Retrieval info: PRIVATE: HAS_MANUAL_SWITCHOVER STRING "1" 179 // Retrieval info: PRIVATE: INCLK0_FREQ_EDIT STRING "50.000" 180 // Retrieval info: PRIVATE: INCLK0_FREQ_UNIT_COMBO STRING "MHz" 181 // Retrieval info: PRIVATE: INCLK1_FREQ_EDIT STRING "100.000" 182 // Retrieval info: PRIVATE: INCLK1_FREQ_EDIT_CHANGED STRING "1" 183 // Retrieval info: PRIVATE: INCLK1_FREQ_UNIT_CHANGED STRING "1" 184 // Retrieval info: PRIVATE: INCLK1_FREQ_UNIT_COMBO STRING "MHz" 185 // Retrieval info: PRIVATE: INTENDED_DEVICE_FAMILY STRING "Cyclone IV E" 186 // Retrieval info: PRIVATE: INT_FEEDBACK__MODE_RADIO STRING "1" 187 // Retrieval info: PRIVATE: LOCKED_OUTPUT_CHECK STRING "0" 188 // Retrieval info: PRIVATE: LONG_SCAN_RADIO STRING "1" 189 // Retrieval info: PRIVATE: LVDS_MODE_DATA_RATE STRING "Not Available" 190 // Retrieval info: PRIVATE: LVDS_MODE_DATA_RATE_DIRTY NUMERIC "0" 191 // Retrieval info: PRIVATE: LVDS_PHASE_SHIFT_UNIT0 STRING "deg" 192 // Retrieval info: PRIVATE: MIG_DEVICE_SPEED_GRADE STRING "Any" 193 // Retrieval info: PRIVATE: MIRROR_CLK0 STRING "0" 194 // Retrieval info: PRIVATE: MULT_FACTOR0 NUMERIC "1" 195 // Retrieval info: PRIVATE: NORMAL_MODE_RADIO STRING "1" 196 // Retrieval info: PRIVATE: OUTPUT_FREQ0 STRING "108.00000000" 197 // Retrieval info: PRIVATE: OUTPUT_FREQ_MODE0 STRING "1" 198 // Retrieval info: PRIVATE: OUTPUT_FREQ_UNIT0 STRING "MHz" 199 // Retrieval info: PRIVATE: PHASE_RECONFIG_FEATURE_ENABLED STRING "1" 200 // Retrieval info: PRIVATE: PHASE_RECONFIG_INPUTS_CHECK STRING "0" 201 // Retrieval info: PRIVATE: PHASE_SHIFT0 STRING "0.00000000" 202 // Retrieval info: PRIVATE: PHASE_SHIFT_STEP_ENABLED_CHECK STRING "0" 203 // Retrieval info: PRIVATE: PHASE_SHIFT_UNIT0 STRING "deg" 204 // Retrieval info: PRIVATE: PLL_ADVANCED_PARAM_CHECK STRING "0" 205 // Retrieval info: PRIVATE: PLL_ARESET_CHECK STRING "0" 206 // Retrieval info: PRIVATE: PLL_AUTOPLL_CHECK NUMERIC "1" 207 // Retrieval info: PRIVATE: PLL_ENHPLL_CHECK NUMERIC "0" 208 // Retrieval info: PRIVATE: PLL_FASTPLL_CHECK NUMERIC "0" 209 // Retrieval info: PRIVATE: PLL_FBMIMIC_CHECK STRING "0" 210 // Retrieval info: PRIVATE: PLL_LVDS_PLL_CHECK NUMERIC "0" 211 // Retrieval info: PRIVATE: PLL_PFDENA_CHECK STRING "0" 212 // Retrieval info: PRIVATE: PLL_TARGET_HARCOPY_CHECK NUMERIC "0" 213 // Retrieval info: PRIVATE: PRIMARY_CLK_COMBO STRING "inclk0" 214 // Retrieval info: PRIVATE: RECONFIG_FILE STRING "pll_pixel_clock.mif" 215 // Retrieval info: PRIVATE: SACN_INPUTS_CHECK STRING "0" 216 // Retrieval info: PRIVATE: SCAN_FEATURE_ENABLED STRING "1" 217 // Retrieval info: PRIVATE: SELF_RESET_LOCK_LOSS STRING "0" 218 // Retrieval info: PRIVATE: SHORT_SCAN_RADIO STRING "0" 219 // Retrieval info: PRIVATE: SPREAD_FEATURE_ENABLED STRING "0" 220 // Retrieval info: PRIVATE: SPREAD_FREQ STRING "50.000" 221 // Retrieval info: PRIVATE: SPREAD_FREQ_UNIT STRING "KHz" 222 // Retrieval info: PRIVATE: SPREAD_PERCENT STRING "0.500" 223 // Retrieval info: PRIVATE: SPREAD_USE STRING "0" 224 // Retrieval info: PRIVATE: SRC_SYNCH_COMP_RADIO STRING "0" 225 // Retrieval info: PRIVATE: STICKY_CLK0 STRING "1" 226 // Retrieval info: PRIVATE: SWITCHOVER_COUNT_EDIT NUMERIC "1" 227 // Retrieval info: PRIVATE: SWITCHOVER_FEATURE_ENABLED STRING "1" 228 // Retrieval info: PRIVATE: SYNTH_WRAPPER_GEN_POSTFIX STRING "0" 229 // Retrieval info: PRIVATE: USE_CLK0 STRING "1" 230 // Retrieval info: PRIVATE: USE_CLKENA0 STRING "0" 231 // Retrieval info: PRIVATE: USE_MIL_SPEED_GRADE NUMERIC "0" 232 // Retrieval info: PRIVATE: ZERO_DELAY_RADIO STRING "0" 233 // Retrieval info: LIBRARY: altera_mf altera_mf.altera_mf_components.all 234 // Retrieval info: CONSTANT: BANDWIDTH_TYPE STRING "AUTO" 235 // Retrieval info: CONSTANT: CLK0_DIVIDE_BY NUMERIC "25" 236 // Retrieval info: CONSTANT: CLK0_DUTY_CYCLE NUMERIC "50" 237 // Retrieval info: CONSTANT: CLK0_MULTIPLY_BY NUMERIC "54" 238 // Retrieval info: CONSTANT: CLK0_PHASE_SHIFT STRING "0" 239 // Retrieval info: CONSTANT: COMPENSATE_CLOCK STRING "CLK0" 240 // Retrieval info: CONSTANT: INCLK0_INPUT_FREQUENCY NUMERIC "20000" 241 // Retrieval info: CONSTANT: INTENDED_DEVICE_FAMILY STRING "Cyclone IV E" 242 // Retrieval info: CONSTANT: LPM_TYPE STRING "altpll" 243 // Retrieval info: CONSTANT: OPERATION_MODE STRING "NORMAL" 244 // Retrieval info: CONSTANT: PLL_TYPE STRING "AUTO" 245 // Retrieval info: CONSTANT: PORT_ACTIVECLOCK STRING "PORT_UNUSED" 246 // Retrieval info: CONSTANT: PORT_ARESET STRING "PORT_UNUSED" 247 // Retrieval info: CONSTANT: PORT_CLKBAD0 STRING "PORT_UNUSED" 248 // Retrieval info: CONSTANT: PORT_CLKBAD1 STRING "PORT_UNUSED" 249 // Retrieval info: CONSTANT: PORT_CLKLOSS STRING "PORT_UNUSED" 250 // Retrieval info: CONSTANT: PORT_CLKSWITCH STRING "PORT_UNUSED" 251 // Retrieval info: CONSTANT: PORT_CONFIGUPDATE STRING "PORT_UNUSED" 252 // Retrieval info: CONSTANT: PORT_FBIN STRING "PORT_UNUSED" 253 // Retrieval info: CONSTANT: PORT_INCLK0 STRING "PORT_USED" 254 // Retrieval info: CONSTANT: PORT_INCLK1 STRING "PORT_UNUSED" 255 // Retrieval info: CONSTANT: PORT_LOCKED STRING "PORT_UNUSED" 256 // Retrieval info: CONSTANT: PORT_PFDENA STRING "PORT_UNUSED" 257 // Retrieval info: CONSTANT: PORT_PHASECOUNTERSELECT STRING "PORT_UNUSED" 258 // Retrieval info: CONSTANT: PORT_PHASEDONE STRING "PORT_UNUSED" 259 // Retrieval info: CONSTANT: PORT_PHASESTEP STRING "PORT_UNUSED" 260 // Retrieval info: CONSTANT: PORT_PHASEUPDOWN STRING "PORT_UNUSED" 261 // Retrieval info: CONSTANT: PORT_PLLENA STRING "PORT_UNUSED" 262 // Retrieval info: CONSTANT: PORT_SCANACLR STRING "PORT_UNUSED" 263 // Retrieval info: CONSTANT: PORT_SCANCLK STRING "PORT_UNUSED" 264 // Retrieval info: CONSTANT: PORT_SCANCLKENA STRING "PORT_UNUSED" 265 // Retrieval info: CONSTANT: PORT_SCANDATA STRING "PORT_UNUSED" 266 // Retrieval info: CONSTANT: PORT_SCANDATAOUT STRING "PORT_UNUSED" 267 // Retrieval info: CONSTANT: PORT_SCANDONE STRING "PORT_UNUSED" 268 // Retrieval info: CONSTANT: PORT_SCANREAD STRING "PORT_UNUSED" 269 // Retrieval info: CONSTANT: PORT_SCANWRITE STRING "PORT_UNUSED" 270 // Retrieval info: CONSTANT: PORT_clk0 STRING "PORT_USED" 271 // Retrieval info: CONSTANT: PORT_clk1 STRING "PORT_UNUSED" 272 // Retrieval info: CONSTANT: PORT_clk2 STRING "PORT_UNUSED" 273 // Retrieval info: CONSTANT: PORT_clk3 STRING "PORT_UNUSED" 274 // Retrieval info: CONSTANT: PORT_clk4 STRING "PORT_UNUSED" 275 // Retrieval info: CONSTANT: PORT_clk5 STRING "PORT_UNUSED" 276 // Retrieval info: CONSTANT: PORT_clkena0 STRING "PORT_UNUSED" 277 // Retrieval info: CONSTANT: PORT_clkena1 STRING "PORT_UNUSED" 278 // Retrieval info: CONSTANT: PORT_clkena2 STRING "PORT_UNUSED" 279 // Retrieval info: CONSTANT: PORT_clkena3 STRING "PORT_UNUSED" 280 // Retrieval info: CONSTANT: PORT_clkena4 STRING "PORT_UNUSED" 281 // Retrieval info: CONSTANT: PORT_clkena5 STRING "PORT_UNUSED" 282 // Retrieval info: CONSTANT: PORT_extclk0 STRING "PORT_UNUSED" 283 // Retrieval info: CONSTANT: PORT_extclk1 STRING "PORT_UNUSED" 284 // Retrieval info: CONSTANT: PORT_extclk2 STRING "PORT_UNUSED" 285 // Retrieval info: CONSTANT: PORT_extclk3 STRING "PORT_UNUSED" 286 // Retrieval info: CONSTANT: WIDTH_CLOCK NUMERIC "5" 287 // Retrieval info: USED_PORT: @clk 0 0 5 0 OUTPUT_CLK_EXT VCC "@clk[4..0]" 288 // Retrieval info: USED_PORT: c0 0 0 0 0 OUTPUT_CLK_EXT VCC "c0" 289 // Retrieval info: USED_PORT: inclk0 0 0 0 0 INPUT_CLK_EXT GND "inclk0" 290 // Retrieval info: CONNECT: @inclk 0 0 1 1 GND 0 0 0 0 291 // Retrieval info: CONNECT: @inclk 0 0 1 0 inclk0 0 0 0 0 292 // Retrieval info: CONNECT: c0 0 0 0 0 @clk 0 0 1 0 293 // Retrieval info: GEN_FILE: TYPE_NORMAL pll_pixel_clock.v TRUE 294 // Retrieval info: GEN_FILE: TYPE_NORMAL pll_pixel_clock.ppf TRUE 295 // Retrieval info: GEN_FILE: TYPE_NORMAL pll_pixel_clock.inc FALSE 296 // Retrieval info: GEN_FILE: TYPE_NORMAL pll_pixel_clock.cmp FALSE 297 // Retrieval info: GEN_FILE: TYPE_NORMAL pll_pixel_clock.bsf FALSE 298 // Retrieval info: GEN_FILE: TYPE_NORMAL pll_pixel_clock_inst.v TRUE 299 // Retrieval info: GEN_FILE: TYPE_NORMAL pll_pixel_clock_bb.v FALSE 300 // Retrieval info: LIB_FILE: altera_mf 301 // Retrieval info: CBX_MODULE_PREFIX: ON

【注】:

①对时序部分代码的编写不论从哪个时期作为判断依据都无所谓,这是一个周期性循环的。后面附另一种判断的写法,其实都一样。

②尽管使用的是LCD而不是CRT,消隐前后期必须保留,若令 H_FRONT、H_BACK、V_FRONT、V_BACK 为零,显示器将不能显示,亲测。

③尽量按照工业标准来写,这样兼容性更强。

RTL:

Technology Map:

Modelsim 仿真

写一个简单的 testbench:

1 `timescale 10 ns/ 1 ps 2 module VGA_color_line_vlg_tst(); 3 reg clk; 4 reg rst_n; 5 // wires 6 wire b_vga; 7 wire g_vga; 8 wire hs_vga; 9 wire r_vga; 10 wire vs_vga; 11 12 VGA_color_line i1 ( 13 .b_vga(b_vga), 14 .clk(clk), 15 .g_vga(g_vga), 16 .hs_vga(hs_vga), 17 .r_vga(r_vga), 18 .rst_n(rst_n), 19 .vs_vga(vs_vga) 20 ); 21 initial 22 begin 23 clk = 0; 24 end 25 always 26 begin 27 #1 clk = ~clk; 28 end 29 endmodule

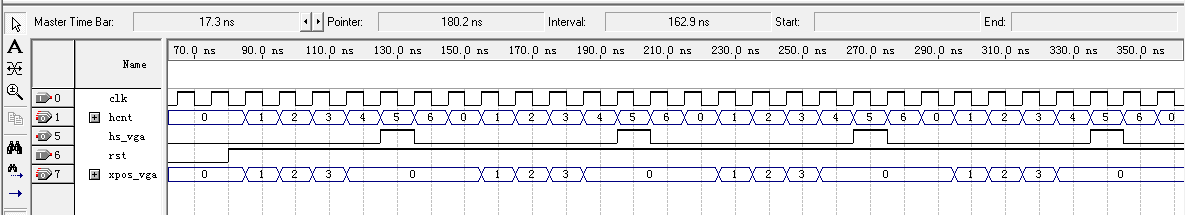

仿真波形:

可以看出波形正常。

2017-07-22--------------------------------------------------------------------------------------------------------------↓↓↓

对于VGA时序里 hcnt、xpos_vga、hs_vga 等随时钟变化存疑,故手动仿真如下:

我们假设 H_DISP = 4, H_BACK = 1, H_SYNC = 1, H_FRONT = 1, H_TOTAL = 7。

由此用 quartus ii 9.0 自带仿真工具测试一下:

1 module VGA_color_line_test (clk, rst, xpos_vga, hcnt, hs_vga); 2 input clk, rst; 3 output hcnt, hs_vga; 4 output [2:0] xpos_vga; 5 6 reg [2:0] hcnt; 7 reg hs_vga; 8 wire [2:0] xpos_vga; 9 10 parameter 11 H_DISP = 3'd4, 12 H_FRONT = 3'd1, 13 H_SYNC = 3'd1, 14 H_BACK = 3'd1, 15 H_TOTAL = 3'd7; 16 17 always @(posedge clk or negedge rst) begin 18 if (!rst) 19 hs_vga <= 0; 20 else 21 if (hcnt >= H_DISP + H_FRONT - 1 && hcnt < H_DISP + H_FRONT + H_SYNC - 1) 22 hs_vga <= 1; 23 else 24 hs_vga <= 0; 25 end 26 27 always @(posedge clk or negedge rst) begin 28 if (!rst) 29 hcnt <= 0; 30 else 31 if (hcnt < H_TOTAL - 1) 32 hcnt <= hcnt + 1; 33 else 34 hcnt <= 0; 35 end 36 37 assign xpos_vga = (hcnt < H_DISP) ? hcnt : 0; 38 39 endmodule

从仿真波形可以看出手动分析完全正确。则原代码中 105 和 106 行 assign语句中不应该加 1。

(assign xpos_vga = (hcnt < H_DISP) ? hcnt : 11'd0; 即可,ypos_vga同理)

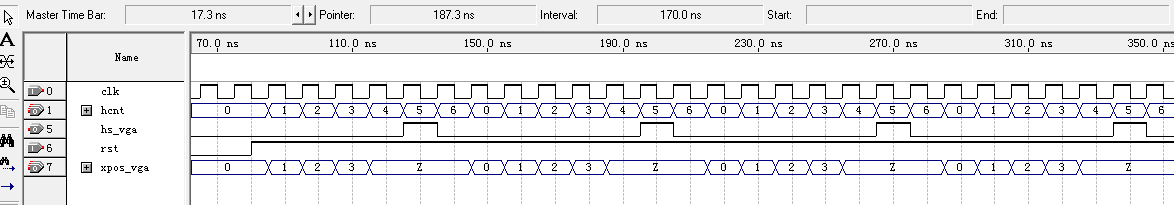

由此能得出在非显示区坐标为 0,那 0 坐标点在非显示期会不会出现异常呢,我把非显示期改为 11'dz 也能正常显示,但是这样好吗??? (希望大神们给点提示^_^)

改为11'dz 仿真波形如下:

2017-07-22--------------------------------------------------------------------------------------------------------------↑↑↑

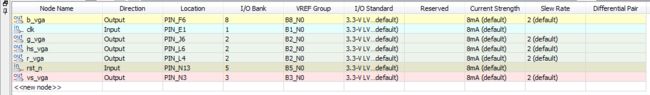

硬件实测

硬件采用:Cyclone IV E(EP4CE6F17C8)

引脚分配:

实际效果:

上面的是比较完善的,下面粘贴第一个版本代码,能显示,稍有瑕疵,程序中有些细节可能有问题,懒得改了,直接粘贴

顶层文件:

1 module VGA_display_easy (clk, rst_n, hs_vga, vs_vga, r_vga, g_vga, b_vga); 2 3 input clk, rst_n; 4 output hs_vga, vs_vga; 5 output r_vga, g_vga , b_vga; 6 reg [2:0] rgb_vga; 7 8 9 // VGA_1280_1024_60fps_50MHz 10 // Horizontal Parameter( Pixel ) 11 parameter 12 H_DISP = 11'd1280, 13 H_FRONT = 11'd48, 14 H_SYNC = 11'd112, 15 H_BACK = 11'd248, 16 H_TOTAL = 11'd1688, 17 // Virtical Parameter( Line ) 18 V_DISP = 11'd1024, 19 V_FRONT = 11'd1, 20 V_SYNC = 11'd3, 21 V_BACK = 11'd38, 22 V_TOTAL = 11'd1066; 23 24 //PLL 25 /*pll_vga pll_vga_inst ( 26 .areset ( ~rst_n ), 27 .inclk0 ( clk ), 28 .c0 ( clk_vga ), 29 .locked ( locked_sig ) 30 );*/ 31 ceshi ceshi_inst ( 32 .inclk0 ( clk ), 33 .c0 ( clk_vga ) 34 ); 35 wire clk_vga; 36 37 //行同步信号发生器 38 reg [10:0] hcnt; 39 reg hs_vga; 40 always @ (posedge clk_vga or negedge rst_n) 41 begin 42 if (!rst_n) 43 hcnt <= 1; // hcnt <= 0; 44 else 45 begin 46 if (hcnt <= H_TOTAL ) // if (hcnt < H_TOTAL - 1'b1) 47 hcnt <= hcnt + 1'b1; 48 else 49 hcnt <= 1; //hcnt <= 0; 50 end 51 end 52 53 always @ (posedge clk_vga or negedge rst_n) 54 begin 55 if (!rst_n) 56 hs_vga <= 1; 57 else 58 begin 59 if (hcnt <= H_SYNC) 60 hs_vga <= 1; 61 //if ((hcnt >= H_DISP + H_FRONT - 1'b1) && (hcnt < H_DISP + H_FRONT + H_SYNC - 1'b1)) 62 //hs_vga <= 0; 63 else 64 hs_vga <= 0; 65 //hs_vga <= 1; 66 end 67 end 68 69 //场同步信号发生器 70 reg [10:0] vcnt; 71 reg vs_vga; 72 always @ (posedge clk_vga or negedge rst_n) 73 begin 74 if (!rst_n) 75 vcnt <= 0; 76 else 77 begin 78 if (vcnt <= V_TOTAL) 79 begin 80 if (hcnt == H_TOTAL) 81 vcnt <= vcnt + 1'b1; 82 else 83 vcnt <= vcnt; 84 end 85 else 86 vcnt <= 1; 87 88 /*if (hcnt == H_DISP - 1) 89 begin 90 if (vcnt < V_TOTAL - 1'b1) 91 vcnt <= vcnt + 1'b1; 92 else 93 vcnt <= 0; 94 end 95 else 96 vcnt <= vcnt;*/ 97 end 98 end 99 100 always @ (posedge clk_vga or negedge rst_n) 101 begin 102 if (!rst_n) 103 vs_vga <= 1; 104 else 105 begin 106 if (vcnt <= V_SYNC) 107 //if ((vcnt >= V_DISP + V_FRONT - 1'b1) && (vcnt < V_DISP + V_FRONT + V_SYNC - 1'b1)) 108 vs_vga <= 1; 109 //vs_vga <= 0; 110 else 111 vs_vga <= 0; 112 //vs_vga <= 1; 113 end 114 end 115 116 //显示期坐标,非显示期,坐标置零。 117 wire [10:0] xpos_vga, ypos_vga; 118 assign xpos_vga = (hcnt > H_SYNC + H_BACK && hcnt <= H_SYNC + H_BACK + H_DISP) ? (hcnt - H_SYNC - H_BACK) : 11'd0; 119 assign ypos_vga = (vcnt > V_SYNC + V_BACK && vcnt <= V_SYNC + V_BACK + V_DISP) ? (vcnt - V_SYNC - V_BACK) : 11'd0; 120 //assign xpos_vga = (hcnt < H_DISP) ? (hcnt + 1'b1) : 11'd0; 121 //assign ypos_vga = (vcnt < V_DISP) ? (vcnt + 1'b1) : 11'd0; 122 123 // 124 always @ (posedge clk_vga or negedge rst_n) 125 if (!rst_n) 126 rgb_vga <= 3'b000; 127 else /*if ((xpos_vga >= 200) && (xpos_vga<=220) && (ypos_vga >= 140) && (ypos_vga <= 460)) 128 rgb_vga <= 3'b100; 129 else if ((xpos_vga >= 580) && (xpos_vga<=600) && (ypos_vga >= 140) && (ypos_vga <= 460)) 130 rgb_vga <= 3'b010; 131 else if ((xpos_vga >= 220) && (xpos_vga<=580) && (ypos_vga >= 140) && (ypos_vga <= 160)) 132 rgb_vga <= 3'b001; 133 else if ((xpos_vga >= 220) && (xpos_vga<=580) && (ypos_vga >= 440) && (ypos_vga <= 460)) 134 rgb_vga <= 3'b110; 135 else rgb_vga <= 3'b000;*/ 136 begin 137 if (xpos_vga > 0 && xpos_vga <= 80) rgb_vga <= 3'b111;//white 138 else if (xpos_vga > 80 && xpos_vga <= 160) rgb_vga <= 3'b100;//red 139 else if (xpos_vga > 160 && xpos_vga <= 240) rgb_vga <= 3'b101;//mangenta 140 else if (xpos_vga > 240 && xpos_vga <= 320) rgb_vga <= 3'b110;//yellow 141 else if (xpos_vga > 320 && xpos_vga <= 400) rgb_vga <= 3'b010;//green 142 else if (xpos_vga > 400 && xpos_vga <= 480) rgb_vga <= 3'b001;//blue 143 else if (xpos_vga > 480 && xpos_vga <= 560) rgb_vga <= 3'b011;//cyan 144 else if (xpos_vga > 560 && xpos_vga <= 640) rgb_vga <= 3'b000; 145 146 else if (xpos_vga > 640 && xpos_vga <= 720) rgb_vga <= 3'b111;//white 147 else if (xpos_vga > 720 && xpos_vga <= 800) rgb_vga <= 3'b100; 148 else if (xpos_vga > 800 && xpos_vga <= 880) rgb_vga <= 3'b101; 149 else if (xpos_vga > 880 && xpos_vga <= 960) rgb_vga <= 3'b110; 150 else if (xpos_vga > 960 && xpos_vga <= 1040) rgb_vga <= 3'b010; 151 else if (xpos_vga > 1040 && xpos_vga <= 1120) rgb_vga <= 3'b001; 152 else if (xpos_vga > 1120 && xpos_vga <= 1200) rgb_vga <= 3'b011; 153 else if (xpos_vga > 1200 && xpos_vga <= 1280) rgb_vga <= 3'b111; 154 else rgb_vga <= 3'b000;//black 155 156 end 157 158 assign r_vga = rgb_vga[2]; 159 assign g_vga = rgb_vga[1]; 160 assign b_vga = rgb_vga[0]; 161 162 endmodule

pll :

1 // megafunction wizard: %ALTPLL% 2 // GENERATION: STANDARD 3 // VERSION: WM1.0 4 // MODULE: altpll 5 6 // ============================================================ 7 // File Name: ceshi.v 8 // Megafunction Name(s): 9 // altpll 10 // 11 // Simulation Library Files(s): 12 // altera_mf 13 // ============================================================ 14 // ************************************************************ 15 // THIS IS A WIZARD-GENERATED FILE. DO NOT EDIT THIS FILE! 16 // 17 // 12.1 Build 177 11/07/2012 SJ Full Version 18 // ************************************************************ 19 20 21 //Copyright (C) 1991-2012 Altera Corporation 22 //Your use of Altera Corporation's design tools, logic functions 23 //and other software and tools, and its AMPP partner logic 24 //functions, and any output files from any of the foregoing 25 //(including device programming or simulation files), and any 26 //associated documentation or information are expressly subject 27 //to the terms and conditions of the Altera Program License 28 //Subscription Agreement, Altera MegaCore Function License 29 //Agreement, or other applicable license agreement, including, 30 //without limitation, that your use is for the sole purpose of 31 //programming logic devices manufactured by Altera and sold by 32 //Altera or its authorized distributors. Please refer to the 33 //applicable agreement for further details. 34 35 36 // synopsys translate_off 37 `timescale 1 ps / 1 ps 38 // synopsys translate_on 39 module ceshi ( 40 inclk0, 41 c0); 42 43 input inclk0; 44 output c0; 45 46 wire [4:0] sub_wire0; 47 wire [0:0] sub_wire4 = 1'h0; 48 wire [0:0] sub_wire1 = sub_wire0[0:0]; 49 wire c0 = sub_wire1; 50 wire sub_wire2 = inclk0; 51 wire [1:0] sub_wire3 = {sub_wire4, sub_wire2}; 52 53 altpll altpll_component ( 54 .inclk (sub_wire3), 55 .clk (sub_wire0), 56 .activeclock (), 57 .areset (1'b0), 58 .clkbad (), 59 .clkena ({6{1'b1}}), 60 .clkloss (), 61 .clkswitch (1'b0), 62 .configupdate (1'b0), 63 .enable0 (), 64 .enable1 (), 65 .extclk (), 66 .extclkena ({4{1'b1}}), 67 .fbin (1'b1), 68 .fbmimicbidir (), 69 .fbout (), 70 .fref (), 71 .icdrclk (), 72 .locked (), 73 .pfdena (1'b1), 74 .phasecounterselect ({4{1'b1}}), 75 .phasedone (), 76 .phasestep (1'b1), 77 .phaseupdown (1'b1), 78 .pllena (1'b1), 79 .scanaclr (1'b0), 80 .scanclk (1'b0), 81 .scanclkena (1'b1), 82 .scandata (1'b0), 83 .scandataout (), 84 .scandone (), 85 .scanread (1'b0), 86 .scanwrite (1'b0), 87 .sclkout0 (), 88 .sclkout1 (), 89 .vcooverrange (), 90 .vcounderrange ()); 91 defparam 92 altpll_component.bandwidth_type = "AUTO", 93 altpll_component.clk0_divide_by = 156250, 94 altpll_component.clk0_duty_cycle = 50, 95 altpll_component.clk0_multiply_by = 337389, 96 altpll_component.clk0_phase_shift = "0", 97 altpll_component.compensate_clock = "CLK0", 98 altpll_component.inclk0_input_frequency = 20000, 99 altpll_component.intended_device_family = "Cyclone IV E", 100 altpll_component.lpm_hint = "CBX_MODULE_PREFIX=ceshi", 101 altpll_component.lpm_type = "altpll", 102 altpll_component.operation_mode = "NORMAL", 103 altpll_component.pll_type = "AUTO", 104 altpll_component.port_activeclock = "PORT_UNUSED", 105 altpll_component.port_areset = "PORT_UNUSED", 106 altpll_component.port_clkbad0 = "PORT_UNUSED", 107 altpll_component.port_clkbad1 = "PORT_UNUSED", 108 altpll_component.port_clkloss = "PORT_UNUSED", 109 altpll_component.port_clkswitch = "PORT_UNUSED", 110 altpll_component.port_configupdate = "PORT_UNUSED", 111 altpll_component.port_fbin = "PORT_UNUSED", 112 altpll_component.port_inclk0 = "PORT_USED", 113 altpll_component.port_inclk1 = "PORT_UNUSED", 114 altpll_component.port_locked = "PORT_UNUSED", 115 altpll_component.port_pfdena = "PORT_UNUSED", 116 altpll_component.port_phasecounterselect = "PORT_UNUSED", 117 altpll_component.port_phasedone = "PORT_UNUSED", 118 altpll_component.port_phasestep = "PORT_UNUSED", 119 altpll_component.port_phaseupdown = "PORT_UNUSED", 120 altpll_component.port_pllena = "PORT_UNUSED", 121 altpll_component.port_scanaclr = "PORT_UNUSED", 122 altpll_component.port_scanclk = "PORT_UNUSED", 123 altpll_component.port_scanclkena = "PORT_UNUSED", 124 altpll_component.port_scandata = "PORT_UNUSED", 125 altpll_component.port_scandataout = "PORT_UNUSED", 126 altpll_component.port_scandone = "PORT_UNUSED", 127 altpll_component.port_scanread = "PORT_UNUSED", 128 altpll_component.port_scanwrite = "PORT_UNUSED", 129 altpll_component.port_clk0 = "PORT_USED", 130 altpll_component.port_clk1 = "PORT_UNUSED", 131 altpll_component.port_clk2 = "PORT_UNUSED", 132 altpll_component.port_clk3 = "PORT_UNUSED", 133 altpll_component.port_clk4 = "PORT_UNUSED", 134 altpll_component.port_clk5 = "PORT_UNUSED", 135 altpll_component.port_clkena0 = "PORT_UNUSED", 136 altpll_component.port_clkena1 = "PORT_UNUSED", 137 altpll_component.port_clkena2 = "PORT_UNUSED", 138 altpll_component.port_clkena3 = "PORT_UNUSED", 139 altpll_component.port_clkena4 = "PORT_UNUSED", 140 altpll_component.port_clkena5 = "PORT_UNUSED", 141 altpll_component.port_extclk0 = "PORT_UNUSED", 142 altpll_component.port_extclk1 = "PORT_UNUSED", 143 altpll_component.port_extclk2 = "PORT_UNUSED", 144 altpll_component.port_extclk3 = "PORT_UNUSED", 145 altpll_component.width_clock = 5; 146 147 148 endmodule 149 150 // ============================================================ 151 // CNX file retrieval info 152 // ============================================================ 153 // Retrieval info: PRIVATE: ACTIVECLK_CHECK STRING "0" 154 // Retrieval info: PRIVATE: BANDWIDTH STRING "1.000" 155 // Retrieval info: PRIVATE: BANDWIDTH_FEATURE_ENABLED STRING "1" 156 // Retrieval info: PRIVATE: BANDWIDTH_FREQ_UNIT STRING "MHz" 157 // Retrieval info: PRIVATE: BANDWIDTH_PRESET STRING "Low" 158 // Retrieval info: PRIVATE: BANDWIDTH_USE_AUTO STRING "1" 159 // Retrieval info: PRIVATE: BANDWIDTH_USE_PRESET STRING "0" 160 // Retrieval info: PRIVATE: CLKBAD_SWITCHOVER_CHECK STRING "0" 161 // Retrieval info: PRIVATE: CLKLOSS_CHECK STRING "0" 162 // Retrieval info: PRIVATE: CLKSWITCH_CHECK STRING "0" 163 // Retrieval info: PRIVATE: CNX_NO_COMPENSATE_RADIO STRING "0" 164 // Retrieval info: PRIVATE: CREATE_CLKBAD_CHECK STRING "0" 165 // Retrieval info: PRIVATE: CREATE_INCLK1_CHECK STRING "0" 166 // Retrieval info: PRIVATE: CUR_DEDICATED_CLK STRING "c0" 167 // Retrieval info: PRIVATE: CUR_FBIN_CLK STRING "c0" 168 // Retrieval info: PRIVATE: DEVICE_SPEED_GRADE STRING "8" 169 // Retrieval info: PRIVATE: DIV_FACTOR0 NUMERIC "1" 170 // Retrieval info: PRIVATE: DUTY_CYCLE0 STRING "50.00000000" 171 // Retrieval info: PRIVATE: EFF_OUTPUT_FREQ_VALUE0 STRING "107.964478" 172 // Retrieval info: PRIVATE: EXPLICIT_SWITCHOVER_COUNTER STRING "0" 173 // Retrieval info: PRIVATE: EXT_FEEDBACK_RADIO STRING "0" 174 // Retrieval info: PRIVATE: GLOCKED_COUNTER_EDIT_CHANGED STRING "1" 175 // Retrieval info: PRIVATE: GLOCKED_FEATURE_ENABLED STRING "0" 176 // Retrieval info: PRIVATE: GLOCKED_MODE_CHECK STRING "0" 177 // Retrieval info: PRIVATE: GLOCK_COUNTER_EDIT NUMERIC "1048575" 178 // Retrieval info: PRIVATE: HAS_MANUAL_SWITCHOVER STRING "1" 179 // Retrieval info: PRIVATE: INCLK0_FREQ_EDIT STRING "50.000" 180 // Retrieval info: PRIVATE: INCLK0_FREQ_UNIT_COMBO STRING "MHz" 181 // Retrieval info: PRIVATE: INCLK1_FREQ_EDIT STRING "100.000" 182 // Retrieval info: PRIVATE: INCLK1_FREQ_EDIT_CHANGED STRING "1" 183 // Retrieval info: PRIVATE: INCLK1_FREQ_UNIT_CHANGED STRING "1" 184 // Retrieval info: PRIVATE: INCLK1_FREQ_UNIT_COMBO STRING "MHz" 185 // Retrieval info: PRIVATE: INTENDED_DEVICE_FAMILY STRING "Cyclone IV E" 186 // Retrieval info: PRIVATE: INT_FEEDBACK__MODE_RADIO STRING "1" 187 // Retrieval info: PRIVATE: LOCKED_OUTPUT_CHECK STRING "0" 188 // Retrieval info: PRIVATE: LONG_SCAN_RADIO STRING "1" 189 // Retrieval info: PRIVATE: LVDS_MODE_DATA_RATE STRING "Not Available" 190 // Retrieval info: PRIVATE: LVDS_MODE_DATA_RATE_DIRTY NUMERIC "0" 191 // Retrieval info: PRIVATE: LVDS_PHASE_SHIFT_UNIT0 STRING "deg" 192 // Retrieval info: PRIVATE: MIG_DEVICE_SPEED_GRADE STRING "Any" 193 // Retrieval info: PRIVATE: MIRROR_CLK0 STRING "0" 194 // Retrieval info: PRIVATE: MULT_FACTOR0 NUMERIC "1" 195 // Retrieval info: PRIVATE: NORMAL_MODE_RADIO STRING "1" 196 // Retrieval info: PRIVATE: OUTPUT_FREQ0 STRING "107.96448000" 197 // Retrieval info: PRIVATE: OUTPUT_FREQ_MODE0 STRING "1" 198 // Retrieval info: PRIVATE: OUTPUT_FREQ_UNIT0 STRING "MHz" 199 // Retrieval info: PRIVATE: PHASE_RECONFIG_FEATURE_ENABLED STRING "1" 200 // Retrieval info: PRIVATE: PHASE_RECONFIG_INPUTS_CHECK STRING "0" 201 // Retrieval info: PRIVATE: PHASE_SHIFT0 STRING "0.00000000" 202 // Retrieval info: PRIVATE: PHASE_SHIFT_STEP_ENABLED_CHECK STRING "0" 203 // Retrieval info: PRIVATE: PHASE_SHIFT_UNIT0 STRING "deg" 204 // Retrieval info: PRIVATE: PLL_ADVANCED_PARAM_CHECK STRING "0" 205 // Retrieval info: PRIVATE: PLL_ARESET_CHECK STRING "0" 206 // Retrieval info: PRIVATE: PLL_AUTOPLL_CHECK NUMERIC "1" 207 // Retrieval info: PRIVATE: PLL_ENHPLL_CHECK NUMERIC "0" 208 // Retrieval info: PRIVATE: PLL_FASTPLL_CHECK NUMERIC "0" 209 // Retrieval info: PRIVATE: PLL_FBMIMIC_CHECK STRING "0" 210 // Retrieval info: PRIVATE: PLL_LVDS_PLL_CHECK NUMERIC "0" 211 // Retrieval info: PRIVATE: PLL_PFDENA_CHECK STRING "0" 212 // Retrieval info: PRIVATE: PLL_TARGET_HARCOPY_CHECK NUMERIC "0" 213 // Retrieval info: PRIVATE: PRIMARY_CLK_COMBO STRING "inclk0" 214 // Retrieval info: PRIVATE: RECONFIG_FILE STRING "ceshi.mif" 215 // Retrieval info: PRIVATE: SACN_INPUTS_CHECK STRING "0" 216 // Retrieval info: PRIVATE: SCAN_FEATURE_ENABLED STRING "1" 217 // Retrieval info: PRIVATE: SELF_RESET_LOCK_LOSS STRING "0" 218 // Retrieval info: PRIVATE: SHORT_SCAN_RADIO STRING "0" 219 // Retrieval info: PRIVATE: SPREAD_FEATURE_ENABLED STRING "0" 220 // Retrieval info: PRIVATE: SPREAD_FREQ STRING "50.000" 221 // Retrieval info: PRIVATE: SPREAD_FREQ_UNIT STRING "KHz" 222 // Retrieval info: PRIVATE: SPREAD_PERCENT STRING "0.500" 223 // Retrieval info: PRIVATE: SPREAD_USE STRING "0" 224 // Retrieval info: PRIVATE: SRC_SYNCH_COMP_RADIO STRING "0" 225 // Retrieval info: PRIVATE: STICKY_CLK0 STRING "1" 226 // Retrieval info: PRIVATE: SWITCHOVER_COUNT_EDIT NUMERIC "1" 227 // Retrieval info: PRIVATE: SWITCHOVER_FEATURE_ENABLED STRING "1" 228 // Retrieval info: PRIVATE: SYNTH_WRAPPER_GEN_POSTFIX STRING "0" 229 // Retrieval info: PRIVATE: USE_CLK0 STRING "1" 230 // Retrieval info: PRIVATE: USE_CLKENA0 STRING "0" 231 // Retrieval info: PRIVATE: USE_MIL_SPEED_GRADE NUMERIC "0" 232 // Retrieval info: PRIVATE: ZERO_DELAY_RADIO STRING "0" 233 // Retrieval info: LIBRARY: altera_mf altera_mf.altera_mf_components.all 234 // Retrieval info: CONSTANT: BANDWIDTH_TYPE STRING "AUTO" 235 // Retrieval info: CONSTANT: CLK0_DIVIDE_BY NUMERIC "156250" 236 // Retrieval info: CONSTANT: CLK0_DUTY_CYCLE NUMERIC "50" 237 // Retrieval info: CONSTANT: CLK0_MULTIPLY_BY NUMERIC "337389" 238 // Retrieval info: CONSTANT: CLK0_PHASE_SHIFT STRING "0" 239 // Retrieval info: CONSTANT: COMPENSATE_CLOCK STRING "CLK0" 240 // Retrieval info: CONSTANT: INCLK0_INPUT_FREQUENCY NUMERIC "20000" 241 // Retrieval info: CONSTANT: INTENDED_DEVICE_FAMILY STRING "Cyclone IV E" 242 // Retrieval info: CONSTANT: LPM_TYPE STRING "altpll" 243 // Retrieval info: CONSTANT: OPERATION_MODE STRING "NORMAL" 244 // Retrieval info: CONSTANT: PLL_TYPE STRING "AUTO" 245 // Retrieval info: CONSTANT: PORT_ACTIVECLOCK STRING "PORT_UNUSED" 246 // Retrieval info: CONSTANT: PORT_ARESET STRING "PORT_UNUSED" 247 // Retrieval info: CONSTANT: PORT_CLKBAD0 STRING "PORT_UNUSED" 248 // Retrieval info: CONSTANT: PORT_CLKBAD1 STRING "PORT_UNUSED" 249 // Retrieval info: CONSTANT: PORT_CLKLOSS STRING "PORT_UNUSED" 250 // Retrieval info: CONSTANT: PORT_CLKSWITCH STRING "PORT_UNUSED" 251 // Retrieval info: CONSTANT: PORT_CONFIGUPDATE STRING "PORT_UNUSED" 252 // Retrieval info: CONSTANT: PORT_FBIN STRING "PORT_UNUSED" 253 // Retrieval info: CONSTANT: PORT_INCLK0 STRING "PORT_USED" 254 // Retrieval info: CONSTANT: PORT_INCLK1 STRING "PORT_UNUSED" 255 // Retrieval info: CONSTANT: PORT_LOCKED STRING "PORT_UNUSED" 256 // Retrieval info: CONSTANT: PORT_PFDENA STRING "PORT_UNUSED" 257 // Retrieval info: CONSTANT: PORT_PHASECOUNTERSELECT STRING "PORT_UNUSED" 258 // Retrieval info: CONSTANT: PORT_PHASEDONE STRING "PORT_UNUSED" 259 // Retrieval info: CONSTANT: PORT_PHASESTEP STRING "PORT_UNUSED" 260 // Retrieval info: CONSTANT: PORT_PHASEUPDOWN STRING "PORT_UNUSED" 261 // Retrieval info: CONSTANT: PORT_PLLENA STRING "PORT_UNUSED" 262 // Retrieval info: CONSTANT: PORT_SCANACLR STRING "PORT_UNUSED" 263 // Retrieval info: CONSTANT: PORT_SCANCLK STRING "PORT_UNUSED" 264 // Retrieval info: CONSTANT: PORT_SCANCLKENA STRING "PORT_UNUSED" 265 // Retrieval info: CONSTANT: PORT_SCANDATA STRING "PORT_UNUSED" 266 // Retrieval info: CONSTANT: PORT_SCANDATAOUT STRING "PORT_UNUSED" 267 // Retrieval info: CONSTANT: PORT_SCANDONE STRING "PORT_UNUSED" 268 // Retrieval info: CONSTANT: PORT_SCANREAD STRING "PORT_UNUSED" 269 // Retrieval info: CONSTANT: PORT_SCANWRITE STRING "PORT_UNUSED" 270 // Retrieval info: CONSTANT: PORT_clk0 STRING "PORT_USED" 271 // Retrieval info: CONSTANT: PORT_clk1 STRING "PORT_UNUSED" 272 // Retrieval info: CONSTANT: PORT_clk2 STRING "PORT_UNUSED" 273 // Retrieval info: CONSTANT: PORT_clk3 STRING "PORT_UNUSED" 274 // Retrieval info: CONSTANT: PORT_clk4 STRING "PORT_UNUSED" 275 // Retrieval info: CONSTANT: PORT_clk5 STRING "PORT_UNUSED" 276 // Retrieval info: CONSTANT: PORT_clkena0 STRING "PORT_UNUSED" 277 // Retrieval info: CONSTANT: PORT_clkena1 STRING "PORT_UNUSED" 278 // Retrieval info: CONSTANT: PORT_clkena2 STRING "PORT_UNUSED" 279 // Retrieval info: CONSTANT: PORT_clkena3 STRING "PORT_UNUSED" 280 // Retrieval info: CONSTANT: PORT_clkena4 STRING "PORT_UNUSED" 281 // Retrieval info: CONSTANT: PORT_clkena5 STRING "PORT_UNUSED" 282 // Retrieval info: CONSTANT: PORT_extclk0 STRING "PORT_UNUSED" 283 // Retrieval info: CONSTANT: PORT_extclk1 STRING "PORT_UNUSED" 284 // Retrieval info: CONSTANT: PORT_extclk2 STRING "PORT_UNUSED" 285 // Retrieval info: CONSTANT: PORT_extclk3 STRING "PORT_UNUSED" 286 // Retrieval info: CONSTANT: WIDTH_CLOCK NUMERIC "5" 287 // Retrieval info: USED_PORT: @clk 0 0 5 0 OUTPUT_CLK_EXT VCC "@clk[4..0]" 288 // Retrieval info: USED_PORT: c0 0 0 0 0 OUTPUT_CLK_EXT VCC "c0" 289 // Retrieval info: USED_PORT: inclk0 0 0 0 0 INPUT_CLK_EXT GND "inclk0" 290 // Retrieval info: CONNECT: @inclk 0 0 1 1 GND 0 0 0 0 291 // Retrieval info: CONNECT: @inclk 0 0 1 0 inclk0 0 0 0 0 292 // Retrieval info: CONNECT: c0 0 0 0 0 @clk 0 0 1 0 293 // Retrieval info: GEN_FILE: TYPE_NORMAL ceshi.v TRUE 294 // Retrieval info: GEN_FILE: TYPE_NORMAL ceshi.ppf TRUE 295 // Retrieval info: GEN_FILE: TYPE_NORMAL ceshi.inc TRUE 296 // Retrieval info: GEN_FILE: TYPE_NORMAL ceshi.cmp TRUE 297 // Retrieval info: GEN_FILE: TYPE_NORMAL ceshi.bsf TRUE 298 // Retrieval info: GEN_FILE: TYPE_NORMAL ceshi_inst.v TRUE 299 // Retrieval info: GEN_FILE: TYPE_NORMAL ceshi_bb.v TRUE 300 // Retrieval info: LIB_FILE: altera_mf 301 // Retrieval info: CBX_MODULE_PREFIX: ON

testbench:

1 // Copyright (C) 1991-2012 Altera Corporation 2 // Your use of Altera Corporation's design tools, logic functions 3 // and other software and tools, and its AMPP partner logic 4 // functions, and any output files from any of the foregoing 5 // (including device programming or simulation files), and any 6 // associated documentation or information are expressly subject 7 // to the terms and conditions of the Altera Program License 8 // Subscription Agreement, Altera MegaCore Function License 9 // Agreement, or other applicable license agreement, including, 10 // without limitation, that your use is for the sole purpose of 11 // programming logic devices manufactured by Altera and sold by 12 // Altera or its authorized distributors. Please refer to the 13 // applicable agreement for further details. 14 15 // ***************************************************************************** 16 // This file contains a Verilog test bench template that is freely editable to 17 // suit user's needs .Comments are provided in each section to help the user 18 // fill out necessary details. 19 // ***************************************************************************** 20 // Generated on "07/19/2017 19:00:02" 21 22 // Verilog Test Bench template for design : VGA_display_easy 23 // 24 // Simulation tool : ModelSim (Verilog) 25 // 26 27 `timescale 10 ns/ 1 ps 28 module VGA_display_easy_vlg_tst(); 29 // constants 30 // general purpose registers 31 32 reg clk; 33 reg rst_n; 34 // wires 35 wire b_vga; 36 wire clk_vga; 37 wire g_vga; 38 wire hs_vga; 39 wire r_vga; 40 wire vs_vga; 41 42 // assign statements (if any) 43 VGA_display_easy i1 ( 44 // port map - connection between master ports and signals/registers 45 .b_vga(b_vga), 46 .clk(clk), 47 .clk_vga(clk_vga), 48 .g_vga(g_vga), 49 .hs_vga(hs_vga), 50 .r_vga(r_vga), 51 .rst_n(rst_n), 52 .vs_vga(vs_vga) 53 ); 54 initial 55 begin 56 clk = 0; 57 end 58 always 59 begin 60 #1 clk = ~clk; 61 end 62 endmodule

未完待续。。。

参考:

Crazy Bingo:http://www.cnblogs.com/crazybingo/archive/2011/02/24/1963652.html

《EDA技术实用教程--Verilog HDL版(第四版)》---- 潘松、黄继业、潘明 编著

如有错误还请指出,如有侵权还请告知,如需转载请注明出处!

本人博客:http://www.cnblogs.com/yllinux/