Xilinx 7系列FPGA收发器架构之硬件设计指导(一)

引言:本文我们介绍Xilinx 7系列FPGA收发器硬件设计主要注意的一些问题,指导硬件设计人员进行原理图及PCB设计。本文介绍以下内容:

- GTX/GTH收发器管脚概述

- GTX/GTH收发器时钟设计

- GTXGTH收发器电源设计

1.概述

Xilinx 7系列FPGA GTX/GTH收发器是模拟电路,当设计和实现PCB设计需要特殊考虑和注意。这其中涉及器件管脚功能、传输线阻抗和布线、供电设计滤波、器件选择、PCB布线和层叠设计相关内容。

2.管脚描述和设计指导

2.1 GTX/GTH收发器管脚描述

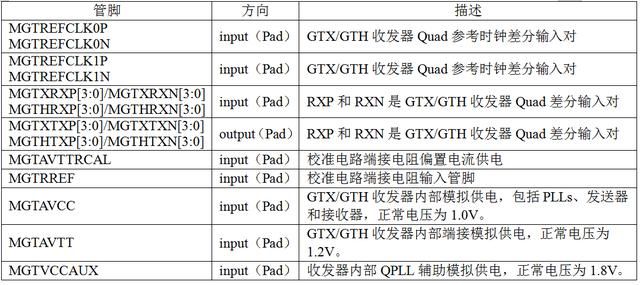

GTX/GTH收发器管脚定义如图1所示。

图1、GTX/GTH收发器管脚定义

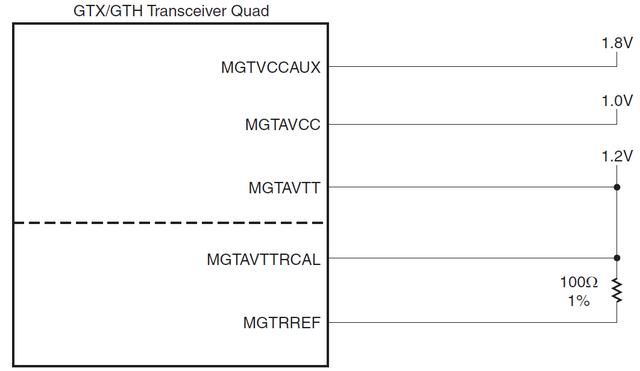

图2显示了GTX/GTH收发器外部电源供电连接图,图中电压的供电要求可以参考7系列FPGA器件手册。

图2、GTX/GTH收发器外部电源供电连接图

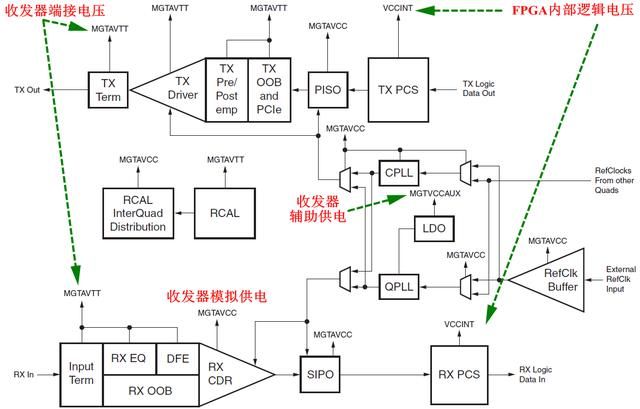

图3显示了GTX/GTH收发器内部电源连接详细框图。

图3、GTX/GTH收发器内部电源连接详细框图

2.2 端接电阻校准电路

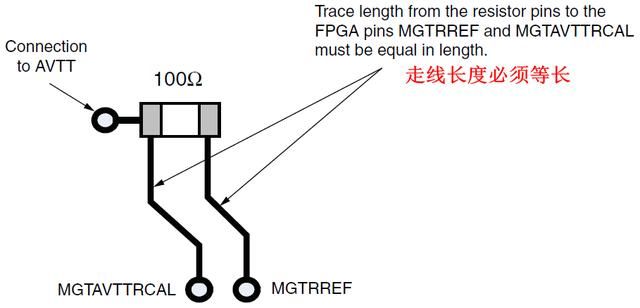

GTX/GTH收发器Quad列中所有Quad共用一个电阻校准电路(RCAL),该电路硬件连接如图4所示。

图4、RCAL电阻PCB布线

RCAL电路仅在FPGA配置器件执行校准功能,在配置前所有模拟电压必须达到7系列FPGA器件手册要求的电压和容忍误差。如果整个GTX/GTH收发器Quad列没有使用,MGTAVTTRCAL和MGTRREF管脚必须接地。外部电阻连接如图4所示,图中电阻精度满足100Ω±1%,PCB布线时满足等长。

2.3 模拟电源供电管脚

GTX/GTH收发器Quad模拟电源在器件封装内部有电源平面,对于某些封装会有多个电源层平面。如果器件封装有多个电源平面,电源供电管脚会有一个“_G#”尾缀标识属于哪个电源层平面。如果所有的Quads没有使用,电源管脚可以悬空或者连接到GND。

3.参考时钟设计

3.1 概述

当为GTX/GTH收发器参考输入时钟选择输入时钟时,需要考虑以下因素:

- 频率范围

- 输出电压摆幅

- 抖动

- 上升和下降时间

- 供电和电流

- 噪声特性

- 占空比和占空比精度

- 频率稳定度

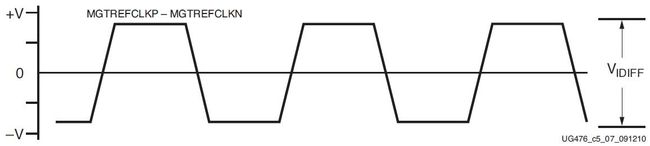

图5显示了GTX/GTH差分时钟输入电压摆幅定义。

图5、GTX/GTH差分时钟输入电压摆幅定义

图6显示了差分时钟上升设计和下降时间定义。

图6、差分时钟上升设计和下降时间定义

图7显示了MGTREFCLK输入Buffer详细结构。图中时钟管脚内部上拉至0.8V。

图7、MGTREFCLK输入Buffer详细结构

3.2 GTX/GTH收发器参考时钟检查列表

当为GTX/GTH收发器选择晶振时,以下规则必须满足:

- 晶振的输出和GTX/GTH收发器Quad时钟输入管脚之间提供AC耦合;

- 确保参考时钟差分电压摆幅满足Kintex-7 FPGA器件手册DS182和Virtex-7 FPGA器件手册DS183 DC和开关特性要求;

- 满足和优于Kintex-7 FPGA器件手册DS182和Virtex-7 FPGA器件手册DS183 DC和开关特性要求;

- 满足和优于GTX/GTH收发器支持的物理层协议要求的参考时钟特性;

- 遵守晶振供应商的供电,布板布线和噪声特性要求;

- 提供晶振和GTX/GTH收发器Quad时钟输入管脚之间专用的点对点连接;

- 保持差分传输线阻抗不连续最小(阻抗不连续会产生时钟抖动)。

4.参考时钟接口

4.1参考时钟接口要求

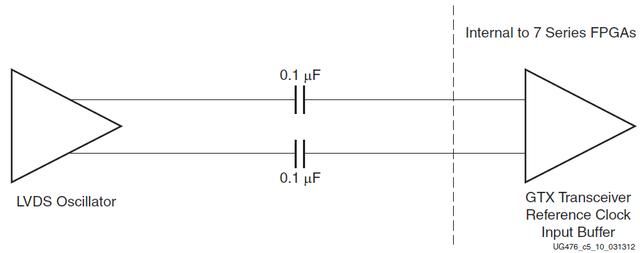

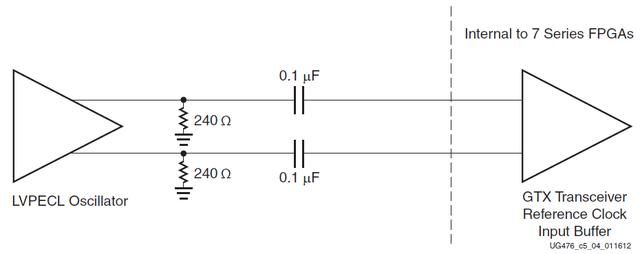

FPGA收发器GTX/GTH参考时钟接口提供两种连接方式:LVDS(如图8所示)和LVPECL(如图2所示)。我们在选择晶振时,至少要支持其中一种接口输出电平标准。图9所示的电阻值为一般推荐值,实际偏置电阻值需要参考晶振手册。

图8和图9中交流AC耦合电容作用:1)阻断外部晶振和GTX/GTH收发器Quad专用时钟输入管脚之间的DC电流,降低功耗;2)AC耦合电容和参考时钟输入端接构成高通滤波器,衰减参考时钟偏移;3)保持耦合电容两侧共模电压独立,互不干扰。

图8、LVDS晶振和7系列FPGA收发器参考时钟输入接口

图9、LVPECL晶振和7系列FPGA收发器参考时钟输入接口

如果参考时钟未使用,则参考时钟MGTREFCLKP和MGTREFCLKN应该悬空。

4.电源供电和滤波

4.1 概述

GTX/GTH收发器一般需要三种电源供电:MGTAVCC、MGTVCCAUX和MGTAVTT。GTX/GTH收发器对电源噪声非常敏感,电源噪声会导致收发器性能下降。噪声通常来源于:

- 电源稳压器噪声

- 电源分布网络

- 来自其他电路耦合

每种噪声源在设计和实现时都必须仔细考虑,在FPGA输入管脚测量的总的噪声Vpk-pk不能超过10mV。

正常情况下,GTX/GTH模拟电源最后一级稳压器应该尽量靠近收发器供电管脚,减小稳压器输出管脚和收发器电源输入管脚之间的距离,降低耦合噪声概率。

4.2 电源分布网络和去偶电容

Die去耦电容

Die内部电容主要对高频噪声起滤波作用。

封装去耦电容

7系列FPGA封装有附加的去耦电容。MGTAVCC、MGTAVTT和MGTVCCAUX管脚去耦电容特性如图10所示。

图10、MGTAVCC、MGTAVTT和MGTVCCAUX管脚去耦电容特性

PCB电路板去耦电容

PCB电路板上的去耦电容应该靠近GTX/GTH收发器电源管脚,这些电容减少了PCB电源网络阻抗。电源管脚噪声在10kHz~80MHz带宽内不能超过10mVpp。推荐的PCB电路板去耦电容如图11所示。

图11、推荐的PCB电路板去耦电容

更多其他技术文章可以关注我的微信公众号“FPGA技术实战”,欢迎交流 !