黑金AX7020 && ZYNQ7000 (一) PL流水灯设计

硬件平台:黑金AX7020

开发环境:widows7 旗舰版 x64

开发软件:vivado 2015.4

一,建立工程

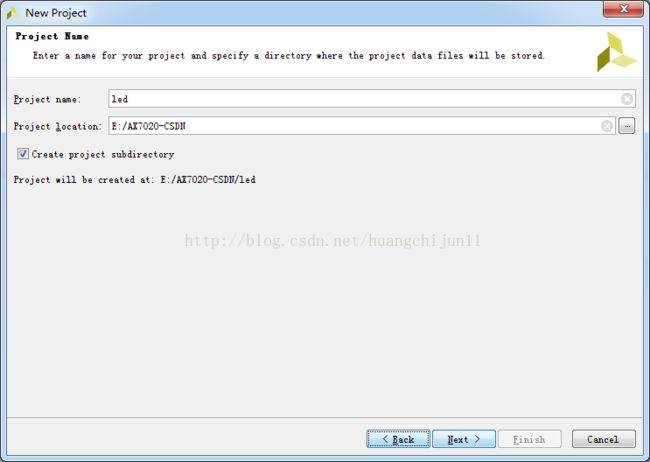

打开vivado,点击create new project,如下图1所示,选择工程路径,填写文件名,接着选next

图1 建立工程

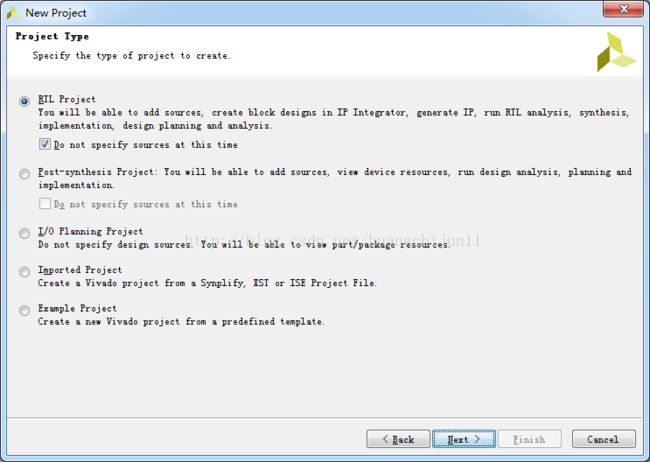

选择工程类型,为RTL Project,如下图2所示

图2 选择工程类型

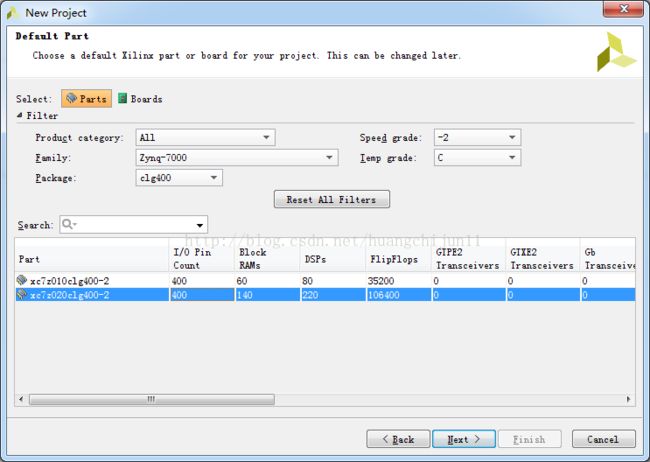

选择器件,Zynq-7000 clg400-2 c,如下图3所示

图3 选择器件图

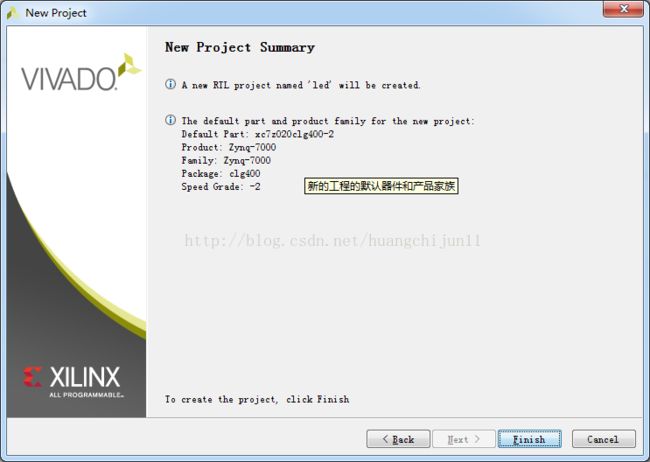

确认自己的选择没有错误,点击Finish,如图4所示

图4 建立工程完成图

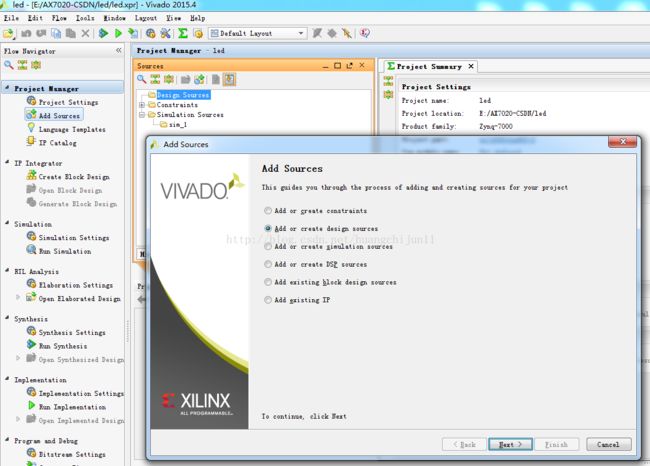

二,添加工程源文件

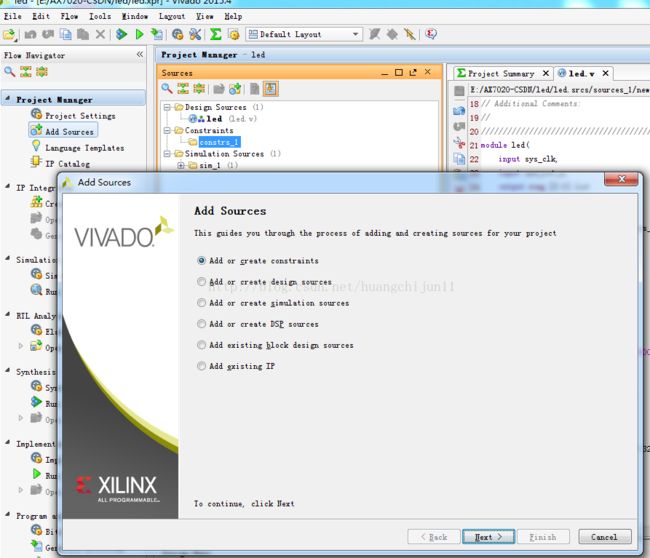

选中Design Sources 点击Add Sources,在弹出的界面中选择Add or create design sources选项,如下图5所示

图5 添加源文件图

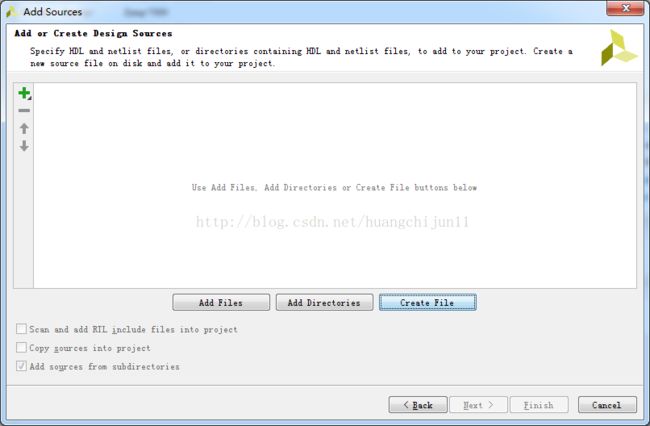

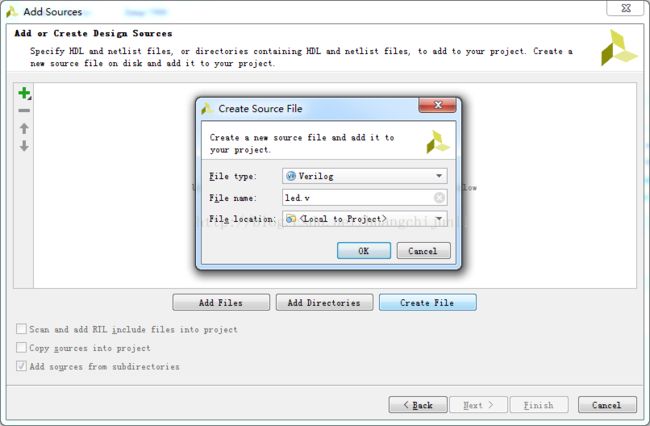

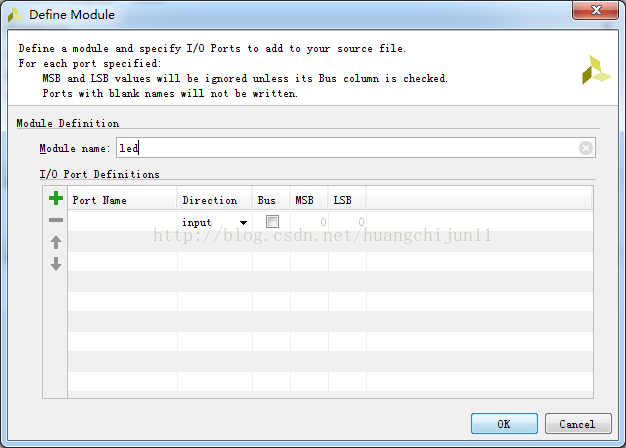

如图6和图7所示,点击Create File按钮,再弹出的对话框里选择File type是verilog, File name为led.v,点击OK按钮

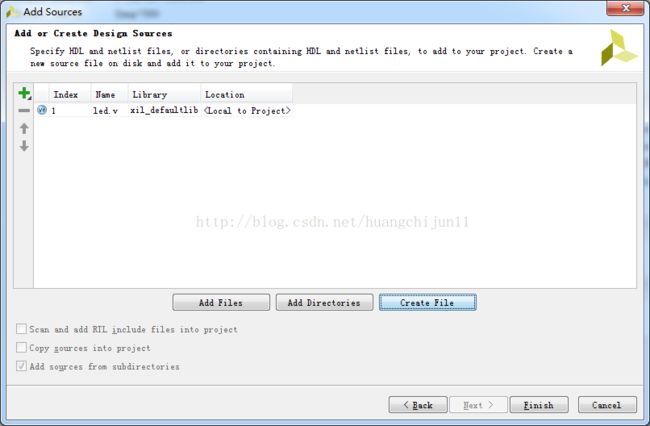

点击ok,会出现下图所示

这个时候会提示您定义I/O的端口,这里我们不定义,后面在程序中编写,下图直接选择OK

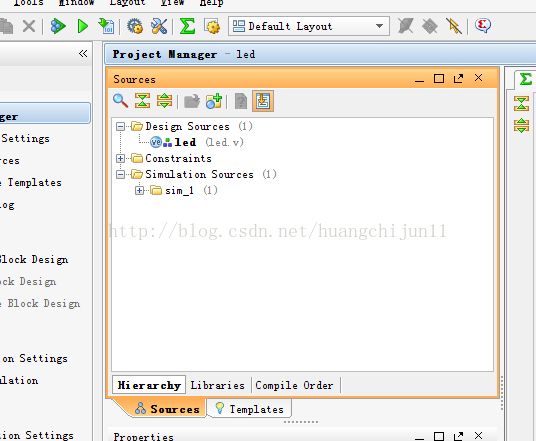

这时在Project Manager界面下的Design Sources里已经有一个led.v文件,并且自动成为项目的Top模块

三,编写源文件

编写led.v文件,我们定义一个32位的寄存器timer,用于循环计数,计数达到9000000的时候,寄存器timer变为0,内容如下

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2016/09/28 15:04:30

// Design Name:

// Module Name: led

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module led(

input sys_clk,

input sys_rst_n,

output reg [3:0] led

);

reg[31:0] timer_cnt;

always@(posedge sys_clk or negedge sys_rst_n)

begin

if(sys_rst_n==1'b0)

begin

led <= 4'b1000;

timer_cnt <= 32'b0;

end

else

begin

if(timer_cnt == 32'd9000000)

begin

timer_cnt <= 32'b0;

led<= (led>>1)|(led<<3);

end

else

begin

timer_cnt <= timer_cnt + 32'b1;

end

end

end

endmodule

小灯的移位采用“左移1位+右移N-1”模式,如下所示:

led<= (led>>1)|(led<<3);四,添加工程约束文件

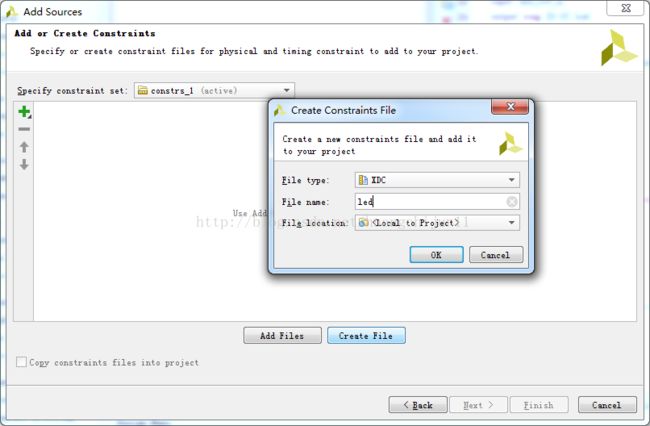

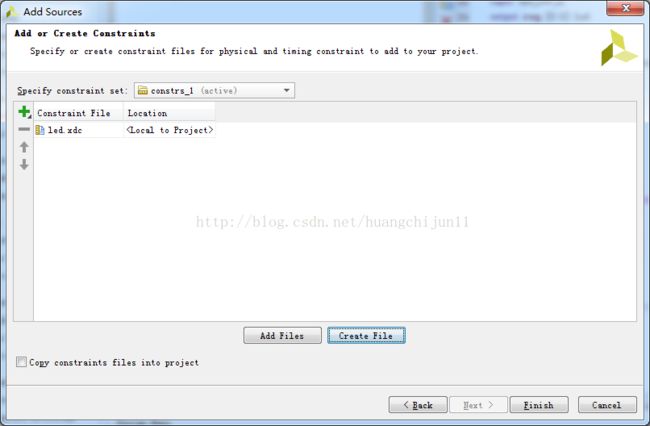

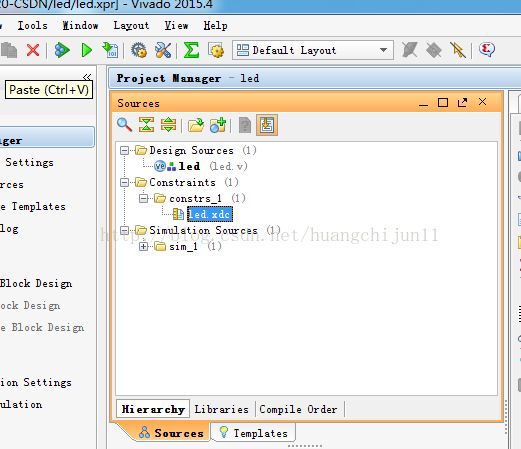

如图所示进行添加,

编写led.xdc文件,添加如下约束管脚定义

set_property IOSTANDARD LVCMOS33 [get_ports {led[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports sys_clk]

set_property IOSTANDARD LVCMOS33 [get_ports sys_rst_n]

set_property PACKAGE_PIN J16 [get_ports {led[3]}]

set_property PACKAGE_PIN K16 [get_ports {led[2]}]

set_property PACKAGE_PIN M15 [get_ports {led[1]}]

set_property PACKAGE_PIN M14 [get_ports {led[0]}]

set_property PACKAGE_PIN U18 [get_ports sys_clk]

set_property PACKAGE_PIN L15 [get_ports sys_rst_n]这里使用了最基本的XDC编写的语法,普通IO口只需要约束引脚号和电压,管脚约束如下:

set_property PACKAGE_PIN "引脚编号" [get_ports "端口名称"]

电平信号的约束如下:

set_property IOSTANDARD "电压" [get_ports "端口名称"]

五,编译

点击Run Systhesis,即可开始综合并生成网表文件,然后点击Run Implementation来开始布局布线,布线完成后在一个提示小窗口中,选择点击Generate Bitstream即可生成bit文件

六,下载和调试

连接实验板的JPAG接口,进行下载,会出现LED的流水灯点亮了。