Xilinx Zynq7000系列学习

1 SoC Zynq-7000

Zynq®-7000 AllProgrammable (全可编程) SoC 重新定义了嵌入式系统的可能性,为系统架构师和软件开发人员推出新的解决方案提供了一个灵活的平台,同时为传统 ASIC 和 SoC 用户提供了一个全可编程的备选方案。

双核 ARM® Cortex ™ -A9 处理器与业界领先的、具有高性能功耗比的 28nm 可编程逻辑巧妙集成,实现的功耗和性能等级远超分立处理器和 FPGA 系统。Zynq-7000 SoC 是业界首款 All Programmable SoC,也是同类产品市场的先锋。凭借最高性能 - 价格 - 功耗比,该产品成为很多嵌入式应用领域的最佳选择,包括小型蜂窝基站、多摄像头驾驶员辅助系统、工业自动化机器视觉、医疗内窥镜和 4K2K 超高清电视。

Zynq-7000由ARM处理器系统而非可编程逻辑元件进行控制,处理系统能够在开机时引导并运行各个独立于可编程逻辑之外的操作系统。

l PS: 处理系统(Processing System),与FPGA无关的ARM的SOC的部分。

l PL: 可编程逻辑(Progarmmable Logic),FPGA部分。

l APU: 应用处理器单元(Application Processor Unit)。位于PS里面的中心位置。

l SCU: Snoop Control Unit,用来保持双核之间的数据Cache的一致性。也就是说,第一个A9处理器写存储时,只是写在了缓存里,没有进主存,如果第二个A9读操作,涉及到第一个写脏了的数据段,SCU要保证第二个A9的缓存里是最新的数据。如果第二个A9写同样数据段的数据,需要在第一个中体现出写的内容。SCU的存在,才使得两个核成互相联系的“双核”,才能成为Mpsoc。

2 PS&PL

2.1 PS/PL电源

PS和PL需分配到不同的电源平面上,PS和PL都有专用的电源引脚,要有独立电源供应路径。如果不需要PL的休眠模式,可将两者的电源连在一起。当PS处于休眠模式,使得PL处于永久复位的状态。通过外部引脚可对PL进行电源管理,因此可设计外部电源管理电路对电源进行管理,而外部电源管理电路可由软件和PS的GPIO控制。

电源模式:

Ø PL休眠Programmable Logic Power Off (Sleep)

PS和PL有不同的电源平面,PL可处于休眠模式。PL不能先于PS上电,每次上电之后都需要对PL进行重新配置。

Ø PS Clock Control

利用内部的PLLs PS可以30MHz的时钟频率运行,时钟频率也可动态改变。

Ø Single Processor Mode

可通过时钟门关闭第二个Cortex-APCPU。

PS和PL的电源是独立的,但是当激活PL的电源时,PS的电源必须已经被激活。当不需要PL时可关闭PL。在PS中处理器必须首先启动,PL的配置过程以软件为中心,软件对PL的配置进行管理。

2.2 PS-PL 接口

PS-PL接口有两类:

Ø 功能接口:AXI、EMIO、中断、DMA、时钟、调试

Ø 配置接口:processorconfiguration access port (PCAP)、配置状态、single event upset (SEU)、配置/完成/初始化

PL和PS数据传输的高效接口有两个:AXI(PS主动)和ACP(PL主动)。PL访问DDR可通过AXI接口,可配置成32-bit或者64-bit。

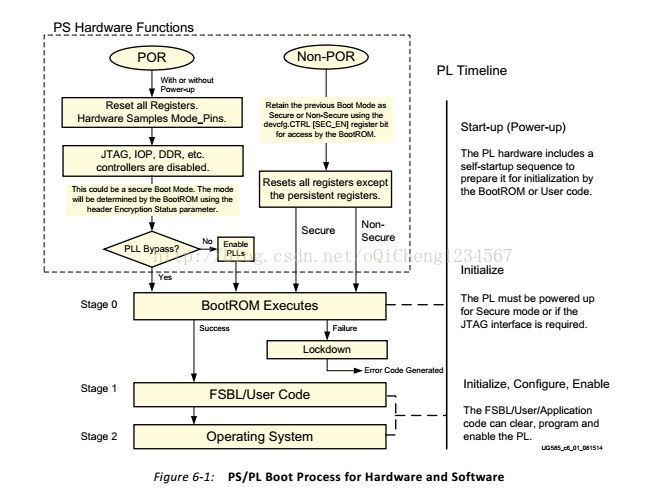

2.3 启动和配置

Zynq-7000需要多级启动过程,并支持安全启动和非安全启动。PS控制器件的启动和配置。为了安全启动,PL部分必须上电保证位于PL内的安全时钟工作,它提供了256-bit 的AES和SHA(解密和认证)。

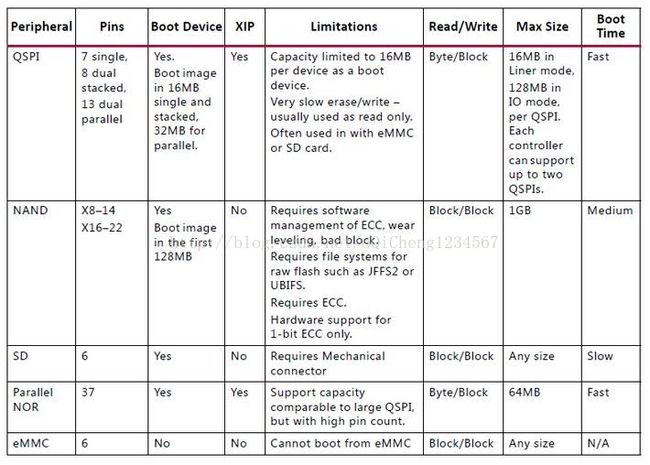

外部配置引脚决定启动器件类型:NOR,NAND,Quad-SPI,SD或者JTAG,JTAG是非安全启动模式。

其中一个ARM Cortex-A9执行片上ROM中的代码,从启动器件中将FSBL(first stageboot loader)拷贝到OCM(on-chip memory),然后处理器执行FSBL。Xilinx提供FSBLs例子,用户也可以自己设置。FSBL开始PS的启动,同时也可以配置PL(PL的配置也可推迟到下级过程)。

图2.1 典型启动过程

PL初始化和配置分为四个步骤:

a) 启动(PL上电)

b) 初始化(PS控制或者INIT/PROGRAM控制引脚)

c) 配置(PS PCAP,JTAG,PL ICAP)

d) 使能PS-PL接口(PS控制)

PS软件可对PL进行配置和重配置,PL配置路径PCAP是最常用的方法。配置路径如下:

l 利用TAP(test accessport)JTAG调试(常用);

l PS PCAP(processor configuration access port);

l ICAP(非常用);

2.4 调试(Hardware and Software)

在Zynq-7000系列中,调试系统都是基于ARM的CoreSight architecture,包括embeddedtrace buffer (ETB)、program trace macrocell (PTM)、instrument trace macrocell(ITM)。PL利用集成的逻辑分析仪调试。

2.4.1 调试端口

有两个JTAG口,可连在一起,也可分别独立使用。

当连在一起,可用于ARM处理器代码下载、实时控制操作、PL的配置、利用ChipScopeTM调试PL,软件开发工具(SDK)和ChipScopeTM共用一个下载线路。

PL的TAP(test accessport)和PS的DAP(debug access port)对于外部的JTAG调试工具都是可见的。连接在PL端的PL_TDO/TMS/TCK/TDI,同时可访问PL和PS。(This is the normal debugcase for most applications。)

当分开时,一个用于PS,可直接访问ARM的DAP(debug accessport)接口,这个CoreSight接口可用于ARM-compliant调试和软件开发工具例如Development Studio 5 (DS-5™)。需通过MIO或者EMIO和PL引脚配置ARM DAP接口。

另一个JTAG口用于PL的开发,同独立的FPGA。

需要注意的是,JTAG调试时PL和PS都需要上电。

3 开发工具

Vivado

Xilink SDK

3.1 PL 调试工具

Chipscope