FPGA常用通信协议---SPI

前言

本文,参考几篇博客,总结一下个人对SPI的理解。

文中的一些文字、图片等来源自参考的博客。

在文后,附上参考的博客链接。

本文重点介绍一下SPI的概念和传输协议,以及FPGA之间通过SPI进行数据传输的方案分析。代码和仿真本文就不做了。

1、SPI概述

SPI(Serial Peripheral Interface)——串行外围设备接口。SPI接口主要应用在EEPROM、FLASH、实时时钟,AD转换器以及数字信号处理器和数字信号解码器之间。SPI是一种高速,全双工,同步的通信总线,在芯片上只占用四根线(CS、MOSI、MISO、SCK),极大的节约了芯片的引脚。

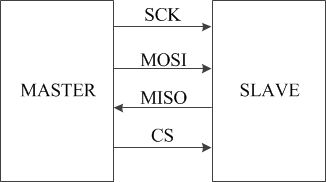

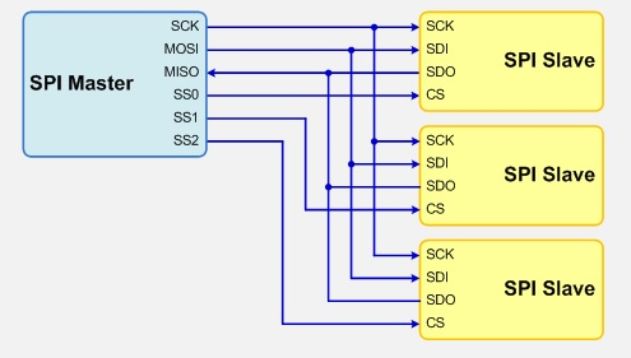

SPI以主从方式工作,这种模式通常有一个主设备和一个或者多个从设备。图1是一个主设备一个从设备的物理连接示意图。

图中SCK是由主设备发送给从的时钟,该时钟决定了主设备发送数据的速率;

MOSI是主设备发送给从设备的数据;

MISO是从设备发送给主设备的数据;

CS是片选信号,即只有片选信号为预先规定的使能信号时(高电平或者低电平)对此芯片的操作才有效。

2、SPI通信协议

CPOL/CPHA及通讯模式

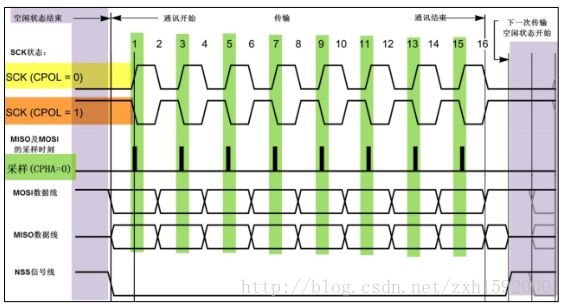

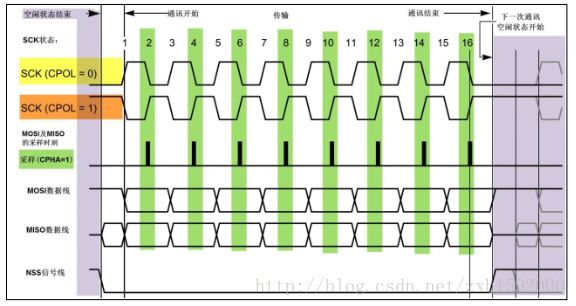

SPI 一共有四种通讯模式,它们的主要区别是总线空闲时 SCK 的时钟状态以及数据采样时刻。为方便说明,在此引入“时钟极性 CPOL”和“时钟相位CPHA”的概念。

时钟极性 CPOL :是指 SPI 通讯设备处于空闲状态时,SCK 信号线的电平信号(即 SPI 通讯开始前、 NSS 线为高电平时 SCK 的状态)。CPOL=0 时, SCK在空闲状态时为低电平,CPOL=1 时,则相反。

时钟相位 CPHA :是指数据的采样的时刻,当 CPHA=0 时,MOSI 或 MISO 数据线上的信号将会在 SCK 时钟线的“奇数边沿”被采样。当 CPHA=1 时,数据线在 SCK 的“偶数边沿”采样。

由CPOL/CPHA的不同状态,SPI分为四种模式,实际中采用较多的是“模式 0”与“模式 3”。

| SPI模式 | CPOL | CPHA | 空闲时SCK时钟电平 | 采样时刻 |

| 0 | 0 | 0 | 低电平 | 奇数边沿 |

| 1 | 0 | 1 | 低电平 | 偶数边沿 |

| 2 | 1 | 0 | 高电平 | 奇数边沿 |

| 3 | 1 | 1 | 高电平 | 偶数边沿 |

3、基于FPGA实现SPI通信

以实现上文SPI模式0的时序为例。

这里仅是 仿照 SPI的通信协议进行两片FPGA之间的通信。

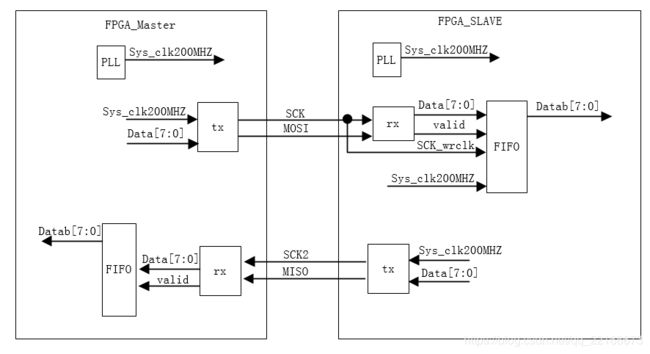

架构设计:

下面是两个FPGA之间进行串行通信,两个FPGA之间可能通过线缆进行数据传输,线缆上信号延迟可能达到几十个ns。

tx:是发送模块,将并行数据data[7:0]转成串行数据MOSI,SCK是MOSI的采样时钟,SCK上升沿时、从机(rx)对MOSI进行数据采样;

rx:接收模块,在SCK的上升沿对MOSI进行数据采样,转换成并行数据data[7:0],同时输出valid信号,指示当前data数据有效。

FIFO:该模块用于将rx模块送出的并行数据data进行跨时钟域转换。

FPGA_SLAVE向master发送数据MISO的时候,流程也是同样的,可以直接使用rx/tx模块。

tx模块发送时序说明,如下图所示。

可以使用一个快时钟,造SCLK信号,将并行data[7:0]数据转成串行数据MOSI。

a.在发送data期间,SCLK是以时钟脉冲的形式发送,即从机检查到SCLK的上升沿的时候,就开始进行数据采样、进行串并转换。在没有发数据的时候,SCLK为低电平。

也可以,将下图中的SS信号线的低电平,作为传输一个数据data[7:0]的标志。即SS低电平期间,当SCLK上升沿到来的时候,从机rx对MOSI进行数据采样。

b.也可以使SCLK时钟一直存在,通过SS信号来标识一次传输的data[7:0]数据。SCLK时钟一直存在的话,也方便接收模块进行串并转换、产生data[7:0]和valid信号。

>>点击这里返回导航页<<

参考文献

| 1.千里沽山 | https://blog.csdn.net/weixin_42509369/article/details/83096349 |

| 2.小时候挺菜 | https://blog.csdn.net/z735640642/article/details/84306421 |

| 3.jgliu | https://www.cnblogs.com/liujinggang/p/9609739.html |