FPGA常用通信协议之UART

目录

1、概述

2、基于FPGA的UART串口设计实践

2.1需求分析

3、RS232接口的可靠传输方法

4、参考文献

1、概述

UART:通用异步收发传输器(Universal Asynchronous Receiver/Transmitter),通常称作UART。UART端口有4个pin(VCC, GND, RX, TX), 用的TTL电平, 低电平为0(0V),高电平为1(3.3V或以上)。

![]()

UART是一种通用串行数据总线,用于异步通信。该总线双向通信,可以实现全双工传输和接收。在单片机中UART可以说是一种最基本的配置,很多与电脑进行通信的设备都采用到它。

- TX - 数据发送接口

- RX - 数据接受接口

两个设备间将TX与RX相连,RX与TX相连即可正常工作。最常用到的就是我们电脑上的USB那就是个最典型的UART接口。

UART使用标准的TTL/CMOS逻辑电平(0~5v、0~3.3v、0~2.5v或0~1.8v)来表示数据,高电平表示1,低电平表示0。为了增强数据的抗干扰能力、提高传输长度,通常将TTL/CMOD逻辑电平转换为RS-232逻辑电平,3~12v表示0,-3~-12v表示1

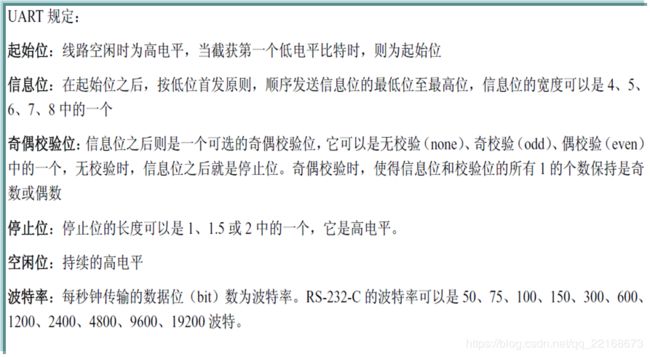

TxD、RxD数据线以位为最小单位传输数据,而帧由具有完整意义的、不可分割的若干位组成,它包含开始位、数据位、校验位(需要的话)和停止位。发送数据之前,UART之间要约定好数据的传输速率(即每位所占据的时间,其倒数称为波特率)、数据的传输格式(即有多少个数据位、是否使用校验位、是奇校验还是偶校验、有多少个停止位)。

数据传输流程如下:

(1)空闲状态:平时数据线处于空闲状态(1状态)

(2)发送起始位:当要发送数据时,UART改变TxD数据线的状态(变为0状态)并维持1位的时间。

这样接收方检测到开始位后,在等待1.5位的时间就开始一位一位地检测数据线的状态得到所传输的数据。

(3)发送信息位:UART一帧中可以有5、6、7或8位的数据,发送方一位一位地改变数据线的状态将他们发送出去,首先发送最低位。

(4)奇偶校验位:如果使用校验功能,UART在发送完数据后,还要发送1位校验位。有两种校验方法:奇校验、偶校验——数据位连同校验位中,1的数据等于奇数或偶数。

(5)停止位:最后,发送停止位,数据线恢复到空闲状态(1状态)。停止位的长度有3种:1位、1.5位、2位。

2、基于FPGA的UART串口设计实践

2.1需求分析

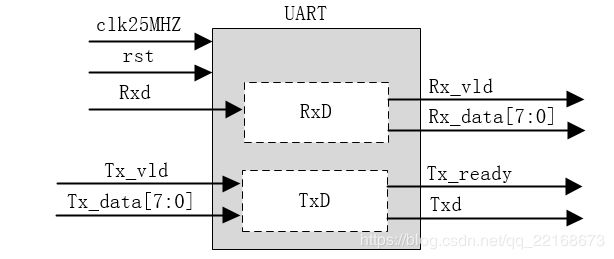

sys_clk位25MHZ,波特率=9600,起始位=1,信息位=8,无奇偶校验位,停止位=1。

波特率=9600,则一个信息位持续时间是1/9600s。即在25MHZ时钟下,需要计数2604个时钟周期。

采用一个计数范围[0:2603]的计数器,当器计数到1301的时候,开始采样Rxd_r上的数据。

rxd_r是rxd信号,经过clk25MHZ打三拍产生,作为数据rxd跨时钟域的处理。

架构如下:

tx_ready:高电平,表示UART空闲,可以接收tx_data[7:0]的数据。

下图是UART接收数据的时序示意图。

UART发送数据的时序图,与上图类似,不再做详细的时序绘制。

UART FPGA工程代码下载链接:

正在整理中。。。。。

3、RS232接口的可靠传输方法

参考原文https://blog.csdn.net/k331922164/article/details/51429544

参考文献

在UART的概述中,引用了下面两篇博客的部分内容,非常感谢原文作者的分享!

https://blog.csdn.net/zhyfxy/article/details/71102867

https://blog.csdn.net/jirryzhang/article/details/70084743

>>点击这里返回导航页<<

设计并验证带有FIFO的UART接收器和发送器。要求在Testbench中联合验证。

其中,sys_clk频率为100MHz,uart_clk=16*9600=153600Hz,波特率=9600,启始位=1,信息位=8,奇偶校验位=0,停止位=1,空闲位=1

设计并验证带有FIFO的UART接收器和发送器。要求在Testbench中联合验证。

其中,sys_clk频率为100MHz,uart_clk=16*9600=153600Hz,波特率=9600,启始位=1,信息位=8,奇偶校验位=0,停止位=1,空闲位=1