【数字IC前端】System Verilog常见问题

汇总了数字芯片实验室公众号的文章,微信搜索即可。

附IC面试常考题链接:

SystemVerilog常见问题汇总

- 1、什么是callback?

- 2、什么是factory pattern?

- 3、解释数据类型logic、 reg和wire之间的区别

- 4、clocking block的用处?

- 5、使用SystemVerilog避免Testbench与DUT之间竞争冒险的方法有哪些?

- 6、SystemVerilog中有哪些覆盖率(coverage)的类型?

- 7、virtual interfaces的需求是什么?

- 8、解释Abstract classes和virtual methods

- 9、抽象类(abstract class)的用途是什么?

- 10、用来建立scoreboard的数据结构是什么

- 11、 与队列(queue)相比,链表(linked-list)的优点是什么?

- 12、 r a n d o m 和 random和 random和urandom有什么区别?

- 13、列出预定义(predefined)的随机方法。

- 14、packages的用途是什么?

- 15、$cast的用途是什么?

- 16、如何在派生类中调用父类中定义的任务?

- 17、rand和randc有什么区别?

- 18、什么是$root?

- 19、什么是双向约束(bi-directional constraints)?

- 20、在constraint之前“solve”是什么意思?

- 21、不使用randomize方法或rand,生成随机循环数组

- 22、解释pass by ref和pass by value?

- 23、什么是静态变量?

- 24、bit[7:0] sig_1和byte sig_2有什么区别?;

- 25、program和module有什么区别?

- 26、如何在program语句块中实现always语句块?

- 27、modports的用途是什么?

- 28、写一个时钟发生器而不使用always语句块。

- 29、什么是前向引用(forwardreferencing),如何避免此问题?

- 30、什么是循环依赖(circular dependency),如何避免这个问题?

- 31、什么是交叉覆盖率(cross coverage)?

- 32、如何在fork / join中kill一个进程?

- 33、什么是立即断言(Immediate Assertions)和并发断言(Concurrent Assertions)

- 34、如何随机化动态数组对象?

- 35、什么是randsequence?它的用途是什么?

- 36、什么是bin(仓)?

- 37、哪种最适合用来建模事务(transaction)?Struct还是class?

- 38、SV是否比Verilog更random stable?

- 39、如何在不干扰随机数生成器状态的情况下控制约束?

- 40、SV中alias有什么用?

- 41、为什么需要在transaction内部显式实现copy()方法,而不是直接将一个对象赋值给另一个对象?

- 42、在SV中实现struct和union有何不同?

- 43、什么是“this”?

- 44、什么是tagged union ?

- 45、什么是“范围分辨率运算符”(scope resolution operator)?

- 46、bits和logic之间有什么区别?

- 47、$ rose和posege有什么区别?

- 48、什么是覆盖率驱动的验证(coverage driven verification)

- 49、什么是分层验证平台?

- 50、验证环境中的simulation phases是什么?

- 51、如何根据随机索引从queue中选择元素?

- 52、什么数据结构用于在scoreboard中存储数据,为什么?

- 53、什么是流操作符,其用途是什么?

- 54、什么是void function?

- 55、如何确保传递的ref函数参数不被改变?

- 56、initial语句块和final语句块有什么区别?

- 57、如何检查句柄是否存有对象?

- 58、旗语(semaphores)的用处是什么?

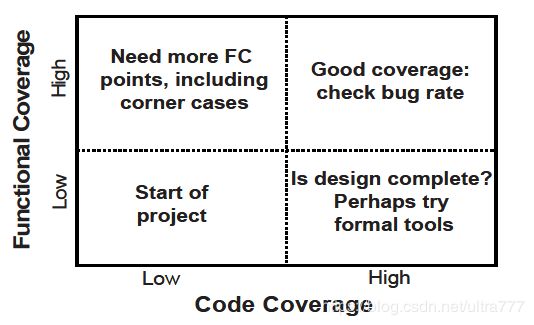

- 59、代码覆盖率(code coverage)和功能覆盖率(functional coverage)有什么区别?

- 60、always_ff的用途是什么?

- 61、什么是static function和automatic function?

- 62、在systemverilog中怎么给数组赋值?

- 63、Systemverilog中有哪些数组类型?

- 64、为什么要使用断言(assertions)?

- 65,如果功能覆盖率超出代码覆盖率,那意味着什么?

- 66、如何在system verilog中指定与timescale无关的#delay?

- 67、super关键字的意义是什么?

- 68、什么是静态变量?

- 69、什么是public声明?

- 70、local声明有什么用?

- 71、如何在clocking block中声明异步信号?

- 72、介绍SystemVerilog中的fork-join?

- 73、什么是chandle ?

- 74、在systemverilog中为function和task添加了哪些功能?

- 75、什么是SystemVerilog中的DPI?

- 76、什么是封装(Encapsulation)?

- 77、如何计算mailbox中的元素数量?

- 78、什么是covergroup?

- 79、什么是super class, abstract class和concrete class?

- 80、什么是Verification plan? What it contains?

- 81、Associative arrays(关联数组)和dynamic arrays(动态数组)之间的区别?

- 82、如何检查随机化是否成功?

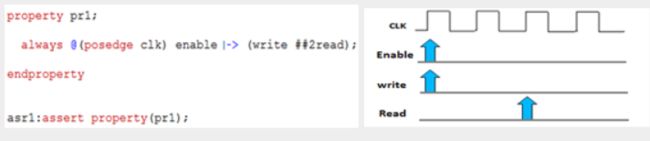

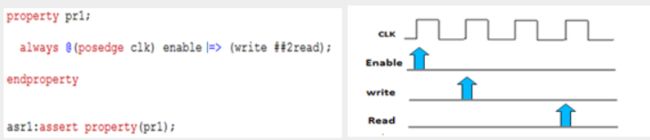

- 83、SVA中的property是什么?

- 84、什么是立即断言(immediate Assertions)?

- 85、什么是断言严重性系统任务?如果我们不指定这些任务会怎样?

- 86、在哪个事件调度区域中将评估并发断言?

- 87、并发断言的主要组成是什么?

- 88、SVA中的连续重复运算符是什么?

- 89、SVA中的goto复制运算符是什么?

- 90、仅在property内部使用的隐含运算符。

- 91、Interface的优点是什么?

- 92、automatic变量在进程中的用处是什么?

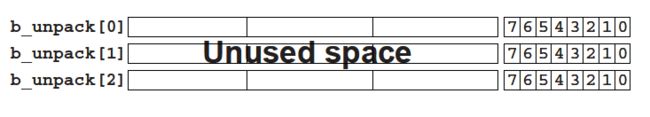

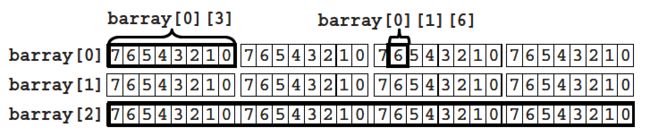

- 93、unpacked array与packed array之间的差异。

- 94、 Dynamic array

- 95、什么时候使用关联数组(Associate array)

- 96、什么是队列(queue)

- 97、什么是变量的Scope和lifetime

- 98、什么是clocking skew

- 99、关于继承两个例子

- 100、定义控制字段

- 101、如果设计工程师和验证工程师在Testbench和DUT中犯同样的错误怎么办?如何能够发现错误?

- 102、如果客户发现了芯片的Bug,该如何调试?如何防止它再次发生?

- 103、解释pass byref和pass by value?

- 104、如何在派生类中调用父类中定义的方法?

- 105、函数重载(function overloading)和函数覆盖(functionoverriding)之间有什么区别?

- 106、数据类型logic,reg和wire有什么区别?

- 107、clocking模块有什么用处?

1、什么是callback?

**callback(回调)**是一种在不更改实际代码的条件下更改为验证组件(例如driver,generator或monitor)行为的机制

class abc_transactor;

virtual taskpre_send();

endtask

virtual taskpost_send();

endtask

task xyz();

this.pre_send();

this.post_send();

endtask : xyz

endclass :abc_transactor

class my_abc_transactor extend abc_transactor;

virtual taskpre_send();

... //This function is implemented here

endtask

virtual taskpost_send();

... //This function is implemented here

endtask

endclass :my_abc_transactor

在上面的例子中,基类abc_transactor具有3个tasks,其中2个被声明为virtual task并且没有具体实现。另一个已完全实现xyz() task会调用这两个virtual task。(Virtual task必须实例化后才可使用,但是静态)

未实现的virtual task称为callback taskes(回调任务)。从基类abc_transactor扩展的子类my_abc_transactor将实现先前未实现的pre_send() task和post_send() task,无需更改xyz() task的代码。

通过这种方式,我们可以将可执行代码注入到函数xyz()task中,而无需对其进行修改。

例如你正在编写将被多个测试环境使用的基类,并且对于每个测试环境,基类中的某些task代码将发生变化,这时就可以将该task/function实现为callback method(回调方法)。

2、什么是factory pattern?

顾名思义,Factory pattern(工厂模式)旨在解决对象创建的问题。

class TOY; // Common data memeber string type;

string type;

virtual function stringget_type();

endclass

class TOY_Tank extends TOY;

function new();

this.string ="Toy Tank";

endfunction

string function stringget_type();

return this.string;

endfunction

endclass

class TOY_Bus extends TOY;

function new();

this.string ="Toy Bus";

endfunction

string function stringget_type();

return this.string;

endfunction

endclass

上面是我们将要创建的对象。我们需要解决的下一个问题是编写TOY_factory类本身。让我们考虑以下情况:我们传递“1”来获得TOY_Tank类的实例,传递“2”来从TOY_Bus类的实例。

TOY_factory如下所示。

class TOY_factory;

Toy my_toy

// Common methods

function toy get_toy(inttype);

if(type == 1)

this.my_toy =new TOY_Tank();

if(type == 2)

this.my_toy =new TOY_Bus();

return this.my_toy;

endfunction

endclass

3、解释数据类型logic、 reg和wire之间的区别

**Wire:**用于连接不同的元件,不存储值,被连续赋值(assign)或者端口(port)驱动

**Reg:**并不意味实际的寄存器,代表Verilog / SystemVerilog中的数据存储元素。保存值,直到将下一个赋值(不是通过assign语句赋值)。可以被综合成触发器,锁存器或组合电路

**Logic:**不能被多驱动,改进了Reg数据类型,可以被连续赋值。

4、clocking block的用处?

interface指定Testbench和DUT通信的信号。但是interface没有明确指定任何时序规则和同步要求。

SystemVerilog添加了clocking block指定任何时序规则和同步要求,以确保Testbench在正确的时间与DUT交互,还可以避免竞争冒险问题。

5、使用SystemVerilog避免Testbench与DUT之间竞争冒险的方法有哪些?

module中的initial语句块调度在Active region,而program中的initial语句块调度在Reactive region。

在program中使用非阻塞赋值来驱动设计信号,在re-NBA区域中对其进行更新。

通过带有**#0** input skews的clocking blocks。

6、SystemVerilog中有哪些覆盖率(coverage)的类型?

- 代码覆盖率(Code coverage):量化执行了多少行代码**(line coverage),执行了哪些路径(path coverage),位变量的值是否覆盖了“0”和“1”(toggle coverage),状态机中的哪些状态和转换已被访问(FSM coverage)**。

- 功能覆盖率(Functional Coverage):和Code coverage不同,Functional Coverage衡量的是设计意图实现的完备性,是主观的。

- 断言覆盖率(Assertion coverage):衡量在测试过程中断言的触发。

7、virtual interfaces的需求是什么?

-

无法在SystemVerilog中的non-module实体内部实例化Interface,但是需要验证环境中的class中驱动Interface。

-

Virtual interface是一种数据类型(可以在一个class中实例化),它保存着对实际接口的句柄(这意味着class可以使用virtual interface来驱动该interface)。

-

Virtua linterface提供了一种可以将验证平台抽象模型与构成设计的实际信号分开的机制。

-

virtual interface的另一个大优点是,类可以在运行时(run time)动态连接到不同的物理接口(physicalinterfaces)。

8、解释Abstract classes和virtual methods

可以从一个通用基类(base class)派生所需的类。基类列出了子类(subclasses)的原型。由于不打算实例化基类,只用来派生子类,因此可以通过将基类指定为virtual class将其抽象化(Abstract)

virtual method为子程序提供了原型。如果abstract class具有virtual methods,则必须重写所有virtual methods才能实例化子类。

这里涉及到OOP的多态(Polymorphism,dynamic method lookup)概念,可以直接从super class中引用那些subclasses的方法。

9、抽象类(abstract class)的用途是什么?

有时候仅需要描述一组对象的属性而无需知道其实际的行为。Abstract classes的方法和构造函数在扩展类中使用,扩展类可以通过Abstract classes共享方法。

10、用来建立scoreboard的数据结构是什么

Queue(队列)

11、 与队列(queue)相比,链表(linked-list)的优点是什么?

队列有固定的顺序,很难将数据插入队列中。但是链表可以轻松地将数据插入任何位置。

12、 r a n d o m 和 random和 random和urandom有什么区别?

$random系统函数每次调用时都会返回一个32位带符号的随机数。

$urandom系统函数每次被调用时都会返回一个32位无符号随机数。

13、列出预定义(predefined)的随机方法。

1.randomize

2.pre_randomize

3.post_randomize

14、packages的用途是什么?

在Verilog中,模块内变量/任务/函数的声明特定于模块(module)。SystemVerilog的package结构允许声明全局变量/任务/函数,从而在modules/classes之间使用。

packages可以包含module/class/function/task/constraints/covergroup等声明,在使用时需要使用范围解析运算符(:或import来访问packages中的内容。

package ABC;

typedef enum {RED, GREEN,YELLOW} Color;

void function do_nothing()

endfunction

endpackage : ABC

import ABC::Color;

import ABC::*; // Import everything inside the package

15、$cast的用途是什么?

通过 $cast 可以将值赋给数据类型不同的变量。特别是在将基类的句柄赋值给扩展类的句柄。

$cast分为static casting和dynamic casting。

static casting示例:

i = int'(10.0-0.1); // static cast convert real to integer

dynamic casting示例:

function int $cast( singular dest_var, singular source_exp );

task $cast( singular dest_var, singular source_exp );

16、如何在派生类中调用父类中定义的任务?

super.task()

17、rand和randc有什么区别?

**rand-随机变量(Random Variable)*在出现所有可能的值之前,可能会出现相同的值。类似于有放回抽签。

randc-随机循环变量(RandomCyclic Variable):,在出现所有可能的值之前,不会出现相同的值。类似于无放回抽签。

18、什么是$root?

top-level scope,可用于引用任意层次中例化的模块

$root.A; // top level instance A

$root.A.B.C; // item C within instance B within top level instance A

19、什么是双向约束(bi-directional constraints)?

默认情况下,SystemVerilog中的约束是双向的。这意味着约束求解器(constraint solver)不遵循约束指定的顺序,同时约束所有变量。例如,(a == 0)->(b == 1)应该作为(!(a == 0)||(b == 1))的所有可能解来求解。

20、在constraint之前“solve”是什么意思?

如果用户要指定约束求解器求解约束的顺序,则用户可以在约束之前通过solve指定顺序。

21、不使用randomize方法或rand,生成随机循环数组

int UniqVal[10];

foreach(UniqVal[i]) UniqVal[i]= i;

UniqVal.shuffle(); //打乱排序

22、解释pass by ref和pass by value?

Pass by value是将参数传递给functions和tasks的默认方法。每个子例程保留该参数的本地副本。如果在子例程声明中更改了参数,不会影响原来的值。

pass by ref中functions和tasks直接访问作为参数传递的指定变量,就像传递变量的指针一样。传递数组给子例程时,使用pass by ref可以避免大量数据的复制。如果不想更改数组值,可以使用const ref。

23、什么是静态变量?

class Transaction;

static int count = 0; // Number of objectscreated

int id; // Unique instance ID

function new();

id = count++; // Set ID, bump count

endfunction

endclass

Transaction t1, t2;

initial begin

t1 = new(); // 1st instance, id=0, count=1

t2 = new(); // 2nd instance, id=1, count=2

$display("Second id=%d, count=%d",t2.id, t2.count);

end

无论创建许多Transaction对象,静态变量count只有同一个。

24、bit[7:0] sig_1和byte sig_2有什么区别?;

byte sig_2是有符号的,而bit [7:0]是无符号的。

25、program和module有什么区别?

**Program是在SystemVerilog中新添加的,**它用于以下目的:

- 分离testbench与DUT

- 有助于确保testbench和DUT没有竞争冒险(race condition)

- 提供了执行testbench的入口点

- 通过(program … endprogram)指定了Reactive Region的调度。

module和program之间的主要区别是:

- program内部不能包含always语句块,而module可以

- program中不能包含UDP,modules或其他program实例,而module可以

- program在调度队列的re-active region中执行,module在active region中执行

- program可以调用modules或其他program中task或function,但是module不能调用program中的task或function。

26、如何在program语句块中实现always语句块?

always @(posedge clk or negedge reset) begin

if(!reset) begin

data <= '0;

end else begin

data <= data_next;

end

end

// Using forever : slightly complex but doable

forever begin

fork

begin

@ (negedge reset);

data <= '0;

end

begin

@ (posedge clk);

if(!reset) data <= '0;

else data <=data_next;

end

join_any

disable fork

end

27、modports的用途是什么?

modports是interface的一部分。modports用于指定与不同模块接口所连接的信号的方向。

interface my_intf;

wire x, y, z;

modport master (input x, y, output z);

modport slave (output x, y, input z);

endinterface

28、写一个时钟发生器而不使用always语句块。

initial begin

clk= 0;

forever#(cycle/2) clk <= ~ clk;

end

29、什么是前向引用(forwardreferencing),如何避免此问题?

有时需要在类声明之前声明另一个类变量。例如,如果两个类各自需要对方的句柄。使用typedef可以解决此问题,为第二个类提供前向声明/引用.

typedef class C2;

class C1;

C2 C;

endclass

class C2;

C1 C;

endclass

30、什么是循环依赖(circular dependency),如何避免这个问题?

过度指定约束求解顺序可能会导致循环依赖,对此没有解决方案,并且约束求解器可能会给出错误/警告,约束求解失败。

int x,y,z;

constraint XYZ{

solve x before y;

solve y before z;

solve z before x;

}

31、什么是交叉覆盖率(cross coverage)?

在多个cover point上同时统计接收到的信息。Cross coverage通过下面的方式指定

covergroup cg;

cover_point_y : coverpoint y ;

cover_point_z : coverpoint z ;

cross_yz : cross cover_point_y,cover_point_z ;

endgroup

32、如何在fork / join中kill一个进程?

disable fork

33、什么是立即断言(Immediate Assertions)和并发断言(Concurrent Assertions)

**立即断言:**当使用“if”或“assert()”执行语句时,立即断言检查表达式是否为真。

**并发断言:**并发断言通过使用“property”持续检查仿真过程中的信号值

interfacearb_if(input bit clk);

logic [1:0] grant, request;

logic rst;

property request_2state;

@(posedge clk) disable iff (rst)

$isunknown(request) == 0; //Make sure no Z or X found

endproperty

assert_request_2state: assert property(request_2state);

endinterface

34、如何随机化动态数组对象?

class ABC;

rand bit [7:0] data [];

constraint cc {

data.size inside{[1:10]}; // Constraining size

data[0] > 5; //Constraining individual entry

foreach(data[i]) // All elements

if(i > 0)

data[i]> data[i-1];

}

endclass

35、什么是randsequence?它的用途是什么?

randsequence由一个或多个式子组成。每个式子均包含名称和列表。列表进一步分为terminals和non-terminals。

non-terminals是根据terminals和其他non-terminals定义的。

terminals是不可分割的项,除了其自身的代码块外,不需要其他定义。最终,每个non-terminals都分解为terminals。列表以“|”分隔,表明一组随机的选择。

randsequence( main )

main : first second done ;

first : add | dec ;

second : pop | push ;

done : { $display(“done”); };

add : { $display(“add”); } ;

dec : { $display(“dec”); } ;

pop : { $display(“pop”); } ;

push : { $display(“push”); };

endsequence

36、什么是bin(仓)?

bin使用**名称(name)和计数(count)记录一组值(value)**或者序列(value transitions)的次数。

如果bin指定一组值,则每次覆盖点与该组中的一个值匹配时,相应的计数就会增加。

如果bin指定序列,则每次覆盖点与序列匹配时,相应的计数就会增加。

program main;

bit [0:2] y;

bit [0:2] values[$]= '{3,5,6};

covergroup cg;

cover_point_y : coverpoint y {

option.auto_bin_max= 4 ; }

endgroup

cg cg_inst = new();

initial

foreach(values[i])

begin

y = values[i];

cg_inst.sample(); //gather coverage

end

endprogram

37、哪种最适合用来建模事务(transaction)?Struct还是class?

transaction为UVM中的sequence item概念,通常需要约束随机数据,因此class更适合于此。Struct仅对数据类型进行重组,而不对方法进行重组。

38、SV是否比Verilog更random stable?

SV允许我们使用受约束的随机测试(constrained-random tests,CRT),这是Verilog不能实现的。通过使用constrained-random data,我们输入有意义的激励。

39、如何在不干扰随机数生成器状态的情况下控制约束?

constraint_mode()

40、SV中alias有什么用?

Verilog的assign赋值是单向赋值(one-way assign),通过RHS变化影响LHS,但是LHS的变化不会影响RHS。SystemVerilog中“alias”可以进行双向赋值。

module byte_rip (inoutwire [31:0] W, inout wire [7:0]LSB, MSB);

alias W[7:0] = LSB;

alias W[31:24] = MSB;

endmodule

41、为什么需要在transaction内部显式实现copy()方法,而不是直接将一个对象赋值给另一个对象?

如果将一个对象赋值给另一个对象,则两个句柄将指向同一对象,这不会复制transaction。

42、在SV中实现struct和union有何不同?

Struct:

initial begin

typedef struct {

int a;

byte b;

shortint c;

int d;

} my_struct_s;

my_struct_s st = '{

32'haaaa_aaaad,

8'hbb,

16'hcccc,

32'hdddd_dddd

};

$display("str = %x %x %x %x ",st.a, st.b, st.c, st.d);

end

Union:与Struct不同,Union的成员均引用同一内存位置。这样,可以在不同时间使用union来容纳不同类型的对象,而无需为每种新类型创建单独的对象。

typedef union {int i; real f; } num_u;

num_u un;

un.f = 0.0; // setvalue in floating point format

当你经常需要以几种不同的格式读写寄存器时,Union很有用。但是更经常使用的还是class。

43、什么是“this”?

当我们使用变量名时,SystemVerilog将在**当前作用域(current scope)中查找它,然后在父作用域(parent scopes)**中查找,直到找到该变量。“This”起到指定作用域的作用

class Scoping;

string oname;

function new(string oname);

this.oname = oname; // classoname = local oname

endfunction

endclass

44、什么是tagged union ?

tagged union包含一个带标记的隐式成员,该隐式成员表示最后一个存储/写入的union成员的名称。如果从非最后写入标记的union成员中读取值,则将显示错误消息。

union tagged {

inti;

realr;

} data;

data data_un;

data_un = tagged i 5; //store the5 in data.i, and set it as the implicit tag.

d_out = data_un.i; //read value

d_out = data_un.r;//ERROR:memeber doesnt match the union's implicit tag

45、什么是“范围分辨率运算符”(scope resolution operator)?

Extern关键字允许在类外定义方法。**范围解析运算符(::)**将方法构造链接到类声明。

class XYZ;

extern void task SayHello();

endclass

void task XYZ :: SayHello();

$Message("Hello !!!\n");

endtask

46、bits和logic之间有什么区别?

bits: 2值逻辑,默认值为0

logic:4值逻辑,默认值为X

47、$ rose和posege有什么区别?

always @(posedge clk)

reg1<= a & $rose(b);

在此示例中,(posedge clk)应用于 r o s e 。 当 b 的 采 样 值 变 为 1 时 , rose。当b的采样值变为1时, rose。当b的采样值变为1时, rose为true。

- 采样值变为1,则$rose返回true,否则返回false。

- 采样值变为0,则$fell返回true,否则返回false。

- 采样值不变,则$stable返回true,否则返回false。

posege返回一个事件(event),而$rose返回一个布尔值,因此它们是不可互换的。

48、什么是覆盖率驱动的验证(coverage driven verification)

覆盖率驱动验证是一种**以结果为导向(resultoriented approach)**的功能验证方法。

根据测试的反馈来开发随机测试激励。初始测试可以使用许多不同的种子,从而创建许多唯一的输入序列。后来,即使使用了新的种子,测试激励也不太可能产生到达所有的设计空间。

当功能覆盖率逐渐接近其极限时,需要更改测试以找到新方法来覆盖设计的未覆盖空间。这就是所谓的“覆盖率驱动验证”。

49、什么是分层验证平台?

50、验证环境中的simulation phases是什么?

Build Phase

-

生成配置:随机化DUT和周围环境的配置

-

构建环境:根据配置规划和连接(Connect Phase)测试平台组件。

Run Phase

- 运行测试:开始测试,然后等待它完成。

Wrap-up Phase

- 报告验证结果

51、如何根据随机索引从queue中选择元素?

int q[$] = {1,2,3,4};

int index[4], out;

foreach(index[i])

index[i] = i;

index.shuffle(); //orindex[i] = $urandom_range (1,4);

foreach(q[i])

out = q[index[i]];

52、什么数据结构用于在scoreboard中存储数据,为什么?

Mailbox或queue。对于每个周期,我们分别从输入和响应中收集并删除这些数据。因此,queue或Mailbox比array更方便。

53、什么是流操作符,其用途是什么?

流操作符<<和>>**将数据块打包为比特流。

- >>运算符从左向右打包数据,

- 而**<<运算符**从右向左打包数据。

54、什么是void function?

没有返回值的函数

55、如何确保传递的ref函数参数不被改变?

const ref

56、initial语句块和final语句块有什么区别?

initial语句块在仿真开始时执行,final语句块在仿真结束时执行

final语句块不能有delay、wait和non-blocking具有时序的语句

57、如何检查句柄是否存有对象?

检查该对象是否已初始化。在SV中,所有未初始化的对象句柄都具有特殊的null值。

assert(obj == NULL)

58、旗语(semaphores)的用处是什么?

semaphore用于控制对资源的访问。

59、代码覆盖率(code coverage)和功能覆盖率(functional coverage)有什么区别?

Functional coverage决定了设计已实现了多少功能。

Code coverage描述设计中代码执行的客观信息

60、always_ff的用途是什么?

使用always语句块对组合逻辑进行建模时,可能会导致latch的生成。SystemVerilog添加了专门的always_comb建模组合逻辑

always_comb

begin

sum = b + a;

parity = ^sum;

end

SystemVerilog添加了专门的always_latch建模锁存器

always_latch

begin : ADDER

if (enable) begin

sum <= b + a;

parity <= ^(b + a);

end

end

SystemVerilog添加了专门的always_ff建模触发器

always_ff @(posedge clk iff rst == 0 or posedge rst)

begin : ADDER

if (rst) begin

sum <= 0;

parity <= 0;

end

else begin

sum <= b + a;

parity <= ^(b + a);

end

end

61、什么是static function和automatic function?

static和automatic的区别在于值是否共享同一块内存空间,默认为静态。

62、在systemverilog中怎么给数组赋值?

int [1:2][1:3]='{'{0,1,2),'{3{4}}};

63、Systemverilog中有哪些数组类型?

Packed数组和unpacked数组。在声明数组时,数组维度在名称之前为packed array,数组维度在名称之后为unpacked array。packed array和unpacked array内存占用是不同的。

int [7:0] c1; //packed array

reg c2 [7:0] //unpacked array

64、为什么要使用断言(assertions)?

断言主要用于检查设计的行为是否正常。可以用来提供功能覆盖信息。断言可以分为立即断言(immediate assertions)和并发断言(concurrent assertions)。

65,如果功能覆盖率超出代码覆盖率,那意味着什么?

code(High)、functional(High)- 活差不多干完了

code(High)、functional(Low) -需要运行更多的仿真或改进测试平台

code(Low)、functional(High)-缺少功能覆盖点

code(Low)、functional(Low) - 需要运行更多的仿真或改进测试平台

66、如何在system verilog中指定与timescale无关的#delay?

#5ns

67、super关键字的意义是什么?

从derived class中使用super关键字来引用base class的成员。

68、什么是静态变量?

在systemverilog中,我们可以在class内部创建一个静态变量。声明为static的变量在其他class之间共享。静态变量通常在声明时完成实例化。

69、什么是public声明?

systemverilog中的对象可以声明为public和private。public声明可从该对象外部访问,默认情况下,systemverilog中的声明是public

70、local声明有什么用?

一旦将数据声明为local,就可以在特定类中对其进行访问。

71、如何在clocking block中声明异步信号?

通过使用modports

interfacearb_if(input bit clk);

logic [1:0] grant, request;

logic rst;

clocking cb @(posedge clk); // Declare cb

output request;

input grant;

endclocking

modport TEST (clocking cb, output rst);//rst is asynchronous signal

modport DUT (input request, rst, outputgrant);

endinterface

module test(arb_if.TEST arbif);

initial begin

arbif.cb.request <= 0;

@arbif.cb;

$display("@%0t: Grant =%b", $time, arbif.cb.grant);

end

endmodule

72、介绍SystemVerilog中的fork-join?

共有三种类型的fork…join

- fork … join:

父进程将阻塞,直到该语句块中所有进程都完成为止。 - fork … join_any:

父进程将阻塞,直到该语句块中的任何一个进程完成为止。 - fork … join_none:

父进程与该语句块中所有进程同时执行。

73、什么是chandle ?

Chandle是一种数据类型,用于存储从DPI传递的指针。chandle的大小取决于机器,初始化值为null。它可用于将参数传递给函数或任务。

74、在systemverilog中为function和task添加了哪些功能?

不需要begin和end。function可以具有void返回类型,task可以具有return

75、什么是SystemVerilog中的DPI?

DPI(Direct Programming Interface,直接编程接口)用于调用C,C ++,System C函数。

76、什么是封装(Encapsulation)?

将数据和方法绑定在一起。

77、如何计算mailbox中的元素数量?

Mailbox用于两个进程之间的通信。

mailbox mbx;

mbx = new(); // Allocate mailbox

mbx.put (data); //Put data object in mailbox

mbx.get (data); // Data updated with new data from FIFO

count = mbx.num(); // To count number of elements is mailbox

78、什么是covergroup?

捕获来自随机激励刺激,封装覆盖率要求。

enum { red, green, blue } color;

bit [3:0] pixel;

covergroupg1 @ (posedgeclk);

coverpoint color;

coverpoint pixel;

AxC: cross color, pixel;

endgroup

79、什么是super class, abstract class和concrete class?

- Super class(父类)是子类可以共享其方法的类(base class/parent class)。

- Abstract class(抽象类)是可以扩展但不能直接实例化的类。使用virtual关键字定义的。

- Abstract class的扩展类是concrete class(具体类)。

80、什么是Verification plan? What it contains?

为(DUT)创建真实的环境以检查行为。验证计划与硬件规范紧密相关,并包含需要验证哪些功能的描述。

验证计划包含:Directed testing、Random testing、Assertion、Hardware andsoftware co-verification

Use of verification IP

81、Associative arrays(关联数组)和dynamic arrays(动态数组)之间的区别?

**关联数组:**具有字符串索引功能,在编译时分配内存。

**动态数组:**在运行时分配内存,构造函数用于初始化动态数组的大小。

82、如何检查随机化是否成功?

if (!obj.randomize())

begin

$display("Error in randomization");

$finish;

end

或者

assert (!obj.randomize())

83、SVA中的property是什么?

- sequences的数量可以组合以创建更复杂的序列。SVA提供了一个关键字"property"来表示这些复杂的序列。

- property的基本语法如下:

property name_of_property;

< test expression > or

< complex sequenceexpressions >

endproperty;

assert_name_of_property: assert property (name_of_property);

84、什么是立即断言(immediate Assertions)?

立即断言是某个判断必须为真的语句,类似于if语句。如果assert求值为X,Z或0,则断言失败。

my_assert:assert(condition1& condition2)

$display("Passed..");

else

$error("Failed..");

85、什么是断言严重性系统任务?如果我们不指定这些任务会怎样?

设置property时,如果不指定property的失败情况,则默认情况下,仿真器应将错误指定为$error严重级别。其他严重级别还包括

$fatal、$error、$warning 和 $info

86、在哪个事件调度区域中将评估并发断言?

并发断言中使用的变量在pre-poned区域中采样,并且在Observe区域中评估断言。这两个区域都紧接在时钟沿之前。

87、并发断言的主要组成是什么?

Sequence

Property

Assert property

88、SVA中的连续重复运算符是什么?

[* ]

指定一个信号或序列在指定的时钟数内连续匹配。

89、SVA中的goto复制运算符是什么?

该运算符指定表达式将匹配指定的次数,而该次数不一定是连续的时钟周期。

x [->4:7]

90、仅在property内部使用的隐含运算符。

91、Interface的优点是什么?

接口是设计重用的理想选择。

1、当信号数量很大时,它减少了信号错误连接的可能性。

2、易于在设计中添加新信号

92、automatic变量在进程中的用处是什么?

有时我们使用循环生成进程,并且在下一次迭代之前不保存变量值。我们应该在fork join语句中使用automatic变量来保存变量。

program automatic test;

task wait for mem(input [31:01 addr, expect data,

output success);

while (bus. addr!== addr)

@(bus . addr);

success = (bus. data== expect data);

endtask

...

endprogram

同时调用此task多次,如果没有automatic修饰符,再次调用wait formem,则第二次调用将覆盖两个参数。

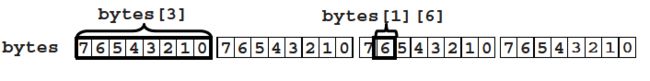

93、unpacked array与packed array之间的差异。

Unpacked array:

bit [7:0]b_unpack[3]; // Unpacked

bit [3:0] [7:0]bytes; // 4 bytes packed into 32-bits

bytes =32'hCafe Dada;

混合packed array和unpacked array:

bit [3:0] [7:0] barray[31; // Packed: 3x32-bit

bit [31:0] Iw =32'h0123 4567; // Word

barray[01 = lw;

barray[0][31 =8'h01;

barray[0] [1][61 =1'h1;

94、 Dynamic array

int dyn[];

initial begin

dyn = new[5];

foreach (dyn[j]) dyn[j] = j;

dyn. size();

dyn. delete();

end

95、什么时候使用关联数组(Associate array)

当集合的大小未知或数据空间稀疏时,关联数组是更好的选择。

关联数组在使用前不会分配任何存储,并且索引不限于整数表达式。

96、什么是队列(queue)

像链表一样,可以在队列中的任何位置添加或删除元素,而无需单步执行前面的元素。

像数组一样,可以直接访问带有索引的任何元素,而无需分配新的数组并复制整个内容。

int j, q2[$]-{3,4), q[$] ={0,2,5};

bit [4:0] ack-que[$];

initial begin

q. insert(1, 1); //{0,1,2,5} Insert 1before 2

q. insert(3, q2); //[0,1,2,3,4,5} Insertqueue in q1

q. delete(1); //f0,2,3,4,5} Delete elem.#1

//These operations are fast

q. push back(8); //(0,2,3,4,8} Insert atback

j= q. pop front; //{2,3,4,8} j=0

foreach (q[ il)

$display(q[i]); //Printentire queue

q. delete(); //{} Delete entirequeue end

97、什么是变量的Scope和lifetime

- Static

- 在时间0分配内存并初始化;

- 存在于整个仿真周期。

- Automatic

- 在调用时分配内存并初始化;

- 存在于某个进程。

- Global Variable在模块外定义,所有模块可以读取

- Local Variable在模块外定义,用于模块内,也可以层次化调用

98、什么是clocking skew

- inputs在时钟之前的skew time采样

- outputs在时钟之后skew time驱动

- 默认input skew为1 Step time,output skew为0.

99、关于继承两个例子

class parent;

int a, b;

task display_c();

$display("Parent");

endtask

endclass

class child extends parent;

int a;

task display_c();

$display("Child");

endtask

endclass

initial begin

parent p;

child c;

c= new();

p=c;

c. display_c();

p. display_c();

//result: Child

//result: Parent

end

没有在父类中声明virtual function,尽管"p"指向"“的句柄,但不允许调用该函数。如果多个子类使用相同的名称定义"display_c()”,则称为多态。

virtual class parent;

pure virtual task display_c();

endclass

class child1 extends parent;

task display_c();

$display("Child1");

endtask

endclass

class child2 extends parent;

task display_c();

$display("Child2");

endtask

endclass

initial begin

parent np[2];

p[0]=new(); //illegal

child1 c1 = new();

child2 c2 = new();

p[0]=c1;

p[1]=c2;

foreach(p[i]) begin

P[i]. display_c();

end

100、定义控制字段

使用枚举类型表示各种激励的类别,从而定义控制字段,控制受约束的变量,提高可读性。

typedef enum {ZERO, SHORT, MEDIUM, LARGE, MAX} simple item delay_e; class simple item extends uvm sequence item;

rand int unsigned addr;

rand int unsigned data;

rand int unsigned delay;

rand simple_item delay edelay kind; // Control field

// UVM automation macros forgeneral objects uvm object `uvm_object_utils_begin(simple_item)

`uvm field int(addr,UVM ALL ON)

`uvm field enum(simple item delay e, delay kind, UVM ALL ON)

`uvm_object_utils_end

constraint delay_order_ c {solve delay kind before delay; }

constraint delay_c {

(delay kind == ZERO)-> delay == 0;

(delay kind == SHORT)-> delay inside { [1:10] }:

(delay kind =-MEDIUM) -> delay inside { [11:99] };

(delay kind == LARGE)-> delay inside { [100:999]};

(delay kind =MAX)- delay == 1000;

delay >=0; delay<= 1000;

}

endclass: simple item

101、如果设计工程师和验证工程师在Testbench和DUT中犯同样的错误怎么办?如何能够发现错误?

- 代码审查(code reviews)和协议检查器(protocol checkers)

- 在多个层次,由不同的人员进行验证(模块级和系统级)

- 客户发现(worst case)

102、如果客户发现了芯片的Bug,该如何调试?如何防止它再次发生?

- 尝试在自己的环境中重现该问题。

- 确定问题之后,在下一个的验证中增加断言或者相应的test case

103、解释pass byref和pass by value?

- **pass by value(按值传递)**是将参数传递给functions和tasks的默认方法。每个子程序保留该参数的本地副本。如果在子程序中更改了参数,不会影响原本数据。

- **pass by reference(按引用传递)**中functions和tasks可以直接访问改变传递的参数,就像传递变量的指针一样。

104、如何在派生类中调用父类中定义的方法?

在派生类中使用super关键字来引用父类的成员。

105、函数重载(function overloading)和函数覆盖(functionoverriding)之间有什么区别?

- 重载是一种允许使用相同名称定义多个成员函数的方法。编译器将选择正确的函数。

- 覆盖是一种允许派生类重新定义从基类继承的成员函数的方法。

106、数据类型logic,reg和wire有什么区别?

**Logic:**过程赋值和连续赋值,可以保存值

**Reg:**过程赋值,可以保存值

**Wire:**连续赋值,不能保存值

107、clocking模块有什么用处?

- 用于指定设计的同步特性

- 避免竞争冒险