FPGA静态时序分析基础

基本概念

Skew: 时钟偏移

Skew表示时钟到达不同触发器的延时差别,Tskew = 时钟到达2号触发器的时刻 - 时钟到达1号触发器的时刻。

Jitter: 时钟抖动

Jitter表示时钟沿到来时刻与标准时刻的差别或者时钟占空比的变化。

Setup time: 建立时间

Setup time表示数据要在时钟沿到来之前保持稳定的最短时间。

Hold time: 保持时间

Hold time表示数据要在时钟沿过去之后保持稳定的最短时间。

timing path:时序路径

静态时序分析首先要把电路分解为一条一条的timing path,起始点是指电路中数据信号被时钟沿锁存的点;而数据信号经过一系列的组合逻辑的通道或者走线后被另外一个时钟沿捕获,这个点被称为终点。信号从起始点到终点所经过的通道就被称为 timing path。

critical path:关键路径

延时最大的那条timing path称为 critical path。关键路径是系统中延时最大的路径,它决定了系统所能达到的最大时钟频率。

slack:时序裕量

如果计算出某条路径的 slack 是正数,说明这条路径的时延是满足要求的;如果计算出某条路径的 slack 是负数,则表示路径上的延时太大了,必须做出修改(修改设计 or 修改约束 or 换芯片),否则包含它的电路不能以预期的频率工作。

时序分析

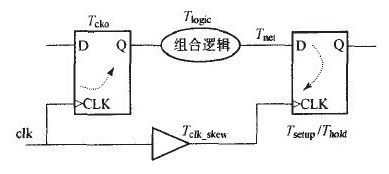

(静态时序分析的典型案例如上图所示)

描述:

第一个FF记为FF1,第二个FF记为FF2;

clk表示时钟,周期为T;

Tcko表示数据被时钟沿捕获后输出的时间;

Tclk_skew表示clk到达两个FF的时间差(Tc2 - Tc1);

Tc2表示clk边沿到达FF2的延时;

Tc1表示clk边沿到达FF1的延时;

Tlogic表示数据经过组合逻辑的延时;

Tnet表示数据走线延时;

Tsetup表示FF的建立时间;

Thold表示FF的保持时间;

Thold+Tsetup是一个触发器的采样窗口时间,在窗口期内,触发器是“直通”的,输入信号在此窗口期间应该保持稳定。

分析:

1 时序路径有几条?

timing path共有一条:自数据从FF1的D端进入被时钟捕获开始(起始时刻),经过组合逻辑及走线,到达FF2的D端,又被时钟捕获为止(终止时刻)。该路径也是该电路的critical path关键路径。

2 如果该电路想要正常工作,需要满足的条件是?

数据信号从起始时刻开始,到达FF2数据端口的延时时间为:Tcko + Tlogic + Tnet;

时钟边沿从起始时刻开始,到达FF2时钟端口的延时时间为:T + Tclk_skew(第二个时钟边沿);

A、FF2想要正常工作需要满足:数据信号要在时钟边沿到来之前Tsetup时间内保持稳定,即数据要早于时钟Tsetup时间:

(Tcko + Tlogic + Tnet) +Tsetup <= (T + Tclk_skew)

信号传输延时时间 + 留出的建立时间裕量 <= 下次时钟沿到来的时间

即:信号传输延时不能太大以至于超过了一个时钟周期。

B、FF2想要正常工作需要满足: 数据信号要在时钟边沿到来之后Thold时间内保持稳定,即

(Tcko + Tlogic + Tnet) >= Thold + Tclk_skew

信号传输延时时间 >= FF的保持时间

即,信号传输延时不能太小以至于小于FF的保持时间。

3 该电路最大工作频率Fmax是多少?

T >= (Tcko + Tlogic + Tnet) + Tsetup - Tclk_skew

Fmax = 1 / T

参考:

1 http://guqian110.github.io/pages/2015/03/18/static_timing_analysis_1_basic.html