基于CS4334的音频DAC学习

---源于一种巧妙运用AVR模拟I2S的技巧

一、假如音频播放设备需要支持的常规音频格式为以下两种情况:

1,44K1 @16bit 双声道,

2,96K @24bit 双声道,

(其它的采样率及位数再另行讨论)。

令fs为音频采样频率,n(I2Sbit)为音频数据位数,A为通道数。有,

BCLK = fs* n(I2Sbit)*A ;

那么针对上面两个模式的BCLK分别为:

1,BCLK = 44.1KHz * 16bit * 2 = 1411.2K BPS,

2,BCLK = 96KHz * 24bit * 2 = 2116.8K BPS,

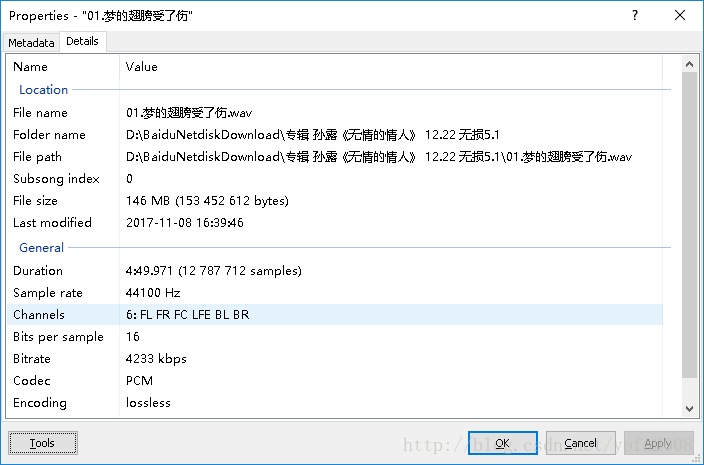

有意思的是这个跟我们看到的文件属性的Bitrate是一致的,如下图:

当然,有时候我们也可能会看到其它的类型,如下图:

显然,这是5.1声道的音源。

假设N为DAC主时钟MCLK与I2S总线数据时钟BCLK的分频系数,且有:

MCLK = BCLK * N (为方便处理及满足分频后时钟精度,N且为整数);

根据经验,16bit时MCLK为fs的256/386倍数以上才能满足基本高保真音质要求;

现在我们来确定当N为整数时,能取到的256/384以上倍数的晶振频率参数;

对于1式,有:

MCLK = 44.1KHz * 16bit * 2 * N ,

当MCLK = 256fs时:MCLK=11.2896MHz,N=8;

当MCLK = 384fs时;MCLK=16.9344MHz,N=12;

对于2式,有:

MCLK = 96KHz * 24bit * 2 * N ,

当MCLK = 128fs时;MCLK=12.2880MHz,N=2.66667,不满足;

当MCLK = 192fs时;MCLK=18.4320MHz,N=4。

在此可以看出,如果打算用AVR来模拟I2S时序的条件是:MCLK时钟不能超过20MHz(5V),一般8bit的AVR也就只能工作在20MHz最大的时钟下,当然超频的不作讨论。

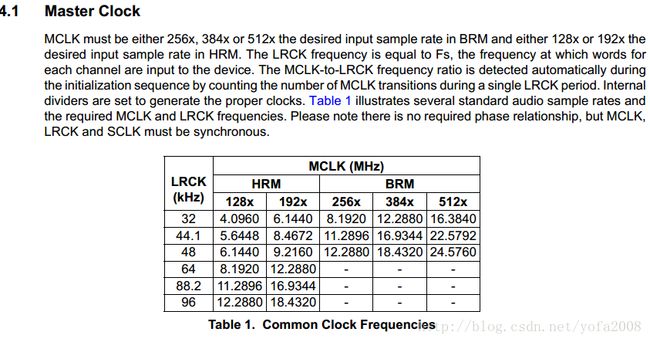

二、反过来,从DAC的角度来看,假如我们使用CS4334这样的一颗DAC,

从它支持的时钟选择参数上看;

MCLK(MHz)

HRM BRM

LRCK(KHz)128x 192x | 256x 384x 512x

44.1 5.6448 8.4672|11.2896 16.9344 22.5792

96 12.2880 18.4320

24bit 24bit | 16bit 16bit。

同样的,一般的音源格式都是44K1和96K,这样要兼容这两个基本的标准又回到了那个老话题:如何实现兼容多个音频源的时钟产生?事实证明这个也已经规避。

三、言归正传接上一篇,原作者将CS4334设置为44K1 24bit这样的音频模式,实际上后面改为了16bit,那么;

MCLK = 44.1KHz * 24bit * 2 * N,

当MCLK = 256fs时;MCLK=11.2896MHz,N=5.3333,

当MCLK = 384fs时;MCLK=16.9344MHz,N=8,

只不过有些怪怪的是一般44.1KHz的音源都是16bit而已。

MCLK = 44.1KHz * 16bit * 2 * N,

当MCLK = 256fs时;MCLK=11.2896MHz,N=8,

当MCLK = 384fs时;MCLK=16.9344MHz,N=12。

CS4334 SCLK有两种工作方式,一是外部audio data processor提供,一种是使用内部产生的SCLK;区别是,使用内部SCLK时,可能同时使用De-Emphasis滤波器;但是MCLK是必须提供的。

这样一来,CS4334的三组时钟如下:

MCLK 16.9344MHz

SCLK 1.4112MHz

LRCLK 44.1KHz

所以AVR的一组分频系统N = 12,这个分频系数很重要。它是与audio data processor进行SPI通信的时钟SCK。

工作在SPI slave的audio data processor在CS片选为高的96(8*N)个时钟周期必须完成下一次SPI数据的装载。

实际上原作者用了一块stm32f103作为SPI从机,且数据格式为16bit;

从这里可以看出,该模拟方案只能应用于16bit的音频解码场景。24bit的话,CS禁能的时间不够。这个优化实验留在下一次尝试,看是否可以把CS时间片增加为32*N来实现。

(全文完)