EBAZ4205 ZYNQ 7Z010 裸机程序NAND固化 JTAG调试方法

简书 https://www.jianshu.com/p/b83c663ecaaa

EBAZ4205 是ebit的控制板,价格便宜。EBAZ4205使用XILINX XC7Z010-1CLG400I soc 包含两个硬核ARM A9,以及ARTIX-7逻辑。板子有一颗128M x 16 bit DDR3 CLK800Mhz,一块128M字节 NAND FLASH,PS 33.333Mhz osc,MII PHY、两个LED、三个排针坐接在PL上。PS上接了两个按键、SDIO、NAND、UART等。注意PHY接在FPGA上。板子电源使用12v,默认板子从三个排针接入电,J4排座没有焊二极管,可以短路后使用J4供电。板子还需要把UART JTAG排针坐焊上。暂时不用SD卡和PHY。

原理图和PCB:https://github.com/Elrori/EBAZ4205

如果使用PHY,参考:https://hhuysqt.github.io/zynq1/ 的方法在第4步建立PHY的EMIO,并把IO引出,再约束。

ZYNQ SOC启动过程以ARM为主,上电后硬件读取PS端IO口确定从NAND、QSPI-FLASH、SD Card还是JTAG启动。板子默认从NAND启动,为了软件调试和下载NAND,须从JTAG启动。

0. 准备板子,接上UART,XILINX JTAG

1. 从JTAG启动:上电前将 电阻R2578靠近NAND的一端接到地,再接上电源没有打印输出或者config done led不亮就说明从JTAG启动。

2. 新建该器件的vivado工程,创建原理图、点击“+” 检索zynq7 processing system添加,去掉AXI:

3. 外设IO设置使用NAND UART1,按照下图:

4. MIO配置,默认:(如使用PHY需勾选ENET0,并使用EMIO从PL引出,参见 githubio)

5. 时钟配置,使用FCLK_CLK0用于PS给PL时钟,按照下图:

6. DDR3配置, DDR3使用镁光128M16的代替,有效数据宽16bits(单DDR3),数据线PCB延迟设置为0.106,按照下图:

7. SMC时序,NAND时序按照下图:

8. 点击OK,右击原理图zynq7 点create ports,再检查可用性。右键source中的设计创建封装和输出,按照下图:

9. 新建verilog 顶层top_pl.v用于点灯。设计包含如下:

引脚约束,xdc文件内容:(PHY引脚参见 githubio)

set_property PACKAGE_PIN W13 [get_ports {led_r}]

set_property PACKAGE_PIN W14 [get_ports {led_g}]

set_property IOSTANDARD LVCMOS33 [get_ports {led_r}]

set_property IOSTANDARD LVCMOS33 [get_ports {led_g}]

10. generate bitstream 产生 .bit文件

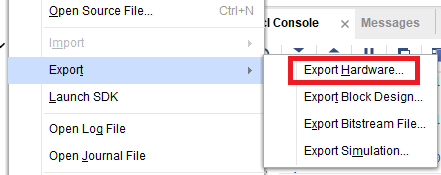

11. file->export hardware,勾上.bit文件:

12. file->launch SDK,在SDK中新建如下,然后设置工程名fsbl,点next选择FSBL模板

13. 同样的方法在SDK中再新建一个工程 名为app并使用hello world模板,裸机程序就在这个工程中,而fsbl工程用于初始化ddr等。保存编译产生两个elf即 app.elf fsbl.elf

14. 制作BOOT.bin用于固化到NAND。BOOT.bin由fsbl.elf top_pl.bit app.elf三个文件组成。

同样的方法加入top_pl.bit 和 app.elf,partition type选择数据文件,请务必按顺序。

点击创建镜像完成产生BOOT.bin

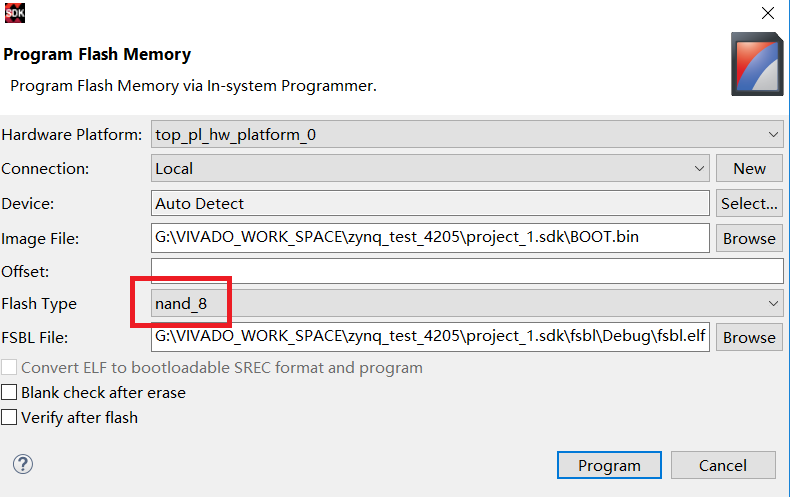

15. 下载BOOT.bin到NAND,按照下图设置:

16. 断电在上电可以看到最后一个行打印输出Hello World说明裸机程序运行成功,LED交替闪烁说明FPGA配置完成。如果需要软件调试上电必须按照步骤1做一遍,然后直接debug app工程,注意debug 选项中ps初始化选上。

以上

操作省略较多 仅参考备忘用途