7天搞定FPGA精录&总结Episode.2 实例入手,体验Robei【基于Robei与Verilog HDL】

我感觉吧,在当前的高校圈,大佬很多,但是很多都没有好好在学习。其实我个人对学习的定义是很严格的,即使是做出了优秀的作品,目的是获得分数和虚荣,也不能叫做学习。

我在读书的时候,看到有工程师这样谈:任何包括集成电路设计在内的工程问题的学习,初学者都会经历感兴趣→迷茫→头疼→失去兴趣→悟道→加深兴趣→痴迷的过程。笔者曾经热爱理论数学的学习,但是因为种种原因没有进入自己心仪的大学。现在看来也不失为一件好事。曾经的经历让我更加坚信任何工作的精通一定需要经过十分困难的修炼,没有一蹴而就和一夜成名,需要我们坚持。此外毕竟信息化社会竞争压力巨大,我们的爱好也需要向生存压力妥协。当然说到这里也不得不承认这样的心思让我永远也成为不了大佬,这也是一个遗憾。

FPGA入门的第二天,通过四个简单的实例来引入如何仅使用Robei进行数字电路的一个软件级逻辑级的开发。由于硬件级的验证需要辅助实际的开发板,所以此处先略去不谈。事实上如果能得到稳定的正确的仿真波形,接下来也就是绑定管脚和下载到板子的机械化工作了,这些在未来EDA的发展过程中相信迟早会成为计算机自动完成的工作。

有些很简单或者已经被验证过类似的模块开发可以不用仿真,但是这类情况比较罕见。所以,通常的开发至少需要一个module模块文件和一个testbench模块构成代码和仿真的基础部分。下面四个样例中,与门电路的设计会详细总结有关软件操作的过程,而ALU由于是CPU计算的基本单元,所以会重点分析其设计思路。

以下给出Robei EDA设计过程中遇到的常见问题和解决方案:

(1)我为什么仿真之后看不到波形?

Robei的模型有四种类型:“module”,“model”,“testbench” 和“constrain”。 如果你想仿真之后看波形应该将顶层的仿真模块类型设置成“testbench”。同时,testbench的模块输入端口类型应为“reg”,输出类型应为“wire”。

如果以上都设置正确,确认一下是否先点"Compile"再点"Run".

(2)出现syntax error?

一般是语法错误,一般是拼写或符号错误、缺少语句、缺少符号等。需要根据错误信息提示的代码行数检查错误。常见的错误类型:1. 如果begin···end不完整,缺少end,错误信息会不能定位出错位置,检查错误时注意begin和end是否一一对应。2. 如果漏掉分号,错误信息也难以定位出错语句,检查错误时注意代码中有没有漏掉分号。3. Robei软件会自动添加module和endmodule,所以不需要自己在code里添加,如果添加了反而会出错。4.文件和变量命名的时候不要使用减号等特殊字符,可以使用下划线。5. 注意分号等符号都要用英文字符,不要使用中文字符。

(3)error: xxx is not a valid l-value in traffic?

说明xxx的Datatype应该是reg类型,但是你设置成了wire类型。

(4)reg xxx; cannot be driven by primitives or continuous assignment.

说明xxx应该是wire类型的,你设置Datatype为reg类型,而且在assign语句中使用了。请修改为wire类型或者不要采用assign语句赋值。

(5)Unable to open input file.

可能是:1.点击运行仿真之前没有点击编译,编辑完测试文件后,先保存、编译,然后再点运行仿真。2.文件命名不符合规范,EDA类工具对命名有一些规定,因此,建议在对文件和变量等命名时: ①只使用英文字母、数字、下划线,不要用空格或其他特殊字符 ②不要与verilog语言的关键词相同(如module) ③必须以英文字母开头,不能以数字或下划线开头

(5)输出信息中存在乱码.

安装路径或工程文件路径的文件夹名有中文或特殊字符。路径的各文件夹中不要有中文、空格、特殊字符,可以有下划线。

(6)Datasize are not equal.

连线的两个端口的位宽不一致。Robei软件中,添加子模块时,需要注意: ①子模块的端口属性是只读模式,不能直接修改; ②需要打开子模块工程进行修改,修改完保存; ③保存完后回到刚才的设计,用delete删除旧的子模块,然后重新添加。

(7)duplicate declaration.....

检查端口或变量是不是声明定义了多次。在Robei软件中设置端口属性后,软件会根据端口属性生成端口声明代码,不需要自己手动再声明一次。

(8)If you want to see the waveform, make sure you have the "Type" changed to "testbench"

只有testbench测试文件才能运行仿真,设计文件不能直接仿真看波形。新建testbench测试文件有两种

一、与门电路的设计:

P.S.此部分我们重点介绍软件操作,具体电路知识参看有关数字电路及数字系统设计方面的参考书

按照以下数字顺序步骤进行操作,可完成与门电路设计到仿真的过程,如依照操作产生错误,可参见上述总结的常见问题方案

1、打开软件,点击File,新建module,命名andgate,选择入端口2个,出端口1个,点击OK,之后点击p0到p2三个出入口,在右端栏里面改名字为a、b和y,如果喜欢可以改成自己的幸运色。完成后如下图

2、点击File,选择save保存,建立一个andgate的文件夹,文件名也命名为andgate,后缀默认.model即可

3、点击Code,键入核心代码 assign y=a&b; 然后再点击保存。之后点击View中的Codeview,即可看到软件自动生成的完整代码如下图所示

4、点击倒数第六个图标,也就是一个向下的箭头指着一块板子的图标,如果代码没有错误就会显示Gnerate文件,如果有错误,依据提示修改对应的行的错误即可

5、回到Graph,右键点击andgate模块,点击create test,然后系统会自动创建Testbench文件,此时务必将写测试代码前空白文件进行保存,且一定要和andgate.model保存在同一路径下

6、选择Current中的andgate模块,左键点击添加到test模块内部去,将对应的p0、p1、p2和a、b、y用线在图画上直接连接,其中线的按键在倒数第八个按键,完成后如下图所示

7、进入Code,键入如下图所示的testbench代码,加以激励,同样的保存方式和codeview查看方式得到完整代码。这里需要强调两点:

①Testbench一般是用initial语句给予一次激励即可,同时利用#10代表下一个语句延后上一个语句多少时间执行

②Testbench中initial语句测试激励完成后,在end之前需要添加&finish;语句

8、保存。之后点击倒数第六个图标验证test代码,没有错误的话点击倒数第五个Run simulation图标,运行成功的话会显示产生波形文件。之后再点击代数第四个图标,则可以看到仿真波形,通过右边栏选择你想要显示的参数即可,具体操作完成如下图

9、依据数字电路的知识,通过波形图分析自己的设计是否满足要求,满足则设计成功,保存退出即可。这样一个十分简单的数字电路模型也就设计完成了

二、4bit计数器的设计:

操作方式与上述类似,以下补充几点不一样的新东西:

1、计数器是一个时序逻辑电路,需要有clock时钟输入,因而在代码的编写中,always语句块不要忘记添加时钟上升沿触发条件,也即:always @(posedge clock)

2、输出count由于是4bit的计数器,相当于可以计数十进制的1-16,于是在创建好模块后,改动输出端口的名字时同时需要改动DataType为reg,Datasize为4,表示4bit的寄存器变量输出

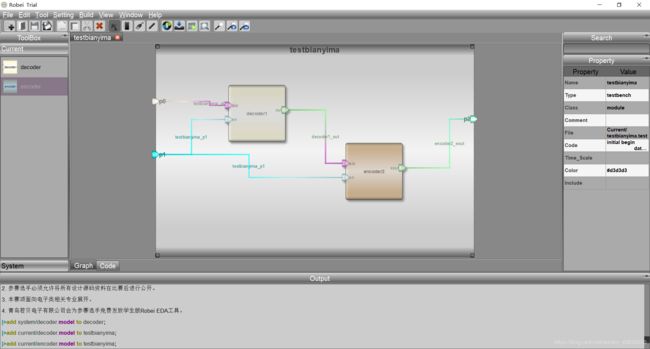

三、简易编译码器的设计:

操作方式与上述类似,以下补充几点不一样的新东西:

1、优先编码器常用于处理最高优先级请求时控制中断请求,将多个二进制数压缩成更少数目输出的电路算法。具体的8-3编码器真值表如下所示:

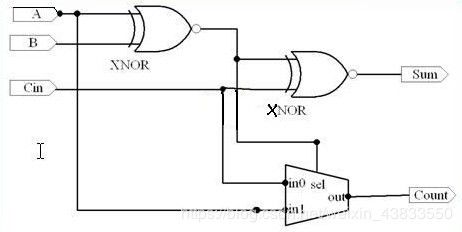

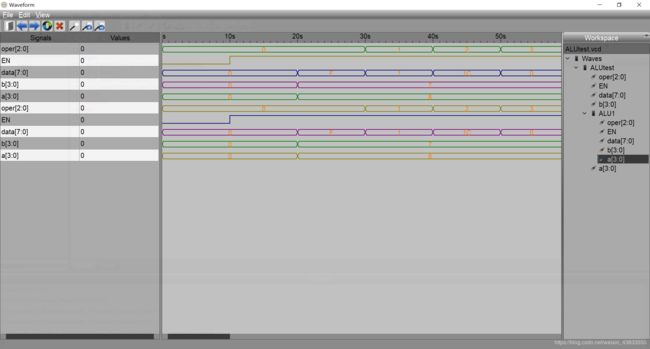

2、译码器则是反向进行操作,这里不需要再通过真值表的方式倒回,只需除了en0外直接给移动一位就好了。最好的方式是利用assign赋值语句和条件赋值语句结合直接搞定:assign out=(en)?(1< 3、en是一个使能信号,声明时信息为Datasize为1的wire线网类型变量 4、testbench中,因为我们对电路的链接是先decoder然后encoder的方式,所以需要通过各个不同的三位激励,各自延迟#1的时间,不要忘记最后的$finish; 四、ALU模块开发: 由于ALU在芯片底层设计中的重要性,本节会详细分析简易ALU的设计思路 1、ALU的概念: ALU是算术逻辑单元,能实现多组算术运算和逻辑运算的组合逻辑电路,算术逻辑单元的简称是ALU。 算术逻辑单元(Arithmetic&logical Unit)是中央处理器(CPU)的执行单元,是所有中央处理器的核心组成部分,由"And Gate"(与门) 和"Or Gate"(或门)构成的算术逻辑单元。 主要功能是进行二位元的算术运算,如加减乘(不包括整数除法)。基本上,在所有现代CPU体系结构中,二进制都以补码的形式来表示。 2、ALU的特点: ALU用以计算机指令集中的执行算术与逻辑操作,某些处理器中,将ALU切分为两部分,即算术单元 (AU)与逻辑单元(LU)。某些处理器包含一个以上的AU,如,一个用来进行定点操作,另一个进行浮点操作。(个人计算机中,浮点操作有时由被称为数字协处理器的浮点单元完成)。 通常而言,ALU具有对处理器控制器、内存及输入输出设备的直接读入读出权限。输入输出是通过总线进行的。输入指令包含一个指令字,有时被称为机器指令字,其中包括操作码,单个或多个操作数,有时还会有格式码;操作码指示ALU机要执行什么操作,在此操作中要执行多少个操作数。 3、ALU的基本原理: 计算机运行时,运算器的操作和操作种类由控制器决定。运算器处理的数据来自存储器;处理后的结果数据通常送回存储器,或暂时寄存在运算器中。 数据运算器的处理对象是数据,所以数据长度和计算机数据表示方法,对运算器的性能影响极大。70年代微处理器常以1个、4个、8个、16个二进制位作为处理数据的基本单位。大多数通用计算机则以16、32、64位作为运算器处理数据的长度。能对一个数据的所有位同时进行处理的运算器称为并行运算器。如果一次只处理一位,则称为串行运算器。有的运算器一次可处理几位 (通常为6或8位),一个完整的数据分成若干段进行计算,称为串 并行运算器。运算器往往只处理一种长度的数据。有的也能处理几种不同长度的数据,如半字长运算、双倍字长运算、四倍字长运算等。有的数据长度可以在运算过程中指定,称为变字长运算。 按照数据的不同表示方法,可以有二进制运算器、十进制运算器、十六进制运算器、定点整数运算器、定点小数运算器、浮点数运算器等。按照数据的性质,有地址运算器和字符运算器等。 操作运算器能执行多少种操作和操作速度,标志着运算器能力的强弱,甚至标志着计算机本身的能力。运算器最基本的操作是加法。一个数与零相加,等于简单地传送这个数。将一个数的代码求补,与另一个数相加,相当于从后一个数中减去前一个数。将两个数相减可以比较它们的大小。 左右移位是运算器的基本操作。在有符号的数中,符号不动而只移数据位,称为算术移位。若数据连同符号的所有位一齐移动,称为逻辑移位。若将数据的最高位与最低位链接进行逻辑移位,称为循环移位。 运算器的逻辑操作可将两个数据按位进行与、或、异或,以及将一个数据的各位求非。有的运算器还能进行二值代码的16种逻辑操作。 乘、除法操作较为复杂。很多计算机的运算器能直接完成这些操作。乘法操作是以加法操作为基础的,由乘数的一位或几位译码控制逐次产生部分积,部分积相加得乘积。除法则又常以乘法为基础,即选定若干因子乘以除数,使它近似为1,这些因子乘被除数则得商。没有执行乘法、除法硬件的计算机可用程序实现乘、除,但速度慢得多。有的运算器还能执行在一批数中寻求最大数,对一批数据连续执行同一种操作,求平方根等复杂操作。 4、ALU的设计实现: 随着手持式个人通讯系统等的发展,低压低功耗高吞吐量电路的需求越来越多,因此低功耗微处理器和元件的设计已经变成了主流。ALU是微处理器最重要的组成部分,其中全加器电路是所有运算电路的基本单元,设计低功耗快速加法器单元是获得低功耗高速运算电路的关键。ALU单元的设计标准是多种多样的,晶体管数量显然是一个主要的关注点,因为它极大的影响了功能单元ALU的设计复杂性。另外两个重要的却又相互矛盾的因素是功耗和速度。与功耗降低相关的一个因素是电路能工作的最低电压, 还有一个是晶体管的数量,而全加器晶体管的数量又极大的影响了ALU单元的晶体管数量,因此全加器的设计也是ALU设计中必须重点考虑的一部分。对于已有的全加器的设计按照种类来分有静态CMOS电路,动态电路,传送管和传输门逻辑。其中全静态CMOS电路是最传统的,但需要28个管子。动态电路能极大的减少晶体管的数量但是短路功耗却很大;使用传送门逻辑是一个可选的降低电路复杂性的方案。在中基于传送门和反向器的全加器设计中各使用了20和16个晶体管,为了得到更少管子的全加器,在中基于XOR/XNOR的传送门逻辑电路组成的全加器只用了14个管子,在中,介绍了一个基于传输管的静态能量恢复全加器(SERE),它只使用了10个管子,且不管它自称的功耗小,这个设计相比同类的设计来讲速度比较慢,同时这个设计不能用来级连,因为在低电压下工作时有多阀值损失问题。在中一种新的基于选择电路的10管全加器设计被提出,然而这个设计也同样有多阀值损失问题,以至于不能在低电压级连模式下正确的工作,前面提到的10管全加器都是基于图1的原理来的。文中的ALU单元将采用一种新的10管全加器,它可以减轻阀值损失问题,这个设计可以在使用少量管子的情况下组成快速的并行加法器(RCA)同时保持较低的能量损耗,另外,这个设计可以在较低的工作电压下正确运行。具体实例参加下图: 5、ALU的FPGA和Robei建议设计注意事项: ①加法运算包含2种类型,一种是不带进位的加法器,另外一种是带进位的加法器。不带进位的加法器的公式: ⑥32位的ALU:我们将4个8位的ALU进行级联,第一个输出的D连到下一级的F,最终的ALU的D连接到顶层的D引脚。第一个ALU的F连接到顶层模块的F。op都连接到顶层的op引脚上,A,B和R按照高低位进行连接。P.S.这个设计需要先注册Robei否则不允许使用这么多模块进行仿真。 6、图例设计过程: 此外,还有很多适合初学者入门的练习题,大多的都可以用作参考,个人认为这些代码已经是几十年前就弄出来的了,我们大可直接复制粘贴已有的东西,把精力都用在模块层级的设计上。此外Robei EDA是提供了一个System包含这些基本的原件已经设计好的模板,也可以通过使用他们来学习、练习或者用于以后的电路设计工作。

{D,R}=A+B

②带进位的可以进行加法器级联,实现更高位数的串行加法运算。带进位的加法器的公式:

{D,R}=A+B+F

③减法运算也包含2种类型。不带借位的减法运算:

{D,R}=A-B

④带借位的减法运算:

{D,R}=A-B-F

⑤16位的ALU:这个设计中使用之前设计好的8位ALU模块,把输入的16位信号拆分为两个8位信号,经过8位ALU处理后再组合成最终的16位输出信号。split模块设计:该模块的功能是把输入的16位数据分解为两个8位数据。merge模块设计:该模块的功能是把两个8位数据组合为一个16位数据。