AI芯片的另一条路

来源:半导体行业观察

在先进工艺和架构的协同下,芯片的性能在过去几年获得了爆发性的增长,尤其是在最近几年火热的人工智能行业,这个取得的成就是有目共睹的。

据OpenAI在2018年年中发表的报告,自 2012 年以来,人工智能训练任务中使用的算力正呈指数级增长。人们对于算力的需求增长也超过 300,000 倍。作为对比,如果是以摩尔定律的速度,这个数字只会是12倍的增长。在他们看来,正是这些硬件性能的跨越式突破,才成就了现在的AI产业。

自2012年以来,AI对算力的要求(source:OpenAI)

Open AI的报告进一步指出,成本考量和物理学特性等因素将会压制传统AI硬件性能的上升势头。但市场对AI算力的需求仍然处于增长期,为此探索新的硬件方案成为了AI芯片供应商亟待解决的问题。不少厂商也都另辟蹊径从多个方向解决广为人知的“冯诺依曼瓶颈”。

在鲲云信息科技有限公司创始人牛昕宇博士(以下简称牛博士)看来,一个不同于过往的新架构,是解决当前AI问题的正确之选。他同时也指出,目前的AI芯片行业,需要变革的不仅仅是架构。

亟待变革的AI芯片架构

对AI芯片行业有所了解的读者都应该知道,现在统治人工智能芯片市场的厂商主要是英伟达,依靠GPU优秀的并行计算能力和CUDA生态,这家本来只是做显卡的厂商在人工智能时代大放异彩。

除了英伟达之外,拥有庞大部署量的英特尔至强处理器和声名在外的谷歌TPU和特斯拉FSD也是AI芯片市场一个不可忽略的角色。这些处理器有一个共同特点,那就是他们无一例外采用了指令集架构处理器。

经典指令集架构图

这些架构在实际应用中不能发挥人工智能芯片的全部算力潜力,为此牛博士指出,在算力需求猛增的AI时代,需要一种新的芯片架构,这主要是由以下两个原因决定的:

从硬件架构上看,指令集架构芯片中有部分芯片面积用于支持指令控制。更关键的问题在于,在指令执行过程中,计算单元在多数时间内处于等待的状态:等待计算所需数据的到来。从这个角度看,指令集架构下的算力并没有被充分发挥出来给到用户。

另一方面,如上图右边所示,一个标准的五级指令集的每一条指令都要经过读取、解码、执行、读写内存和把数据写到寄存器里面去这五个步骤。在这些步骤中,只有执行这一步骤是在执行真正的计算。其他部分都是在做指令的读取和解码这样的功能。虽然可以通过指令流水降低计算单元闲置,不过在实际执行过程中,受限于指令间的依赖、以及指令间协同的时钟不确定性,指令内部的计算单元会出现闲置等挑战。

牛博士举例说到,英伟达T4在Batch=128或Batch最高的测试环境下,按照其官网公布的指标去比对几个网络实际的使用算力,得出的结果是峰值算力的7%到30%左右。这意味着产品有很大部分的性能还不能完全发挥出来。

“如果大家都在类似架构下竞争,在接近的芯片利用率前提下,芯片公司的产品升级最后会变成依赖制程工艺和软件生态的比拼。而且,对比P4与T4产品的实测性能可以发现,随着峰值算力的增加,芯片的实际利用率有所降低”,牛博士补充说。

从目前的市场发展上看,包括英伟达在内的多家AI芯片厂商都在沿着上述技术路线演进,但从当前制程工艺的发展和材料本身的特性限制看来,继续大幅提升峰值算力意味着更高的芯片成本,而随着峰值算力降低的芯片利用率意味着给到用户的实测算力并不会等比例线性提升。这与当前AI应用客户更高算力性价比的需求是相背而行的。换而言之,寻找一个新的AI芯片架构迫在眉睫。

“数据流架构或许会是一个不错的选择”,牛博士说。

根据他的观点,所有的计算架构需要保证一个核心需求:加减乘除等计算操作能够按照编程需求按特定次序完成对特定数据的计算。与传统的冯·诺依曼架构或控制流体系结构进行对比,数据流架构并没有指令相关的指令控制与执行单元。数据流架构依靠数据流动次序,而不是指令执行次序保证计算执行顺序,从而将计算与数据搬运重叠,以实现更高的吞吐量和更低的延迟。

定制数据流计算示例

“在指令集架构中,由于指令协同的不确定性,计算与数据读写无法深度重叠,部分时间计算单元处于等待数据状态,从而导致闲置计算单元和芯片利用率的下降。而数据流架构中每个时钟下所有计算单元的状态是确定的,计算单元无需等待其它单元的计算,从而消除计算资源闲置。”牛博士表示。“这就像一个交响乐团,当乐团中每个人都按照统一的拍子进行演奏时,而且每个人在每个拍子下的动作是确定的,乐团中的乐器之间并不需要相互等待,可以按照自己的节拍并行的演奏,就会协作完成一首曲子。这就像数据流架构中计算单元间的协作关系:通过精确的时钟进行协作,而并不存在先后依赖关系,所以无需等待。”牛博士补充说。

据介绍,数据流架构支持时钟级的精确计算,让每个数据流动及计算在每个时钟都可精确预计,从而支持将数据流动与计算深度重叠,消除计算单元闲置;于此同时,数据流架构中没有指令,从而破除了指令集架构的控制冗余以及等待指令读取译码带来的计算单元闲置问题,进一步提升芯片利用率。此外,数据流架构中一个数据流流水线中可深度整合大量计算单元,从而打破指令集架构中峰值算力提升与芯片利用率的冲突问题:通过不断加深数据流流水线,可以在提升峰值算力同时,不降低流水线中计算单元闲置时间。”

正是因为数据流架构拥有如此多的优势,包括Wave Computing、SambaNova和Groq在内的多家公司投入了这个领域的研发,值得一提的是Groq的初创团队还是由谷歌TPU的核心成员创立,由此可以看到数据流架构的前景。

当然,鲲云科技创始团队自1994年就开始探索数据流架构在各个垂直领域的开发和落地,在数据流技术上具有深厚的积累,自然是这个架构的积极支持者。也正是在这个背景下,团队创立了鲲云科技,从零开始探索针对深度学习的数据流架构,也就是CAISA。

AI芯片能力≠芯片峰值算力

在架构类似的情况下,峰值算力是一个可以简单快速估算芯片实测性能的指标,也是在AI芯片设计中重点关注的指标。然而近几年,提升峰值算力的发展方向将人工智能芯片的发展推向了另一个极端:峰值算力(或每瓦的峰值算力)已经成为评价一颗AI芯片性能的单一指标,导致大量AI芯片研发资源投入到如何把峰值算力推高。

然而对于用户来说,峰值算力其实并不是他们的本质需求。

“用户真正关心的是AI芯片的实测算力,而不完全是峰值算力。峰值算力并不能直接释放给用户,真正释放给用户的要乘上一个系数,叫做芯片利用率”,牛博士说。“峰值算力指标假设每个芯片内部计算单元每个时钟都处于计算状态,而现有指令集架构在运算执行中计算单元存在闲置”,牛博士强调。

以英伟达T4加速卡为例,常用的识别、检测和分割的算法ResNet50、SSD-ResNet50和U-Net Industrial,在Batch=128或者最高性能的情况下,可以分别获得32.1%、7.5%、11.9%的芯片利用率,这意味着在实际应用中,只有7%到32%的峰值算力转换为实测性能释放给用户,当中带来的芯片性能浪费是显而易见的。

T4加速卡的测试结果

“为了让用户获得更高的性能,除了持续提高峰值性能以外,芯片利用率的提升会是一个更好的方案,因为这会在不增加芯片成本的情况下,大幅提升芯片的实测性能。这也是鲲云科技新推出的CAISA 芯片正在努力的方向”,牛博士说。

这是一款采用28nm工艺打造的芯片,搭载了四个CAISA 3.0引擎,具有超过1.6万个MAC(乘累加)单元,峰值性能可达10.9TOPs。而通过PCIe 3.0×4接口与主处理器通信,同时具有双DDR通道,可为每个CAISA芯片提供超过340Gbps的带宽。

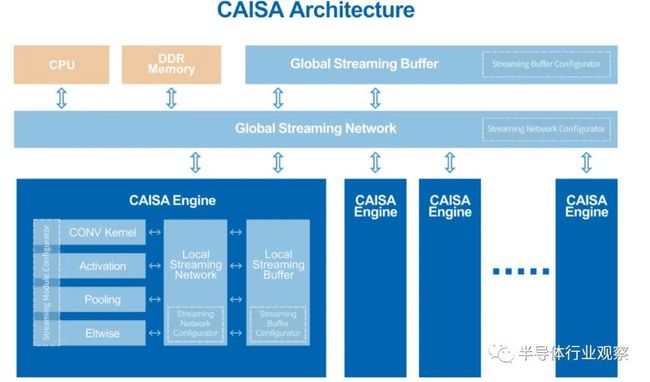

CAISA芯片架构图

作为一款面向边缘和数据中心推理的人工智能芯片,CAISA芯片可实现最高95.4%的芯片利用率。这就让他们在既满足客户在价格和功耗方面需求的同时,还能为客户提供更强的算力,提高了性价比。而之所以能做到如此高的芯片利用率,与鲲云科技的CAISA 3.0数据流架构有莫大的关系。

CAISA3.0架构图

在文章前面我们提到,鲲云科技首席科学家Wayne Luk陆永青院士从1994年就开始将数据流架构应用到各个垂直领域。经历了前十几年的发展积累,到鲲云科技于2016年成立并在FPGA上实现交付,与客户的交流迭代之后,完成了此次全新的架构升级。

来到CAISA3.0中,数据计算与数据流动的重叠,压缩计算资源的每一个空闲时钟;通过算力资源的动态平衡,消除流水线的性能瓶颈;通过数据流的时空映射,最大化复用芯片内的数据流带宽,减少对外部存储带宽的需求。上述设计使CNN算法的计算数据在CAISA3.0内可以实现不间断的持续运算,最高可实现95.4%的芯片利用率,在同等峰值算力条件下,可获得相对于GPU 3倍以上的实测算力,从而为用户提供更高的算力性价比。

相比旗舰款Xavier加速卡,搭载CAISA芯片的星空加速卡X3可以最高提供4.12倍实测性能提升;而与T4相比,鲲云科技也能提供最高3.91倍实测性能提升。这都是超高的芯片利用率提升所带来的。得益于这个利用率,过往通过提升峰值性获得更高性能而带来的高成本问题,也迎刃而解。

X3 vs Xavier 芯片利用率对比图

X3 vs Xavier 性能对比图

X3 vs Xavier 延时对比图

X9 vs T4 芯片利用率对比图

X9 vs T4 性能对比图

X9 vs T4 延时对比图

也许很多人并没有理解这个3.91倍背后的意义,让我们举个现有的例子来对比说明一下。

AI从业人员都知道,英伟达为了展现其T4的实力,在其官方网站上公布了这个加速卡跑在不同网络模型下的性能指标。作为AI芯片行业的风向标,任何一款芯片想要说明自己的实力,只需要跑和T4一样的网络,然后公布相关的Benchmark就可以如愿以偿。早前被英特尔收购的Habana就是这样做的。根据Habana所公布benchmark性能,相比于T4官网指标(最新官网指标为5415FPS),通过更高的峰值算力,Habana的产品提供了2.85倍实测性能提升。正是因为在实测性能上取得的领先,最终获得Intel的青睐,让他们以20亿美元的估值被收购。

通过这个例子,我们也可以看到鲲云科技这个数字的真正价值。

在这个高性能芯片的支持下,鲲云科技打造了高算力性价比的AI计算平台星空加速卡系列,并推出了X3和X9两款产品。

其中星空X3加速卡是搭载单颗CAISA 芯片的数据流架构深度学习推断计算平台,为工业级半高半长单槽规格的PCIe板卡。得益于其轻量化的规格特点,X3加速卡可以与不同类型的计算机设备进行适配,包括个人电脑、工业计算机、网络视频录像机、工作站、服务器等,满足边缘和高性能场景中的AI计算需求。相较于英伟达边缘端旗舰产品Xavier,X3可实现1.48-4.12倍的实测性能提升。

星空X3加速卡

X9加速卡为搭载4颗CAISA 芯片的深度学习推断板卡,峰值性能43.6TOPS,主要满足高性能场景下的AI计算需求。同英伟达旗舰产品T4相对,X9在ResNet-50, YOLO v3等模型上的芯片利用率提升2.84-11.64倍。在实测性能方面,X9在ResNet50可达5240FPS,与T4性能接近,在YOLO v3、UNet Industrial等检测分割网络,实测性能相较T4有1.83-3.91倍性能提升。在达到最优实测性能下,X9处理延时相比于T4降低1.83-32倍。实测性能以及处理延时的大幅领先,让数据流架构为AI芯片的发展提供了提升峰值性能之外的另一条技术路线。

据了解,目前星空X3加速卡已经推出市场,而星空X9加速卡将于今年8月推出市场。

全球首个数据流AI芯片背后

从行业的现状看来,鲲云科技是全球首家推出数据流AI芯片,并且提供第三方实测benchmark的中国芯片企业。这是前文说到的Wave Computing、SambaNova和Groq等国外明星初创企业所不能达到的成就。而通过数据流网络中算子的不同配置和组合,鲲云科技的CAISA芯片更可支持到绝大多数的CNN算法,并能让开发者轻易地将模型迁移到这个平台上。。

能做到这样,是其架构和软件相互协同获得的成果。

CAISA3.0架构可以通过流水线动态重组实现对不同深度学习算法的高性能支持。通过CAISA架构层的数据流引擎、全局数据流网、全局数据流缓存,以及数据流引擎内部的人工智能算子模块、局部数据流网、局部数据流缓存的分层设计,在数据流配置器控制下,CAISA架构中的数据流连接关系和运行状态都可以被自动化动态配置,从而生成面向不同AI算法的高性能定制化流水线。在保证高性能的前提下,支持用户使用基于CAISA3.0架构的计算平台实现如目标检测、分类及语义分割等广泛的人工智能算法应用。

“专为CAISA3.0架构配备的RainBuilder编译工具链支持从算法到芯片的端到端自动化部署”,牛博士强调。而在RainBuilder编译工具链的支持下,用户和开发者无需了解架构的底层硬件配置,简单两步即可实现算法快速迁移和部署。

RainBuilder架构图

据透露,RainBuilder编译器可自动提取主流AI开发框架(TensorFlow,Caffe,Pytorch,ONNX等)中开发的深度学习算法的网络结构和参数信息,并面向CAISA结构进行优化;工具链中的运行时(Runtime)和驱动(Driver)模块负责硬件管理并为用户提供标准的API接口,运行时可以基于精确的CAISA性能模型,实现算法向CAISA架构的自动化映射,同时提供可以被高级语言直接调用的API接口;最底层的驱动可以实现对用户透明的硬件控制。RainBuilder工具链使用简单,部署方便,通用性强,可以让用户快速和低成本的部署和迁移已有算法到CAISA硬件平台上。

回顾计算行业的发展,不同的应用催生了不同的处理器架构。早期PC的出现,让X86架构和Intel名扬天下;近十年移动设备的出现,又推动了Arm架构和高通的蓬勃发展。

现在,我们进入了AI时代,也许一个属于数据流处理器和鲲云科技的时代,从这刻开始正式上演。

未来智能实验室的主要工作包括:建立AI智能系统智商评测体系,开展世界人工智能智商评测;开展互联网(城市)云脑研究计划,构建互联网(城市)云脑技术和企业图谱,为提升企业,行业与城市的智能水平服务。

如果您对实验室的研究感兴趣,欢迎加入未来智能实验室线上平台。扫描以下二维码或点击本文左下角“阅读原文”

![]()

![]()