根据黑金 AX301 手册,数码管位选信号命名为 SEL[5:0],其中 SEL[5] 对应最左边的数码管,而SEL[0] 对应最右边数码管;作为约定,在下面的描述中我们对应的称之为数码管 5 和数码管 0。数码管的段选信号被命名为 DIG[7:0];DIG[7] 为小数点 DP,DIG[6] 为数码管 g 段,DIG[0] 为 a 段,其他类推即可。

由于数码管的段选信号是共用的,理论上是不可能同时显示六个不同字符的,但由于人眼的视觉残留现象,只要我们很快的依次显示每一个数字,就可以欺骗人眼达到显示多位数字的目的,假设需要显示的数字为 123456,其二进制 BCD 码为 24'b 0001_0010_0011_0100_0101_0110 可以简写成 24'h123456,实现的流程如下:

- 首先使能数码管 0,关闭其他数码管:SEL = 6'b111_110,显示的数值为 6,DIG = {1,DIG[6:0]} = 7'b1_000_0010;

- 第二步使能数码管 1,关闭其他: SEL = 6'b111_101,显示的数值为 5,DIG = 7'b1001_0010;

- 同理 SEL = 6'b111_011,显示 4 DIG = 7'b1001_1001;

- 同理 SEL = 6'b110_111,显示 3 DIG = 7'b1011_0000;

- 同理 SEL = 6'b101_111,显示 2 DIG = 7'b1010_0100;

- 同理 SEL = 6'b011_111,显示 1 DIG = 7'b1111_1001;

- 回到步骤一。

晶振的频率显然超过了三极管的频率上限,我们通过设计一个分频器来产生一个不超过 1KHz 的扫描信号;这个分频器的原理在于设计一个每个时钟周期加 1 的计数器,如果累计器是 3 位的,那么它的数值变化就如下表所示:

counter[2:0]:000,001,010,011,100,101,110,111,

counter[0]: 0, 1, 0, 1, 0, 1, 0, 1,------------- 50MHz

counter[1]: 0, 0, 1, 1, 0, 0, 1, 1, ------------- 25MHz

counter[2]: 0, 0, 0, 0, 1, 1, 1, 1, ------------- 11.5MHz

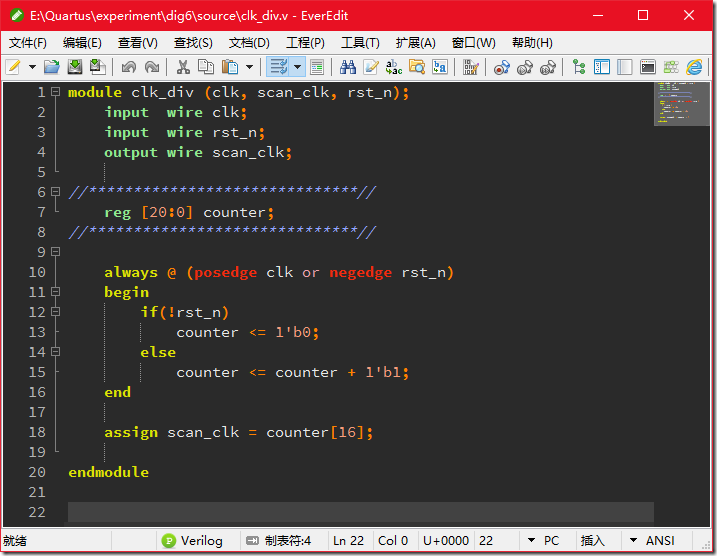

分频器的具体的代码如下:

通过实验发现设置为 19、18、17 时数码管都会出现严重的闪烁现象,而 16 这个值正常,计算便可以得出这时的频率大约为 400Hz

f =50MHz/( 2^(16+1)) = 50_000_000 Hz/(2^17) = 381.469726 Hz ~~ 381.47 Hz

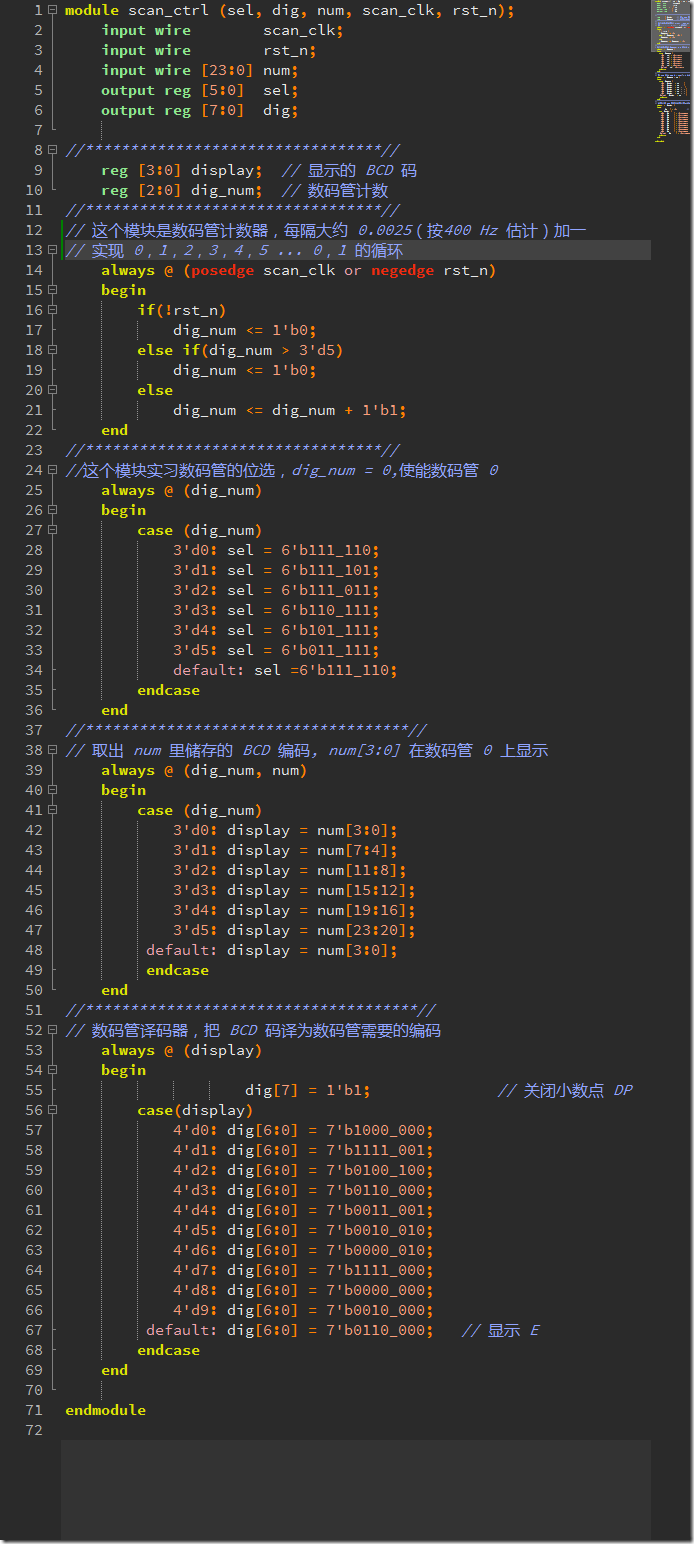

下面是控制模块的代码,这个模块实现的功能比较复杂:

- 首先实现一个 0 ~ 5 不断循环的低速计数器 dig_num 作为参考值。

- 当 dig_num 为 0 时,点亮数码管 0,同时分离 num[3:0](6)到 display。

- 当 dig_num 为 1 时,点亮数码管 1,分离 num[7:4](5)到 display。

- 当 dig_num = 2 ~ 5 时,情况同上。

- 任何时候把 display 中的值转化为数码管显示所需的段选信号。

注意:Verilog 语法 十进制 'd、十六进制 'h、八进制 'o、二进制 'b 在本例中非常容易弄错

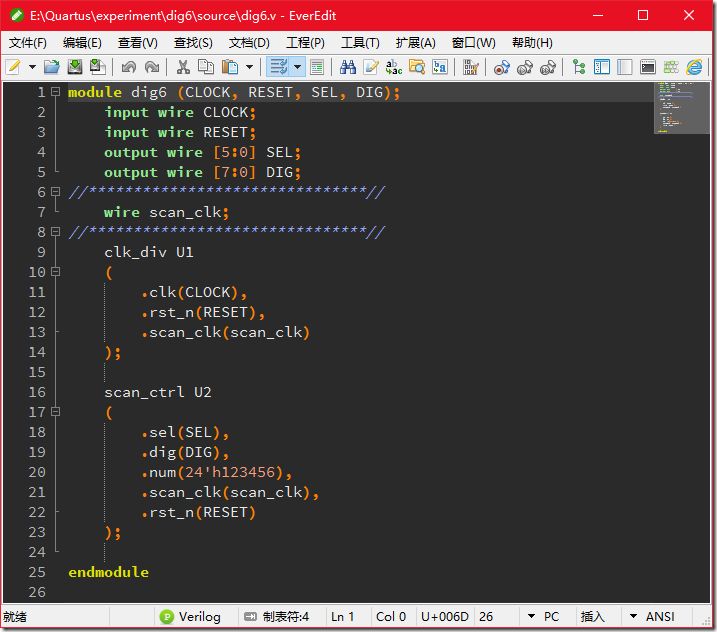

最后是顶层模块,模块中指定了要显示的字符:

读者如果觉得同时显示六个字符有些困难,可以选择先点亮两个,再来依次增加即可。