GTX高速收发器Transceiver概述与收发共同特征(UG476)

目录

本文主要对xilinx的GTX核的使用手册进行阅读,UG476,可以对照着原文再看我的博文。

Ch1.Transceiver and Tool Overview

2.1Reference Clock Input Structure

2.2Reference Clock Selection and Distribution

2.3Reset and Initialization

2.3.1Reset Modes

2.3.2CPLL Reset

2.3.3QPLL Reset

2.3.4TX Initialization and Reset

2.3.5GTX/GTH Transceiver TX Reset in Response to Completion of Configuration

2.3.6GTX/GTH Transceiver TX Reset in Response to GTTXRESET Pulse

2.3.7GTX/GTH Transceiver TX Component Reset

2.3.8RX Initialization and Reset

2.3.9GTX/GTH Transceiver RX Reset in Response to Completion of Configuration

2.3.10GTX/GTH Transceiver RX Reset in Response to GTRXRESET Pulse

2.3.11GTH Transceiver RX PMA Reset

2.3.12GTX/GTH Transceiver RX Component Resets

2.4Power Down

2.5Loopback

2.6DRP:Dynamic Reconfiguration Port

2.7Digital Monitor

发射端:GTX高速收发器Transceiver之发射端Transmitter(UG476)

Ch1.Transceiver and Tool Overview

xilinx的7系列FPGA根据不同的器件类型,集成了GTP、GTX、GTH以及GTZ四种串行高速收发器,可以支持多种协议如PCI Express,SATA,JESD204B等。

四种收发器主要区别是支持的线速率不同,图一可以说明在7系列里面器件类型和支持的收发器类型以及最大的收发器数量[1]。

![]()

图1

GTXE2_CHANNEL/GTHE2_CHANNEL代表一个GTX/GTH transceiver channel。

GTXE2_COMMON/GTHE2_COMMON代表一个QPLL。

a) Xilinx的7系列FPGA随着集成度的提高,其高速串行收发器不再独占一个单独的参考时钟,而是以Quad来对串行高速收发器进行分组;

b)一个Quad包括四个GTX/GTH transceiver channel、一个QPLL组成,两个差分输入参考时钟接口;

c)每一个串行高速收发器称为一个Channel,其主要由channel PLL 、TX和RX组成。

以XC7K325T为例,GTX在FPGA内部如图二所示:

![]()

图2

对于每一个Quad的结构图如图三:

![]()

图3

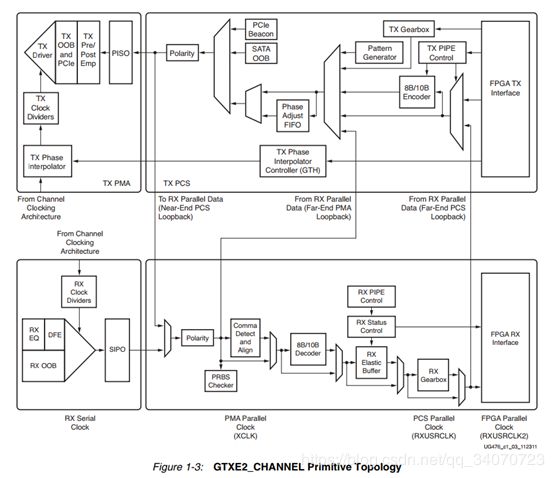

对于每一个串行高速收发器,其包含了发送部分和接收部分,内部结构图4:

图4

发送端和接收端功能独立,均由PMA(Physical Media Attachment,物理媒介适配层)和PCS(Physical Coding Sublayer,物理编码子层)两个子层组成。

其中PMA子层包含高速串并转换(PISO)、预/后加重、接收均衡、时钟发生器及时钟恢复等电路。PCS子层包含8B/10B编解码、缓冲区、通道绑定和时钟修正等电路。

GTX发送端处理流程:首先用户逻辑数据经过8B/10B编码后,进入一个发送缓存区Phase Adjust FIFO,该缓冲区主要是PMA子层和PCS子层两个时钟域的时钟隔离,解决两者时钟速率匹配和相位差异的问题,最后经过高速Serdes进行并串转换(PISO parallel-in serial-out),有必要的话,可以进行预加重、后加重(Pre/Post Emp)。值得一提的是,如果在PCB设计时不慎将TXP和TXN差分引脚交叉连接,则可以通过极性控制来弥补这个设计错误。接收端和发送端过程相反,相似点较多,这里就不赘述了,需要注意的是RX接收端的弹性缓冲区(RX Elastic Buffer),其具有时钟纠正和通道绑定功能。

Ch2.Shared Features

2.1Reference Clock Input Structure

2.2Reference Clock Selection and Distribution

1.参考时钟整体架构

每个Quad的时钟结构如图所示[1]:

![]()

红色方框表示两个外部差分参考时钟源。

绿色方框是来自其他Quad的参考时钟输入,7系列FPGA支持使用相邻(南北方向)Quad的参考时钟作为当前Quad的参考时钟。

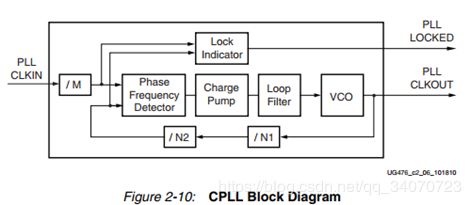

多路参考时钟源经过一个选择器之后,分两路进入QPLL和CPLL,其中蓝色方框是QPLL,黄色方框是CPLL。

CPLL与QPLL的区别

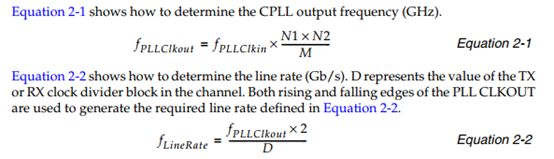

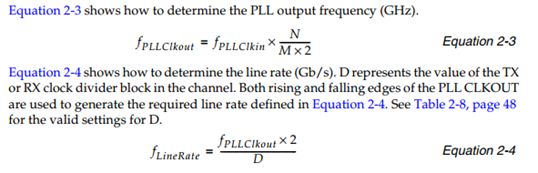

对于每个GTX Channel来说,可以独立选择参考时钟,可以选择QPLL或者CPLL,区别在于两者支持的线速率不同,QPLL支持的线速率高于CPLL。 CPLL支持的线速率1.6GHz到3.3GHZ之间;QPLL来说,GTX支持的线速率分两档,Lower Baud支持5.93GHz~8.0GHz,Upper Baud支持9.8GHz~12.5GHz,对于GTH则不分档位,支持的线速率为8.0GHz~13.1GHz。

2.Quad或Channel时钟选择

因为每一个Quad有两个外部参考时钟,因此对于每一个Quad来说,可以选择两个不同的参考时钟,每一个CHANNEL的接收端和发送端都可以独立选择参考时钟,如图所示:

![]()

如果用户需要使用其他Quad的参考时钟源来作为当前Quad的参考时钟,在满足下面三个条件的情况下可以使用:

1. 只能使用当前Quad上方的Quad的参考时钟;

2. 只能使用当前Quad下方的Quad的参考时钟;

3. 一个Quad的参考时钟源不能驱动超过3个Quad的收发器(只能驱动当前Quad和上下方相邻两个Quad);

满足上面的条件,就可以把其他Quad的参考时钟配置成当前Quad的参考时钟,如图九所示,注意图中红色方框表示相邻的Quad:

![]()

3.各参考时钟介绍

(1)红色方框部分是两个差分参考时钟输入,每个外部参考时钟的输入必须经过IBUFDS_GTE2源语之后才能使用。IBUFDS_GTE2 软件原语对应外部输入参考时钟缓冲器,对输入参考时钟进行处理。

原语使用例如:

IBUFDS_GTE2 tx_ref_inst(

.I (tx_ref_clk_p), //双极性输入

.IB (tx_ref_clk_n),

.CEB (1'b0), //1就关闭此缓冲器

.ODIV2 (), //二分频输出

.O (tx_ref_clk) //正常输出

);

(2)CPLL

CPLL的输入参考时钟选择:

CPLL内部框图:

(3)QPLL

对于CPLL和QPLL:

手册还给出了多种协议下特定通道速率的参数设置。相关参数设置,端口描述与属性 就不写了。

使用模式:可以动态改变的CPLL或者QPLL的配置,也可以动态的在CPLL和QPLL之间切换,具体怎么换手册给出了步骤(P54/P60)。

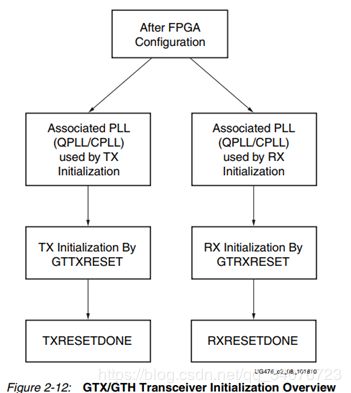

2.3Reset and Initialization

TX和RX初始化顺序:

1.初始化PLL

2.初始化数据路径PMA+PCS

顺序框图:

两种复位类型:

1.初始化时的复位:设备上电时,复位以进行初始化

2.模块复位,单独部分的复位

复位信号都是高电平有效。

2.3.1Reset Modes

两种复位模式:

1. Sequential mode:随着复位状态机顺序复位各个部分。

RESETDONE上升沿标志复位完成。

2. Single mode:仅复位单个部分。

GTX/GTH收发信机初始化复位必须使用顺序模式。除TX复位外,所有组件复位均可在顺序模式或单模式下操作,TX复位只能在顺序模式下操作。

2.3.2CPLL Reset

CPLL在参考时钟有效前must be powered down using the CPLLPD port。然后对每个通道的CPLL复位。

有三个接口控制,

2.3.3QPLL Reset

完全与CPLL相同。

2.3.4TX Initialization and Reset

分为TX PMA和TX PCS两个复位区域。TX初始化和复位只能在顺序模式下操作。

使用复位状态机

(图中,GTTXRESET High到WAIT Until GTTXRESET From High to Low 的意思就是要等待一个GTTXRESET脉冲电平就进入复位过程)

2.3.5GTX/GTH Transceiver TX Reset in Response to Completion of Configuration

进行TX复位前需要满足一定的条件,本节主要讲要满足条件中关于 配置的 部分。

满足:

1. GTRESETSEL must be Low to use sequential mode.

2. GTTXRESET must be used.

3. TXPMARESET and TXPCSRESET must be constantly driven Low during the entire

reset process before TXRESETDONE is detected High.

4. GTTXRESET cannot be driven Low until the associated PLL is locked.

如果在配置时重置模式默认为顺序模式,那么在配置完成后等待至少500 ns后,才可以进行复位C/QPLLRESET和GTTXRESET。

建议使用CPLL或QPLL中的PLLLOCK信号来释放GTTXRESET从高到低,已启动TX复位过程。如图2-16所示,需要注意的是,PCS的复位需要在TXUSERRDY为高电平的时候才能复位。

TXUSERRDY为高电平要满足一定的条件:

1. All clocks used by the application including TXUSRCLK/TXUSRCLK2 are shown as

stable or locked when the PLL or MMCM is used.

2. The user interface is ready to transmit data to the GTX/GTH transceiver.

2.3.6GTX/GTH Transceiver TX Reset in Response to GTTXRESET Pulse

进行TX复位前需要满足一定的条件,本节主要讲要满足条件中关于 GTTXRESET脉冲 部分。

TXPMARESET_TIME和TXPCSRESET_TIME可以通过DRP端口静态设置或重新编程设置,在应用GTTXRESET之前调整所需的复位时间。

使用GTTXRESET时必须满足以下条件:

1. GTRESETSEL must be driven Low to use sequential mode.

2. TXPMARESET and TXPCSRESET must be driven constantly Low during the entire

reset process before TXRESETDONE is detected High.

3. The associated PLL must indicate locked.

4. The guideline for this asynchronous GTTXRESET pulse width is one period of the

reference clock.

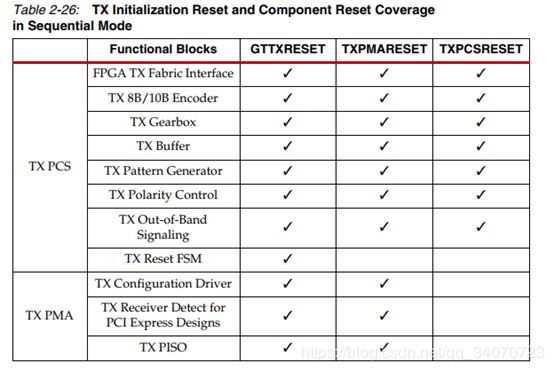

2.3.7GTX/GTH Transceiver TX Component Reset

TX PMA和TX PCS可以单独复位。在TXPMARESET或TXPCSRESET过程中,GTTXRESET必须在复位完成之前持续低电平。

生成一个TXPMARESET脉冲以启动PMA复位,状态机在PMA复位后会接着复位PCS。

生成一个TXPCSRESET脉冲以启动PCS复位。状态机只复位PCS。

接着讲了GTTXRESET、TXPMARESET、TXPCSRESET都能复位哪些发射机组件:表2-26。

表2-27讲了在一些情况下建议进行什么样的复位。

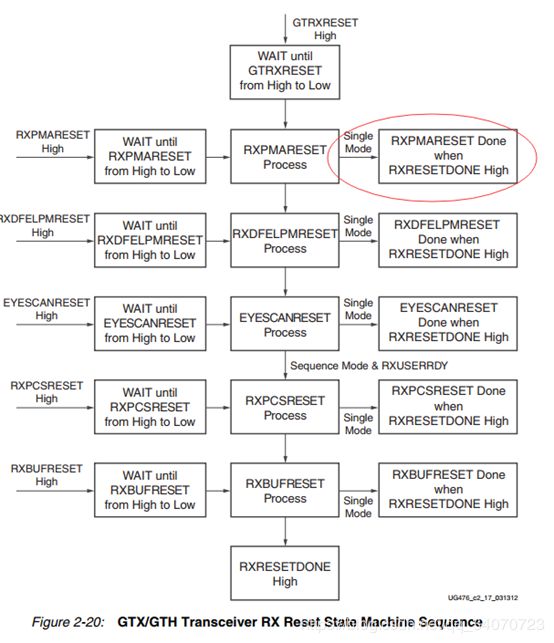

2.3.8RX Initialization and Reset

RX复位可以工作在2种模式。顺序与单模式。

1.顺序模式

与TX的情况相同,使用状态机,状态机可以从头触发,也可以从中间某一个状态触发。

2.单模式

RX的各个模块可以单独触发相应信号以单独复位。

复位状态机(复位过程同样是需要有信号先变高在变低即产生一个脉冲来启动复位);单模式复位情况下,以下图红圈里的为例,产生一个RXPMARESET脉冲仅仅复位PMA,并不会复位后面的模块。

2.3.9GTX/GTH Transceiver RX Reset in Response to Completion of Configuration

和TX相同,都需要满足一些条件,然后进行整个RX复位过程

It is recommended to use the associated PLLLOCK from either the CPLL or QPLL to release GTRXRESET from High to Low as shown in Figure 2-21.

上图是GTX/GTH Receiver after FPGA Configuration,此外还描述了仅在GTH的收发器的情况,具体就不细说了。

2.3.10GTX/GTH Transceiver RX Reset in Response to GTRXRESET Pulse

和TX相同,在产生GTRXRESET脉冲前 都需要满足一些条件,在这里就不罗列了。

这个异步GTRXRESET脉冲宽度的准则是参考时钟的一个周期。

同上一小节一样,除了适用GTX/GTH的,还有只有在GTH的情况。

2.3.11GTH Transceiver RX PMA Reset

当用户希望进行RXPMARESET时,应该满足的条件(针对GTH)。

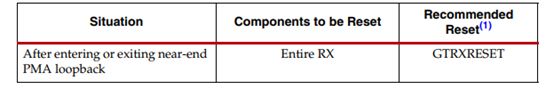

2.3.12GTX/GTH Transceiver RX Component Resets

内容安排与TX类似。

表2-30和表2-31还总结了GTX/GTH收发器RX可用的所有复位以及顺序模式和单模式下受相应影响的组件。这些重置都是异步的。

表2-32列出了在一些情况下建议进行什么样的复位。

表我就不放了。

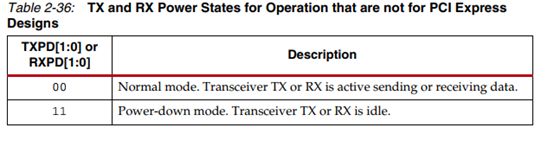

2.4Power Down

GTX/GTH收发机提供不同级别的功率控制。

每个方向的每个通道都可以使用TXPD和RXPD分别关闭。

CPLLPD端口直接影响CPLL,QPLLPD端口直接影响QPLL。

表2-33定义了power-down ports.

表2-34定义了power-down属性.设置power-down的时间等。

PLL Power Down

在初始配置和通电期间,CPLL在参考时钟有效之前必须使用CPLLPD端口断电。如果参考时钟停止,CPLL应该关闭电源。用CPLL时可以把QPLL Power Down,。用QPLL 时,在配置完成后至少500 ns后才能Power Down,然后等待参考时钟有效在开启QPLL。

从Power Down状态恢复,意味着PLL LOCK高电平时,相应的PLL才有效。

TX and RX Power Down

当TX和RX功率控制信号在非PCI Express实现中使用时,TXPD和RXPD可以单独使用。同样,当这些接口在non中使用时PCI Express应用程序只支持两种电源状态,如表2-36所示。当使用这种断电机制时,确保如下:

• TXPD[1] and TXPD[0] are connected together.

• RXPD[1] and RXPD[0] are connected together.

• TXDETECTRX must be strapped Low.

• TXELECIDLE must be strapped to TXPD[1] and TXPD[0].

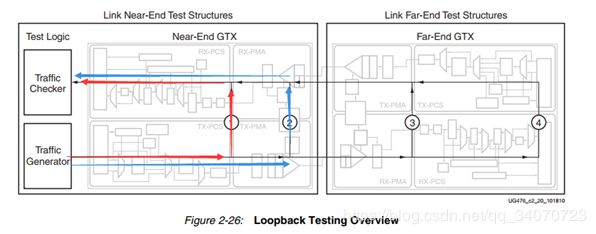

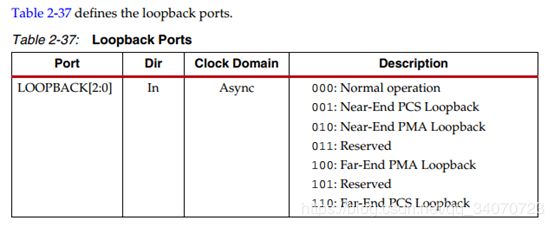

2.5Loopback

环回模式是收发器数据路径的特殊配置,数据流发出去又发回来。通常,传输特定的数据内容,然后进行比较以检查错误。图2-26演示了具有四种不同环回模式的环回测试配置。

分为近端和远端,

环回测试可以在开发过程中使用,也可以在部署的设备中用于故障隔离。所使用的流量模式可以是应用程序流量模式,也可以是专用的伪随机位序列。每个GTX/GTH收发器都有一个内置的PRBS生成器和检查器。

并分别讲了四种模式需要注意的一些设置,

Near-End PCS Loopback (path 1 in Figure 2-26)

Near-End PMA Loopback (path 2 in Figure 2-26)

Far-End PMA Loopback (path 3 in Figure 2-26)

Far-End PCS Loopback (path 4 in Figure 2-26)

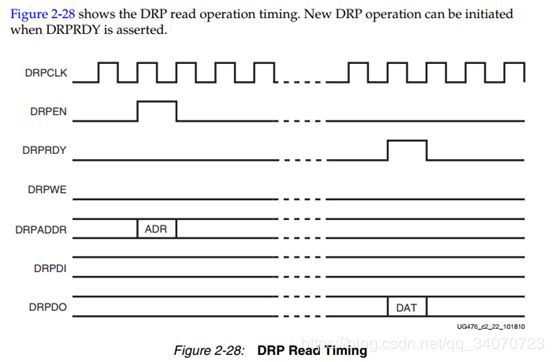

2.6DRP:Dynamic Reconfiguration Port

DRP动态重新配置端口是用来动态改变GTXE2_CHANNEL/GTHE2_CHANNEL

和GTXE2_COMMON/ GTHE2_COMMON原语的。

包括地址总线DRPADDR,有用于读取(DRPDO)和写(DRPDI)配置数据到原语的分离数据总线。

表2-38显示了GTXE2_CHANNEL/GTHE2_CHANNEL的DRP相关端口。

表2-39显示了GTXE2_COMMON/GTHE2_COMMON的DRP相关端口。和2-38基本一样。

Usage Model

分别给出了读操作写操作的时序。

2.7Digital Monitor

这部分是指RX的两种均衡器模式,LPM和DFE的观测

Power-efficient adaptive linear equalizer mode called the low-power mode (LPM)

低功耗自适应线性均衡器模式

5-tap decision feedback equalization(DFE)

5-tap决策反馈均衡器

输出端口DMONITOROUT包含所选循环的当前代码。

讲了相关的端口以及属性,以及如何捕获数字监视器输出数据DMONITOROUT,并对输出数据进行解释。

参考文献:

- Xilinx-7Series-FPGA高速收发器使用学习—概述与参考时钟篇https://blog.csdn.net/ladywn/article/details/52836818

- UG476-Xilinx-7Series-FPGA高速收发器使用学习—TX发送端 https://blog.csdn.net/ningjinghai11/article/details/80677620

- Xilinx-7Series-FPGA高速收发器使用学习—TX发送端介绍https://blog.csdn.net/ladywn/article/details/52985461

- ug476_7Series_Transceivers.