pci device init on hypervisor

1: address translation

#define PCI_CONFIG_ADDR 0xCF8U

#define PCI_CONFIG_DATA 0xCFCU

static uint32_t pci_pio_read_cfg(union pci_bdf bdf, uint32_t offset, uint32_t bytes)

{

uint32_t addr;

uint32_t val;

addr = pio_off_to_address(bdf, offset);

/* Write address to ADDRESS register */

pio_write32(addr, (uint16_t)PCI_CONFIG_ADDR);

/* Read result from DATA register */

switch (bytes) {

case 1U:

val = (uint32_t)pio_read8((uint16_t)PCI_CONFIG_DATA + ((uint16_t)offset & 3U));

break;

case 2U:

val = (uint32_t)pio_read16((uint16_t)PCI_CONFIG_DATA + ((uint16_t)offset & 2U));

break;

default:

val = pio_read32((uint16_t)PCI_CONFIG_DATA);

break;

}

return val;

}

static const struct pci_cfg_ops *acrn_pci_cfg_ops = &pci_pio_cfg_ops;

static const struct pci_cfg_ops pci_pio_cfg_ops = {

.pci_read_cfg = pci_pio_read_cfg,

.pci_write_cfg = pci_pio_write_cfg,

};

uint32_t pci_pdev_read_cfg(union pci_bdf bdf, uint32_t offset, uint32_t bytes)

{

uint32_t val = ~0U;

val = acrn_pci_cfg_ops->pci_read_cfg(bdf, offset, bytes);

return val;

}

#define PCIR_HDRTYPE 0x0EU

hdr_type = (uint8_t)pci_pdev_read_cfg(bdf, PCIR_HDRTYPE, 1U);

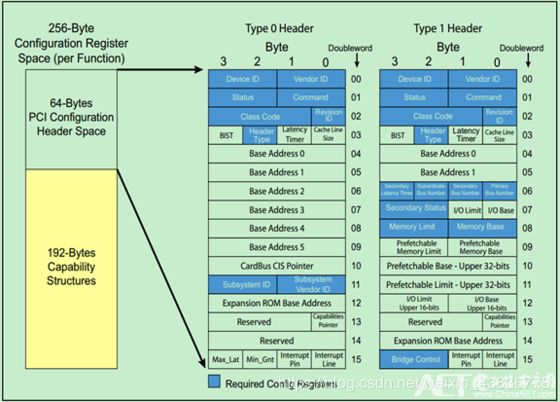

2 pci config space:

由于PCI/PCIe设备分为Bridge和Agent两种,所以配置空间也有两种类型: