揭开次世代处理器革新风暴前奏——Cell处理器

从纸面变成现实——历时五年的研发计划

2000年年中,日本索尼、东芝以及美国IBM开始探讨下一代游戏机处理器的构想,并于秋季达成了共识。次年3月,这三大巨头宣布正式启动位于美国得州奥斯汀的联合开发实验室——STI Design Center(位于IBM奥斯汀实验室ARL的三楼),一个新的Power PC联盟——STI(SONY,Toshiba,IBM)正式诞生。

这个实验室研究的项目进展似乎非常顺利,到了2002年3月份,索尼就首次向外界公布了初步的研究成果——Cell(细胞)的概况,并且很快就在同年的4月份宣布STI将共同开发新的芯片制造技术。

|

从2001年起,超过400位美日工程师参与了Cell的研发

随着Cell项目进展,Cell研发团队也成倍增长,除了STI Design Center外,还启用了IBM远程站点的工程师,包括美国明尼苏达州Rochester、纽约Yorktown Heights、德国Boebingen以及以色列Haifa等地。之所以需要动用如此庞大的研发团队,原因在于Cell的效能目标定得相当高,没有现成的例子可以直接套用,IBM的工程师一再强调Cell是一个从零开始的计划。

AIM阵营理念的失落与STI阵营的宏伟目标

和十多年前的AIM(Apple、IBM、Motorola)阵营不同的是,当初的AIM是旨在合三家之力,利用RISC(精简指令集计算机)概念设计的PowerPC处理器能够击败CISC(复杂指令集计算机)中以x86为代表的Wintel阵营。不过由于微软略带阴谋的惰性、PC市场巨大的惯性以及传说中兼容x86的PowerPC 615遭遇流产,AIM阵营并没能在PC市场对Wintel阵营上形成有效的冲击。时至今日,苹果公司已经卖掉了一部分股票给微软以博取支持,摩托罗拉把芯片部门剥离出来,AIM阵营当初的豪言壮语已经没多少人能记起来了。

AIM阵营虽然没有达到预期中的目标,但是基于PowerPC/Power指令集的产品并没有像Alpha等同期的RISC处理器那样消亡掉,而是继续在扮演着重要的角色,是唯一依然在桌面电脑上不断更新换代保持着较强活力的RISC处理器,并成为Cell的重要构成元素之一。

STI阵营在2002年3月份的Cell主题演讲中,明确表示Cell是为索尼下一代游戏机(Playstation3)而提出的网络化计算概念,以大规模的片内MP(多处理)和高带宽连接架构等技术,把处理器的性能提升到空前的水平,配合开放式的软件环境,实现新的霸业。和AIM阵营相比,STI现在的目标更广阔,包括了游戏机、多媒体工作站以及网格计算,不再仅仅局限在某个领域。

第一代的Cell在运算能力领先英特尔为代表的x86体系三到五年时间,和当初PowePC/Alpha推出不久后就被Intel/AMD引入RISC内核反击相比,现在的Cell显然有更充足的时间来完成全盘的部署。Cell广阔的应用领域,正是Wintel阵营组合裂痕扩大的所在,微软的操作系统垄断优势在这里没有什么影响力,而PowerPC/Power处理器累计10年来的应用软件和开源软件却已经比较丰富。

索尼联合IBM与东芝的目的——各取所需

在Cell之前,任天堂已经采用了源自PowerPC的Gekko处理器作为GameCube的CPU,GameCube虽然并没有取得销量上的胜利,但是在市场上基本上还是能够达到和XBOX平分秋色的水平,保存了参与下一轮搏杀实力,作为一个几乎被边缘化的游戏机厂商来说,已经算是不错的结果了。这除了GameCube性能平衡的设计外,IBM提供的技术支持为开发人员提供了轻松的编程环境也是功不可没的。相比之下,索尼的Playstation2的编程便利性就一直受到开发人员的抱怨,STI阵营的组成,对于提高Playstation 3的开发效率无疑是有莫大的裨益,特别是IBM提供的SDK(软件开发包)。

| IBM的Power架构其实包括三大系列:Power系列、PowerPC系列以及Star系列,三个系列的大部分指令是兼容的,其中的PowerPC是AIM阵营共同开发的,完全开放,其他厂商可以。Star系列已经停掉,由Power4取代。 在Playstation 3之前的Playstation1/2采用的都是MIPS指令集处理器(分别是LSI和Toshiba+LSI)提供的。 1988年,索尼开始了Playstation 1的前身——Super Disc的研发,当任天堂在1993年决定取消合作计划后,曾经为任天堂SNES设计了音频芯片的久夛良木健设计了基于MIPS R3000A的处理器(处理器内核授权来自SGI),作为索尼第一部游戏机Playstation的CPU。 在1993年的时候,AIM阵营刚刚成立,不过当时的Power指令集架构是完全封闭不对外开放的,而AIM的PowerPC 601还完全是一个新生儿。此外,索尼一直都抱有核心部件必须完全掌握在自己手里的企业理念,所以索尼选择早已开放并且直到1998年大部分时间依然是全球销量最大的RISC体系——MIPS指令集更加切合实际情况。 当索尼开发Playstation 2的时候,Playstaion 2被设计为Playstation1的升级版,Emotion Engine采用了MIPS指令集处理器内核。 然而,接下来的问题让索尼头痛不已。PS2采用的Emotion Engine采用了一个全新的体系架构,引入的两个VU(向量单元)在当时缺乏高级工具,影响了性能上的发挥。 |

IBM除了能提供强大的软件支持和PowerPC/Power架构外,手中的SOI、铜互连等技术也是Cell计划达成的重要因素,而且IBM和英特尔之间有特殊而微妙的关系,把IBM拉过来,可以增添对付XBOX(Wintel阵营的产物)的实力(有趣的是,微软后来也选择了IBM的PowerPC架构,为XBOX 2的PowerPC开发Windows系统)。

不过索尼并没有把制造工艺的赌注都扔到IBM一个篮子里,全球第二大半导体厂商——东芝成为Cell的另一个关键同盟。东芝在PS2时代就参与了芯片制造,索尼看中的是东芝的eDRAM和XDR制造技术,PS3如果想获得对PS2的兼容,就需要Toshiba的加盟。而东芝则对Cell的嵌入式版本应用于HDTV以及获取IBM和索尼在半导体技术和资金的支持有非常浓厚的兴趣。

Cell的整体架构实际上有些类似于Playstation2中的Emotion Engine扩大版,因此整体架构的设想应该是由索尼提出,IBM出钱又出力,显然是被Cell潜在的强大运算能力和广泛的应用深深吸引。在设计Cell的时候,IBM就着眼于密码学、Vertex Shader、物理仿真、傅理叶变换、矩阵数学以及其他科学计算领域等各种工作,因此,在Cell出样后不久,IBM就用64枚Cell搭建出16TFlops的工作站。

|

三颗图钉代表的就是STI吗?

挑战——处理器性能提升的三大壁垒

在过去的数十年,处理器体系架构设计师在衡量体系执行性能的时候,主要着眼的无非是两个度量标准:每周期的执行性能(例如IPC——指令/周期)和设计时钟频率(例如用4路扇出或者说fanout-4的非门电路的延迟时间来计算出周期时间)。设计师综合预计采用的工艺水平所能提供的能力(例如各FO4非门电路延迟能达到多少皮秒)和目标平台的限制(例如电源供应、发热条件、参考时钟的孔径晃动等)情况,确定处理器最终的运行频率。

|

不过随着制造工艺日益精密,漏电问题日益显著,每次制造工艺换代平均提升的晶体管数量比上一代高一倍,每平方毫米的用电(功率密度)也显著提升了,但是性能提升却只有40%左右。体系架构师、微体系架构师和逻辑电路工程师都已经意识到,光是考虑频率和IPC并不足够,必须把功率问题也考虑在内,即所谓的功耗壁垒(Power Wall)。

另一个对性能构成较大影响的瓶颈在内存子系统的延迟上,即所谓的内存壁垒(Memory Wall)。STI的工程师认为,现在的处理器访问系统内存的延迟达到了数千个CPU周期,对于片内多内核的系统来说,内存的等待时间问题尤其明显,即使带宽提升了,但是延迟时间削弱了所增带宽提供的性能提升。为了缓解内存与CPU之间延迟造成的性能影响,工程师们采用了各种复杂、昂贵的cache技术,这些cache技术融入了先进的硬件控制电路,对于出色的程序员和编译器来说,虽然很想对cache进行控制,却不得不受制于些cache硬件控制电路。

再来看看频率方面遇到的问题,即所谓的频率壁垒(Frequency Wall)。流水线工位越多的处理器可以跑更高的频率,但是现在的处理器为了提升IPC,大都采用了超标量或者说多发射(multi-issue)执行,由此引入的乱序执行所需要的分支预测并非100%都能推测成功。

流水线工位越多,分支预测失败造成的性能损失就越大。所以虽然靠增加流水线工位把频率提升了,但是因此获得的性能提升正逐渐削弱,如果用性能/耗电指标来衡量的话,这个提升甚至可能是负增长。这倒也不是说增加流水线工位是绝对行不通的办法,研究结果表明,如果能把分支预测的动作减少和增加寄存器的话,增加流水线工位带来的频率提升还是有较大正面意义的。

STI的工程师是如何应对这三大壁垒,最终设计出让世人惊讶的Cell呢?下面就让我们层层展开,揭开Cell的神秘面纱吧。

Cell的处理器微体系

|

Cell在2002年3月份的一次公开演讲中首次曝光,尔后出现了数篇基于这次演讲和2001年索尼申请的专利资料综合起来撰写的推测文章,不过专利和真正的产品还是存在不少距离的,直到当STI在ISSCC 2005上公布4篇Cell的技术文档(同期还有一份RAMBUS的Redwood Rambus ASIC Cell文档)后,Cell的轮廓才终于清晰起来。

|

ISSCC 2005上由STI共同发表的四篇Cell文档。

90纳米Cell的硬件规格和体系架构

按照2002年索尼的Cell专题演讲,提到了Cell会采用100纳米工艺。当2004年第一代的Cell正式投产的时候,采用了更精密的90纳米工艺。不过第一代的Cell在运算能力上还是和最初宣讲的时候有不少差别,例如内部环路连接带宽等,下面让我们来看看基于90纳米生产的Cell的硬件规格和基本架构:

|

量产版[DD2]的 90nm Cell 管芯图[250M晶体管/235mm^2]

量产(DD2)版250百万晶体管;原型[DD1]版234百万晶体管

90纳米制造工艺,钯/SOI半导体,8层铜内连以及1层局部内连

Cell原型(DD1,ISSCC 2005上展示的)管芯面积为221平方毫米,正式的量产版[DD2]为235平方毫米

用散热片把芯片内部温度控制在85摄氏度时,1.1伏特电压能运行于4.06GHz

把散热片温度控制在12摄氏度时,1.1伏特电压能运行于4.32GHz,此时芯片内部温度为41摄氏度

90nm Cell功能模块图1个双线程的64位Power架构处理器内核——PPE(Power Processor Element)

8个SPE(Synergistic Processor Elements),支持单精度和双精度运算

双通道XDR内存控制器,支持256MB XDR内存

把上述单元连接在一起的EIB(Elements Interface Bus)

和外部单元连接的FlexIO总线

基本上,Cell包含了三个主要的单元,这三个单元由两条RAMSBUS公司授权的总线界面支撑。这三个主单元是:一个作为主处理器的Power Processor Element(Power处理器元件,简称PPE)、8个单指令多数据流(SIMD)向量处理器——SPEs以及一个高度可编程的DMA控制器。由于拥有1 Power内核+8 SIMD,所以你也可以把Cell看作是一个MIMD(多指令多数据流)处理器。虽然在以往已经有内建SIMD和向量处理器的例子,但是并不十分成功,不过IBM相信对于多媒体和图形处理偏重的任务来说,这样的体系依然是最佳的搭配,能够把耗电和芯片面积降低到最小。

|

Playstation 2的Emotion Engine架构图

运作模式类似(FPU+CPU Core+VPU0)+(VPU1+GS)

Cell的架构在一定程度上和Emotion Engine非常相似,例如CPU内核是2-issues的超标量执行;Emotion Engine集成了两个向量处理器(VPU0和VPU1,Cell有8个更强大的VPU——SPE),VPU0协助CPU跑物理,VPU1负责跑几何;内部都有一条相对高速的总线;都采用RAMBUS的内存技术;Emotion Engine的VPU1、VPU0都有自己的本地内存等。

当然,Cell和Emotion Engine也是存在不少差别的,例如两者的指令集架构完全不同;EE的CPU内核是索尼自己修改过的MIPS-III指令集,不具备多线程技术,流水线工位要比PPE少很多级;Cell的频率是EE的10倍以上,Cell内部的Cache/内存是EE的30倍以上;Cell的内部总线(EIB)带宽接近EE的30倍以上等等。总之,Cell和EE是完全不同的产品。

控制中枢Power Processor Element

Cell的大脑是Power架构内核。如果我们把Cell看作是一枚网络处理器,那么Power内核就是一个控制平面处理器。这是一个重新设计的64位in-order、2-issue超标量Power内核,专门针对Cell设计,并非其他Power架构处理器的“老翻”。

由这个Power内核(即PXU,Power eXecution Unit)和512KB L2 cache组成的单元被称作PPE(Power Processor Element),在最初的Cell专利文档中,PPE被称作PU(processor unit)。PPE支持Power指令集和AltiVec扩展指令集,具备多线程,可同时对两个线程进行调度执行。

虽然STI曾经探讨过其他处理器内核,不过毫无疑问,由于IBM已经在Power上倾注10年的心血,拥有丰富的经验,因此Power指令集的采用几乎是不二的选择,但是STI并没有选择仅仅弄一个PowerPC 970FX(Apple机上的PowerPC G5)的SoC版了事。

Cell的Power内核是在“频率指标已死”的论调蔓延之前的年代就开始设计的,设计伊始的时候,STI就把Cell的时钟频率目标定在了4GHz以上。STI设计团队为此做了一个简化了的Power内核(例如in-order、2-issue超标量),并且在一些关键的计时部件上采用动态逻辑电路。

|

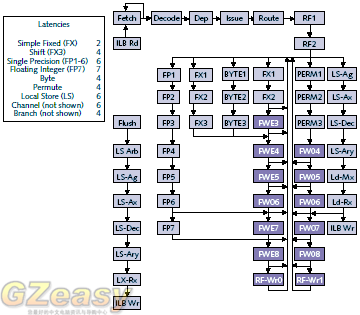

PPE的整数流水线深度为21级,时钟周期间隔为11个FO4延迟

而PowerPC 970流水线深度为16级,时钟周期间隔为13个FO4延迟

PPE遵循PowerPC指令集架构2.02版(以及2.01的公开发布版),设计上采取了与PowerPC 970不同的、独特的管芯面积、时钟频率和体系架构效率平衡点。这个Power内核拥有相对较长的流水线(21级流水线深度,时钟周期间隔为11个FO4),就好像Power4和PowerPC 970的差别,但是PPE并不具备很宽的流水线,同时也没有很多的功能单元。

PPE具备硬件细密化(fine-grained)多线程(FGMT),支持以“轮讯”方式进行线程调度实现“细密化”多线程处理。当两个线程都是活跃的时候,那么处理器就会依次在各线程中拾取指令。当出现一个线程不活跃或者发射(issue)不出指令的时候,另一个活跃的线程就会被允许每个周期都发射出一条指令。多线程执行增加了大约7%的管芯面积,因为这需要增加寄存器文件、程序计数器以及指令解码工位之前的并行指令缓存。IBM的Power5具备吞吐效率更高的Simultaneous Multithreading(SMT),但是增加的芯片面积为24%(和Pentium4的Hyper-Threading不同,Power5的SMT具备动态SMT),而且Power5的超标量能力是4-issue per core,采用SMT的性能回报较高(+40%),把SMT用在只有2-issue的PPE上似乎不太合算。

多线程执行的好处是众所周知的,对于高带宽和游戏内容来说,我们应该可以比较容易地从软件中“提取”出多条并发的线程。在出现分支预测失败的时候,PPE会出现8个周期的流水线性能损失以及4个周期的数据cache装载存取时间损失。如果有一个线程出现分支预测失败的话,第一个线程通常可以马上执行,把流水线停滞的性能损失填补回来,从而实现更高的体系架构效率和更高的处理器资源利用率。

PPE拥有32 KB 2-way关联的L1 指令cache和32KB 4-way关联的L1 数据cache,cache存取延迟为一个周期。

值得注意的是,Cell的内存数据排列是big-endian(一个word的高位byte放在该word在内存区段中的最低地址处,word即字,是指处理器一次处理的指令长度,Cell的字长是64位)方式。虽然Power指令架构可以支持big-endian和little-endian(一个word的低位byte放在该word在内存区段中的最低地址处),但是Cell只支持big-endian。我们PC的软件一直以来都是little-endian,不过当年闹“RISC革命”后,所有的RISC处理器都采用了big-endian,像Apple机的软件就是big-endian的。所以,如果把Cell的软件或者Cell本身是弄到Apple上,内存数据的存放地址顺序并不是什么大的软件障碍。big-endian和little-endian本质上并没有什么相对的优势,不过little-endian比较方便人们的代码阅读。

PPE的中断机制有些类似于PowerPC,当SPE和MFC(内存流控制器,SPE的DMA单元,不是微软炸鸡...)发出中断事件的时候,Cell会把这些中断以外部中断的形式传递给PPE。PPE还可以透过一个支持虚拟处理、比操作系统低阶的管理程序运行多个操作系统。

爆裂筋肉Synergistic Processor Elements

|

Cell有8个SPE,SPE由SXU(Synergistic eXecution Unit,也被称作SPU即Synergistic Processor Unit)、256KB LS(Local Store,本地储存)SRAM以及MFC(实际上是DMA控制器,有些时候又被称作SMF)组成。每个SPE都有自己的local store,local store实际上是SPE的主内存,没有cache的一致性协议,LS的数据和指令的“出”、“入”都必须用软件来管理并且受MFC控制。

LS可以实现数据同步,但是不会由硬件cache一致性实现(因为LS没有这样的硬件一致性部件),那么SPE是如何实现数据同步的呢?8个LS在处理器的内存映射空间中都有自己的别名(alias),PPE可以从LS映射的内存空间读取或者保存数据,只是这样的操作速度比较慢。同样,一个SPE可以使用MFC把数据迁移到自己或者另一个SPE的LS映射的主内存地址里。当某个SPE对所属LS的某个地方作更改的时候,并不会反映到系统主内存中,其他SPE和PPE是不知道的该SPE的LS作了更改,即所谓的一致性,因此该SPE必须把LS更改的部分透过MFC以DMA的方式传到主内存里,这样才能被其他SPE和PPE看到。

Cell中的8个SIMD单元——SPE都是完全一样的,可以处理8位、16位、32位整数和32位(单精度)、64位(双精度)浮点数,由于具备这样的数据处理能力,SPE比传统的协处理器更强大、自由。实际上,SPE并不直接与PPE打交道,命令流的获取是由分配的内存中获取的,而命令和数据的移动是由MFC控制的。

|

每个SPU都是一个针对32位单精度优化的4路SIMD单元,虽然它支持双精度浮点计算,但是性能会大打折扣(大约是单精度的1/10左右)。每个SPU有128个低延迟的128位寄存器,集成庞大的寄存器主要是为了能存放更多的数据值,降低访问LS的次数。SPU的指令集源自PowerPC的向量扩展VMX/AltiVec和PS2 Emotion Engine的向量单元指令集,支持能够对3个源地址和一个目的地址进行操作的(F)MAC或者说(F)MADD指令。在4GHz下,8个SPE能提供256G(Fl)ops的峰值性能,对一枚芯片来说,这是一个给人印象深刻的数字。在索尼当初发表的专利中,还提到了把4枚Cell组合成一枚BE(Broadband Element,宽带元素),实现单芯片1 Tera Flops的运算能力,不过以目前Cell的芯片尺寸看,这个BE似乎不太可能在90nm时代实现,起码要到65nm甚至45nm才有机会看到。

IBM的工程师表示他们曾经考虑过类似TriMedia TM32的VLIW(甚长指令集,VLIW的1条指令可以长达1024bit,并且每条指令包含多个独立并行的操作数,属于体系架构层面的技术)版SPE,但是IBM的工程师意识到VLIW指令的“扩展”是一个棘手的问题,以他们在VMX扩展指令集上的丰富经验,弄一个强大的SIMD单元显然更驾轻就熟。

多媒体数据一旦进入LS,SIMD单元就能够高效地在同一时间对多媒体数据进行处理。和传统的处理器相比,SIMD增加了需要把多个操作数并拢到寄存器的动作。在SPE中的MFC能够把数据并拢到LS中。

SPE没有引入多线程技术,一方面是因为IBM给SPU配置了大量寄存器和足够的LS,在进行数据处理的时候,不会有由于快取命中失败造成的性能损失。另一方面,如果给SPU增加多线程技术的话,可能会出现相当复杂的调度问题和并且造成操作数的隔绝和导致管芯面积显著增大(...8倍基数!)。在对SPE的操作进行编程的时候,程序员能够确保所有的资源都用于进行的任务上而不会被其他线程共享。在共享某个SPE的资源时,如果遇到某些关键进程(例如加密和解密),那么这个SPE就会把这个进程和共享同一LS的其他进程任务隔离。不过与此同时,SPE能够对这些任务进行双缓存。在当前的任务正在运行的时候,MFC就开始传递下一个任务的数据集。

目前的浮点操作扩展指令大都被设计成提高多媒体和3D操作的吞吐能力,像AMD的3D Now!SIMD扩展指令集就牺牲了IEEE754的精度来获取速度和芯片设计的简化,对这类运算来说,精确的舍入模式(rounding mode,例如四舍五入)和异常(exceptions,例如除零、上溢、下溢等)很大程度上并不十分重要。运算结果是否会出现上溢(overflow)、下溢(underflow)和饱和(saturation)等情况,要比是否出现异常(exception)和未知数(undetermined)来的重要。对绝大多数人来说,一格画面中出现一点小的瑕疵是可以忍受的;而由于长时间的错误操作引起的渲染对象丢失、视频断裂或者渲染结果不完整无疑更令人讨厌的。

此外,SPE还支持双精度浮点操作,提供更完整的IEEE754舍入模式(rounding mode)和exception支持,但是性能会急剧下降。但是另一方面,SPE并不支持PowerPC的Precise mode(精确exception模式,出于速度的考量,PowerPC采用非精确exception模式时,对于发生trap的指令“附近的”指令都不会去跑;但是设定为精确exception模式的时候,就会继续跑发生trap的指令后面排列的指令)。第一代Cell的SPE是专门为单精度优化的,如果需要用在科学计算为主的领域(例如超级电脑),SPE还需要作进一步的开发,特别是精度方面。Cell的PPE支持VMX SIMD扩展指令,因此除了SPE外,Cell应该还提供更多的SIMD运算性能。

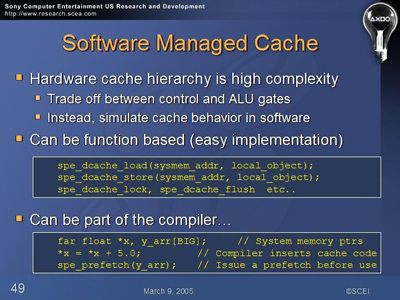

SPE内的256KB Local Store内存

Local Store拥有不错的256KB容量,但是为了达成这个容量,LS也作出了一定的妥协。出于节省芯片空间和耗电的考量,LS是单端口的,传输的数据必须排列成4个字长(quadword,128-bit)。在使用quadword排列的时候,DMA传输一次可以传输1024位数据,任何排列少于quadword的DMA传输都需要经过读取-修改-写入的转换。

|

SPE的Local Store采用eSRAM

但是没有复杂的cache控制电路

控制任务交给程序员和编译器来完成

|

从LS中取指的长度也是128个字节(由32个4字节组组成),不过为了提高取指带宽的效率,这些指令会以64个字节为排列边界存放在latch中,latch的两端就能同时写入、读取指令了。正是因为这样的设计,local store的load和store动作之间的延迟时间被最小化。IBM认为,只要采用优化的代码,local store的利用率可以达到80~90%的水平。

如果要对Local store进行存取,是要按照轻重次序排队的,PPE发出的load-store DMA传输被定义为最高的优先次序,其次是SPE的load-store,SPE的指令拾取次序则会被安排到最后。SPE在遇到一个分支预测失败的时候,会造成相对较长的性能损失(18个周期),不过SPE有大容量的local store,因此IBM鼓励编程人员把循环(loop)代码展开(unrolling),减少因为分支预测失败造成的性能损失。SPE里有一些对分支有帮助的措施,例如branch hint(分支提示)指令,一个三源按位选择。如果分支被正确选取和提示(hint),那么SPE可以看作是能够做到性能无损的分支预测。

| Cell的设计师力求简化以达到较佳的性能/晶体管比例,因此尽管IBM坚持SPE能够做CPU能做的任何事情,但是本质上还是更加类似DSP。SPE采用了in-oreder的流水线,去掉了动态分支预测,但是和大多数的流水线式CPU(例如PowerPC 603)一样,还是能够做静态分支预测的。 |

Cell的架构可以把LS映射到系统主内存中的实地址空间,由拥有“特权”的程序对内存的映射作控制。在Cell中,内存映射是一个2-stage(二阶段)的过程:先使用SLB(区段监视缓存,segment lookaside buffer)把有效地址(effective address)转换成虚拟地址(virtual address);然后使用TLB(translation lookaside buffer)把虚拟地址转换成实地址。在PowerPC架构里,是由“特权”软件程序管理SLB,硬件管理TLB。SPE的内存管理是PowerPC的超集,TLB除了能够由硬件来管理外,也可以让“特权”软件来管理。软件管理能够提供更大的内存页面表灵活度,但是需要更多的性能开销。顺便一提的是,PPE的MMU执行方式PowerPC架构保持一致。

在SPE中,如果出现一个定点操作或者一个浮点操作是按照偶数字长(even-word)来排列,并且load指令是奇数字长(odd-word)排列的时候,那么此时的SPE就具备了一定限度的双指令发射(dual instruction-issue)能力,这样的架构安排有些类似老Pentium,并且隐约间透露出一点(V)LIW的痕迹。

SPU单元从一开始就被设计成可以塞到一个包含进很多执行单元的矩阵中,其编程模型并没有被预先定死,对流水线(pipeline,或者说streaming,流式)和并行(parallel)式处理模式都提供了支持。

在流水线处理执行模式下,数据会轮流在各SPU上跑不同的操作,跑出来的中间结果会传给下一个编号(SPU的编号有0~7)的SPU跑。SPU采用流水线执行模式的好处是可以让各SPU执行的代码相当“细小”,整个运作比较好管理,更居预见性。可预见性是设计Cell处理器时的重要目标,也是SPU为何有内存(虽然是SRAM)而没有cache的原因之一。不过流水线方式缺点是难以做到每个阶段上SPU分配到的任务所需要的时间和复杂度都是等同的,如果其中某个SPU分配到的任务非常复杂,那么整个“流水线”的效率就会受到这个SPU影响(其他阶段的SPU会停下来等待)。

并行模式的灵活性要更高,但是任务的完成时间更加难以确定。每个程序通常都由一枚指定的SPU来全部完成,这样提高数据存放的本地化程度减少数据的复制次数,整体的吞吐量也比较高。缺点是需要更多的线程管理和数据一致性管理开销。不过一颗90nm的Cell有多达8枚SPU,我们可以把上述的两种执行方式混合起来运用,例如多媒体的处理和通用计算是存在差别的,其数据形态更具并行性。

不管是流水线模式还是并行模式,Cell的内存模型都支持对内存位置的共享,某个SPE中local store的有效地址可以被Cell中的其他处理单元另命别名(alias)。由于有大量的128位寄存器和内存转址缓存,前后关系交换(context switch)的时间成本和存储空间成本会非常“昂贵”,因此IBM的工程师高度建议给每个SPU分配的是一个能单独完成的任务,程序编写的时候要做到每个SPU都能够获得要完成任务所需的全部指令和数据。

SPU和MFC之间的通信是透过一条SPE Channel(SPE通道)实现的,每条SPE Channle都是一条具备多种查询深度的单向通道,可以配置成块方式(blocking)或者非块方式(non-blocking)。SPU命令必须按照SPU的接受顺序来执行。SPU透过这条通道和一个外部事件控制器,SPU可以设置为执行或者等待状态。SPU和PPE之间的通信可以透过MFC提供的两个mailbox(邮箱)队列来实现,这些32位的mailbox信息是由用户定义的,在PPE中,这些mailbox在内存中被映射到I/O空间地址。

虽然SPE在各类数据的处理、load和store的控制以及分支处理等方面都相当了得,但是SPE并不是设计成跑操作系统的,和Cavium Networks公司的16个MIPS-64bit内核处理器Octeon相比,这的确简化了SPE的设计。为了达成运行高时频的目标,SPU在某方面的设计也有些类似于PPE,例如用in-order的执行机制简化电路和减少数据相依性的检查,但是分支预测失误造成的损失要比PPE高的多。IBM还在SPE中应用了动态逻辑电路来实现低耗能高频运行。

Cell没有引入专门用于安全事务处理的单元,而是交给了SPU来完成这个任务,不过对于SPE是如何达成这个任务,STI目前还没有透露。我们前面提到,Cell有一个别具特色的设计,可以利用硬件保护功能把各个SPE隔离开来,在这样的模式下,SPU(s)被专门用于安全运算,不受系统其他单元的侵扰,拥有受专门保护不会被其他进程访问的内存。该特性将成为未来数码版权管理(DRM)的执行方式,SPU的“信任计算”所在。

内存流控制器(Memory Flow Controller)

让我们继续从生物学的观点来看看Cell的其他部件:Cell的心脏——MFC(内存流控制器)以及Cell的血管系统——EIB(执行单元内连总线,Element Interconnect Bus)。为了维持Cell处理器的运行,MFC可以支持超过128个未决内存请求,而要让SPE保持较高的利用率同样需要MFC提供对大量事务流的同步。

MFC有自己的内存管理单元(MMU),属于PXU MMU的子集,具备64位虚拟内存寻址能力,新引入了16KB和64MB的页面大小,传输包的数据大小可以从1个字节到16KB,不过IBM的工程师表示尽量不要采用小于一条cache-line(128个字节)的传输包。MFC支持分散/收集(scatter/gather)以及交错式(interleaved)操作。

根据IBM在Cell的DMA命令Lis机制(用来确定DMA命令列表存放在local store中什么地方并递交给DMA单元异步执行)的经验来看,对于那些在达至SPE运算极限能力之前就先受至于内存带宽的SPE程序,是可以从大跨度内存空间定址和预拾取(Prefetch)上获益良多。MFC采用的DMA-list机制有些类似于显示卡上采用的dislplay-list。

MFC在SPE和内存之间的数据传输使用的是get和put命令,每条命令都能有一个指令修改符(instruction modifier,有一个"s"前缀),用来指示SPE在这次传输完成后的程序计数器寄存器开始处理指令。MFC可以直接从SPE获取数据并装填到PPE的L2 cache中,让PPE更快的获得关键数据。