BIOS之内存控制器设置以及内存电路接口分析

作者:wogoyixikexie@gliet

现在来看2440内存控制器初始化代码

;Set memory control registers

ldr r0,=SMRDATA ;be careful!, hzh

ldr r1,=BWSCON ;BWSCON Address

add r2, r0, #52 ;End address of SMRDATA

0

ldr r3, [r0], #4

str r3, [r1], #4

cmp r2, r0

bne %B0

;=========================================

SMRDATA DATA

; Memory configuration should be optimized for best performance

; The following parameter is not optimized.

; Memory access cycle parameter strategy

; 1) The memory settings is safe parameters even at HCLK=75Mhz.

; 2) SDRAM refresh period is for HCLK<=75Mhz.

DCD (0+(B1_BWSCON<<4)+(B2_BWSCON<<8)+(B3_BWSCON<<12)+(B4_BWSCON<<16)+(B5_BWSCON<<20) + (B6_BWSCON<<24)+(B7_BWSCON<<28))

DCD ((B0_Tacs<<13)+(B0_Tcos<<11)+(B0_Tacc<<8)+(B0_Tcoh<<6)+(B0_Tah<<4)+(B0_Tacp<<2)+(B0_PMC)) ;GCS0

DCD ((B1_Tacs<<13)+(B1_Tcos<<11)+(B1_Tacc<<8)+(B1_Tcoh<<6)+(B1_Tah<<4)+(B1_Tacp<<2)+(B1_PMC)) ;GCS1

DCD ((B2_Tacs<<13)+(B2_Tcos<<11)+(B2_Tacc<<8)+(B2_Tcoh<<6)+(B2_Tah<<4)+(B2_Tacp<<2)+(B2_PMC)) ;GCS2

DCD ((B3_Tacs<<13)+(B3_Tcos<<11)+(B3_Tacc<<8)+(B3_Tcoh<<6)+(B3_Tah<<4)+(B3_Tacp<<2)+(B3_PMC)) ;GCS3

DCD ((B4_Tacs<<13)+(B4_Tcos<<11)+(B4_Tacc<<8)+(B4_Tcoh<<6)+(B4_Tah<<4)+(B4_Tacp<<2)+(B4_PMC)) ;GCS4

DCD ((B5_Tacs<<13)+(B5_Tcos<<11)+(B5_Tacc<<8)+(B5_Tcoh<<6)+(B5_Tah<<4)+(B5_Tacp<<2)+(B5_PMC)) ;GCS5

DCD ((B6_MT<<15)+(B6_Trcd<<2)+(B6_SCAN)) ;GCS6

DCD ((B7_MT<<15)+(B7_Trcd<<2)+(B7_SCAN)) ;GCS7

DCD ((REFEN<<23)+(TREFMD<<22)+(Trp<<20)+(Tsrc<<18)+(Tchr<<16)+REFCNT)

DCD 0x32 ;SCLK power saving mode, BANKSIZE 128M/128M

;DCD 0x02 ;SCLK power saving disable, BANKSIZE 128M/128M

DCD 0x30 ;MRSR6 CL=3clk

DCD 0x30 ;MRSR7 CL=3clk

---------对于上面的东西无非是寄存器的参数设置,很明了。我在这里就不注释了。

下面看我和一个技术网友的谈话

且听风吟 22:50:32

这是2440内存控制器那章节

且听风吟 22:51:19

其实这个nWBE和所有bank公用的的

且听风吟 22:51:30

就接到当才那几个东西

datasheet 22:51:37

不,这个问题的重点是 cpu 的LnWBEn n=(0,1,2,3)

且听风吟 22:51:53

是啊

datasheet 22:52:11

还有sdram 的UDQM, LDQM

且听风吟 22:52:26

现在我想到另外一个问题,四片32M又应该怎么接的呢?

且听风吟 22:52:37

毕竟这些信号只有四个引脚

且听风吟 22:52:58

估计最大2440最大内存只能扩大到256m

datasheet 22:53:27

估计没办法接 4个16位的

datasheet 22:56:09

nWBE[3:0]用于为ROM/SRAM/FLASH存储器组提供写操作信号

且听风吟 22:56:49

刚才我发给你的是UB/LB

datasheet 22:57:58

明白

datasheet 23:03:18

nWE就像通常的单片机(51)里的nWE一样使用

nWBE[3:0]通常在外接SDRAM时使用,如两片32M的SDRAM时,nWBE0,nWBE1分别接低位的LDQM和UDQM;nWBE2,nWBE3分别接高位的LDQM和UDQM

且听风吟 23:03:38

是啊

datasheet 23:03:50

nWBE[3:0]还可以应用在多片8位ROM组成32位ROM的场合

且听风吟 23:04:04

现在我正在找,软件在哪里设置了这个东西

datasheet 23:04:17

软件没有

datasheet 23:04:25

是指令吧?

且听风吟 23:04:35

对

datasheet 23:05:05

因为在 内存配置的时候,我们设成了 32位的

且听风吟 23:05:40

是32位

datasheet 23:05:49

BWSCON

DWx:使用两位来设置存储器的位宽:00-8位,01-16位,10-32位

且听风吟 23:05:58

这个东西不会是自动的把

datasheet 23:06:20

是自动的

且听风吟 23:06:44

天啊

且听风吟 23:06:53

2440太隐蔽了

datasheet 23:06:57

你看看这篇吧

且听风吟 23:07:01

那篇?

datasheet 23:07:01

http://chinadz.net/Article/IC/200608/101.htm

datasheet 23:07:04

是很老的

datasheet 23:07:33

arm 应该很早就有这功能了

且听风吟 23:08:29

只是我太菜了,才会不知道这些,哈哈

且听风吟 23:08:51

我以前只会一点单片机,就直接2440了

datasheet 23:09:06

你已经很难得了

且听风吟 23:09:37

去年这个时候还打算去做销售员呢

datasheet 23:10:21

唉,别说了

datasheet 23:10:30

我现在还没入行呢,

datasheet 23:10:40

只是个门外汉罢了

且听风吟 23:11:20

继续努力

且听风吟 23:12:02

这几天还要搞什么三串口,在标准5.0下,摄像头驱动

datasheet 23:12:49

呵呵,别人都说写wince 的驱动 好过linux下的

datasheet 23:13:13

不过还好,这些都有开源,可以参考

SZwince 23:22:07

还有一个地方 跟这个有关系

且听风吟 23:22:14

?

SZwince 23:23:26

cpu 的地址线 与sdram的 是错开的

SZwince 23:23:48

少了一根线,也就是 他每次只读了 半字

且听风吟 23:24:07

错开了两位

且听风吟 23:24:20

每次都是32位读取的

SZwince 23:24:38

那是宏观上的

且听风吟 23:24:54

你说少了一根是哪里?

SZwince 23:25:15

少了两根

SZwince 23:25:28

a0 a1

且听风吟 23:25:31

两根就是32位的对齐方式

--------------------------------------基本是这样

CSDNgooogleman(402955982) 23:34:20

我有些不敢相信

CSDNgooogleman(402955982) 23:34:59

2440的地址访问居然是高16位和低16位分开读取的

CSDNgooogleman(402955982) 23:35:22

但是这样让我很吃惊

CSDNgooogleman(402955982) 23:35:52

有些问题我现在还没有办法解释,我先做个记号先,明天继续分析

===============================哈哈,再来=====================================

-----------现在我已经锁定问题,但是我还是不确定-----------今天在CSDN发帖个帖子吧。希望有得到帮助

=============================================================================

昨晚,问了一些群里面的人,后来再看看电路图。

发现问题在LDQM,UDQM这两个引脚,接到2440的四个nWBE引脚。内存资料是这么说的:Data Input/Output Mask Controls output buffers in read mode and masks input data in write mode 一些中文文档是这么说的:在读模式下控制输出缓冲;在写模式下屏蔽输入数据。按照这种接法(2片内存都是错位2位)我觉得内存是分开高16位和低16位分别访问的,但是让我纳闷的是2440是怎么控制四个nWBE引脚来完成任务的?并且,我看访问内存的时候都是直接访问32位地址的。真的迷茫了,不知道2440是如何实现的。请高手指点一下。谢谢。

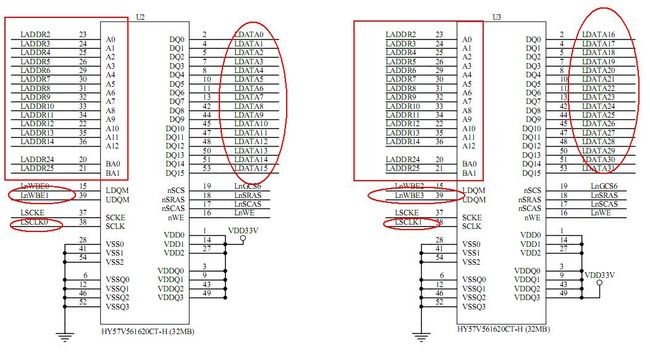

下图是内存连接图,关键部分我都大了红圈。

----------------------------------------------------------------------------------------------

实际上,它把两片 16 位的内存组合成 32 位来用了,这两片内存都接在了控制芯片同一个 BANK 地址上,利用 地址线 数据线 SCLK LDQM UDQM 这 3 个引脚来控制 32 位数据的读写。

-------------------------------------

访问控制信号:为了实现ARM存储器访问指令LDR/STR字节、半字和字访问的三种方式,在S3C2440的存储器组中,除了Bank0以外的所有地址空间都可以通过编程设置为8位、16位或32位对准访问,Bank0可以设置为16位或32位。引脚nWBE[3:0](写字节使能)实现8bit ROM芯片组的三种访问方式,或者SRAM不使用UB/LB(在BWSCON中设置)的情况下,与UB/LB连接。引脚nBE[3:0](在使用SRAM情况下的字节允许信号)在SRAM使用UB/LB(是否使用可在BWSCON中设置)的情况下与UB/LB连接。DQM[3:0](SDRAM数据屏蔽信号)引脚实现对SDRAM的三种访问。还有nWAIT、nXBREQ/nXBACK引脚。

谢谢两位。你们说的在那篇文章我都知道。只是我想了解的更加具体一点——可惜三星已经把所有东西包装得严严实实——很多东西通过硬件实现了。

----------现在我把我的理解发上来。

一、为什么会两片内存都连接相同的地址线?(我一直以为地址线必须是递增的)

答案:因为这是两片独立内存,地址线都是固定的,如果地址递增会造成糟糕的后果(我还真以为是两片内存可以无缝连接呢!大错特错了。)

二、为什么两片内存都要错位两位?

答案:

因为两片内存是独立访问的,并且总线宽度都是32位(高16位数据和低16数据位分开读取。至于错位原因请看ARM字节对齐文章)。

但是难题来了,为什么三星访问内存时候并没有分开呢?LDQM UDQM 这两个引脚起作用了(用来屏蔽高低字节输出,相当于锁存)控制这两个引脚的是三星的nWBE

引脚,三星是怎么控制这些引脚的呢?我也很想知道,在这里我只能说出我的推测:2440/2410有个寄存器设置内存的大小,我想2440/2410就是根据这些信息来控制这些引脚,使最总实现32位一起访问。——所有东西包装得严严实实——很多东西通过硬件实现了。

如果我说的不对,请跟帖,两天后结贴。也让我彻底死心,彻底明白。

转载请标明wogoyixikexie@gliet桂林电子科技大学一系科协,如有错误,希望能够指出。