信号完整性之阻抗匹配与端接方法

1. 前言

随着电子技术的发展,电路的规模越来越大,单个器件集成的功能越来越多,速率越来越高,而器件的尺寸越来越小。由于器件尺寸的减小,器件引脚信号变化沿的速率变得越来越高,导致SI问题越来越突出。

SI (Signal Integrity,信号完整性)与以下几个因素有关:反射、串扰、辐射。

反射是由信号传输路径上的阻抗不连续造成的;

串扰与信号的间距有关;

辐射则与高速器件自身以及PCB设计均有关。

2. 信号的阻抗匹配

信号的阻抗匹配是影响信号完整性最主要的因素。

什么样的信号需要考虑阻抗匹配?

信号的有效频率 F k n e e F_{knee} Fknee取决于信号边沿速率,当信号的有效频率 F k n e e F_{knee} Fknee比较低,使得信号的有效波长 λ k n e e λ_{knee} λknee大于信号走线长度的6倍时,该信号线路可被视为集总式,即,某一特定时刻,信号线路上任一点的电平状态都近似相等,否则,该信号线路应被视为分布式,信号线的走线以传输线来对待。

对于传输线,必须考虑在信号传输路径上阻抗不匹配而带来的反射。

备注:

信号有效频率为 F k n e e F_{knee} Fknee

定义为:

F k n e e F_{knee} Fknee=0.5/Tr(10%~90%)

Tr(10%~90%)为信号的10% ~ 90%上升时间

λ k n e e λ_{knee} λknee=C/ F k n e e F_{knee} Fknee

C=3x10^8m/s

区分传输线与非传输线的步骤如下:

- 获取信号的有效频率 F k n e e F_{knee} Fknee和走线长度L

- 利用 F k n e e F_{knee} Fknee计算出信号的有效波长 λ k n e e λ_{knee} λknee

- 判断L与 λ k n e e λ_{knee} λknee/6之间的关系,若L> λ k n e e λ_{knee} λknee/6,则该走线视为传输线,反之,则为非传输线。

2.1 反射的计算

。信号的反射可利用反射系数 ρ \rho ρ计算:

ρ \rho ρ=(Z2-Z1)/(Z2+Z1)

Z2-----反射点之后的线路阻抗

Z1-----反射点之前的线路阻抗

反射计算案例:

如下图,信号的发送端在A点,接收端在B点,信号线为传输线,A点到B点的走线传输延时为5ns,信号输出电平为3.3V,发送端器件的输出阻抗和传输线阻抗都是50Ω,则在接收端器件的输入阻抗为0Ω和无穷大的两种情况,A点波形分别如何?

在A点,由于发送端器件输出阻抗和传输线阻抗都是50Ω(发送端输出阻抗=发送端源电阻R0+发送端串电阻Rs,等于或接近传输线阻抗),因此在A点存在分压(以A点为反射点,A点之后的线路阻抗Z2为传输线阻抗,A点之前的线路阻抗为发送端输出阻抗;因此信号分压,真正进入传输线上传播的只有源信号电压的一半),信号电平为发送端输出电平的一半,即A点电压为1.65V(3.3V/2)。

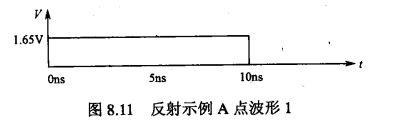

1)当接收端器件的输入阻抗为0Ω时,B点反射系数:

ρ \rho ρ=(Z2-Z1)/(Z2+Z1)==(0-50)/(0+50)=-1

Z2------B点之后接收端输入阻抗

Z1----- B点之前传输线阻抗

ρ \rho ρ=-1,表示在B点,信号将以反向电平而全反射,即反射电平为-1.65V。所以B点电压为1.65-1.65=0V(接收端输入的阻抗为0相当于短路)

反射信号回到A点后,

ρ \rho ρ=(Z2-Z1)/(Z2+Z1)==(50-50)/(50+50)=0

Z2-------A点之后的发送端输出阻抗

Z1-------A点之前的传输线阻抗

ρ \rho ρ=0,表示在A点,信号全部被吸收而不再发生反射。

因此A点波形如下图:

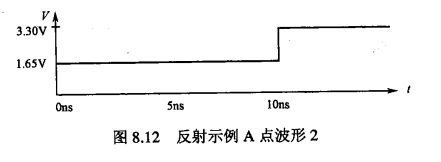

2)当接收端器件的输入阻抗为无穷大时,B点的反射系数:

ρ \rho ρ= ( ∞ - 50)/( ∞ + 50)=1

ρ \rho ρ=1,表示在B点,信号将以正向电平而全反射,即反射电平为1.65V(此时B点电平为1.65+1.65=3.3V;相当于接收端开路情况)。

反射信号回到A点后,同样全部被吸收而不再发生反射。

因此,A点波形如下图:

始端、传输路径、终端阻抗的不匹配,都造成信号的反射。为了减小反射,需尽可能地减小反射系数 ρ \rho ρ,即要求Z2尽可能地等于Z1.

通过在电路上增加元器件以减小 ρ \rho ρ的方法,称为阻抗匹配设计。从理论上讲,如果在传输线的任何一端消除这种阻抗突变,反射也随之消失。阻抗端接就是基于这种策略,通过人为加入电阻来消除或减轻这种阻抗突变。

2.2 阻抗匹配设计

传输线的匹配端接通常采用两种策略:

1)使负载阻抗与传输线阻抗匹配,即并联端接

2)使源端阻抗与传输线阻抗匹配,即串联端接。

在实际应用中,我们要根据具体情况来选择串联匹配还是并联匹配。

一般情况下,很少会让发送端和接收端都保持完全的匹配,因为这种情况下,接收端将无法靠反射来达到足够的电压幅值。

电路设计中常用的端接方式有五种:

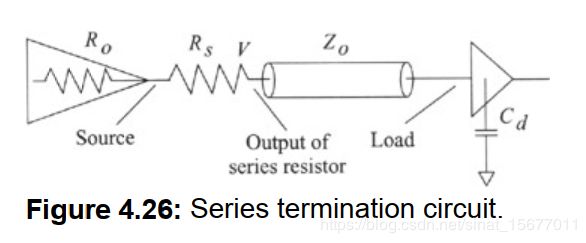

1)发送端串联端接

Ro----发送端(源端)输出阻抗(比如推挽输出MOS管内阻等)

Rs----发送端串联电阻

Z0----传输线特性阻抗

该匹配方式要求发送端器件输出阻抗Ro(比如推挽输出MOS管内阻等)与发送端匹配电阻Rs的和,近似地等于传输线阻抗。串联电阻必须直接位于驱动器的输出,而且在元件和电阻间不能使用过孔,串联电阻计算公式:

Rs=Z0 - Ro

例如,如果R0=22Ω,传输线阻抗Z0=55Ω,则Rs=55-22=33Ω; 实际上计算出的串联阻抗Rs会大于等于源输出阻抗且小于传输线阻抗Z0。典型值在15Ω~75Ω(通常为33Ω)

单点对单点地信号连接,应采用发送端串联匹配。当终端是集总负载或单一元件时,串联匹配是最佳的。

这种匹配方式只是实现了发送端地匹配,由以上案例可知,信号传输路径上地电平约为驱动电平地一半,而接收端器件阻抗较大,反射系数 ρ \rho ρ近似为1,从而造成在接收端的全反射,全反射后接收端电平正好等于发送端的驱动电平。

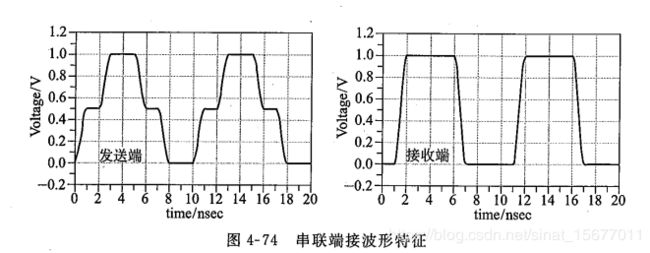

串联端接典型的信号波形特征如下图所示,接收端波形能够达到满摆幅,反射信号返回源端后不再反射。驱动端波形出现典型的台阶形状,台阶的时间宽度为传输线往返时间延迟,台阶的幅值为满摆幅的一半。

实际上驱动器输出阻抗Ro并非恒定值,因此串联端接无法真正和传输线阻抗相匹配,对于反射噪声来说,驱动器的交流输出阻抗Zac有可能远高于传输线特性阻抗(与输出MOS直流工作位置有关,当直流工作点电压较低时,Zac和Zdc差别较小)。端接串联电阻的作用更确切地说是控制加载到传输线上信号地电压幅度,如果加载到传输线上地电压幅度不超过信号幅度地一半,末端反射后就不会出现波形地上冲和下冲。

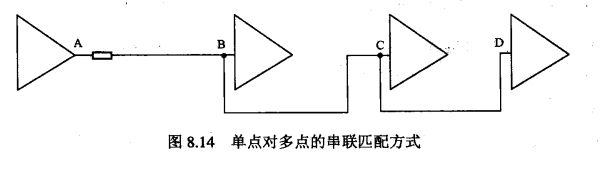

若采用发送端串联匹配实现单点对多点的连接,走线应成菊花链式,如下图:

由于串联匹配需通过反射才能在接收端建立电平,因此上图D点的电平最先建立,而A点最晚,从时序裕量的方面考虑,D点最好,然后依次是C、B。

优点:

发送端匹配不会引起额外的功耗;匹配方式简单,且不会增加线路的stub(分叉)。

缺点:

一般仅适合于点对点的信号;受发送端分压的影响,传输路径上的电平低于驱动电平,在接收端,必须依靠反射才能恢复电平;

另一方面,匹配电阻Rs的存在将使信号的边沿变缓,在时序裕量较小的场合,应权衡选择Rs的阻值。

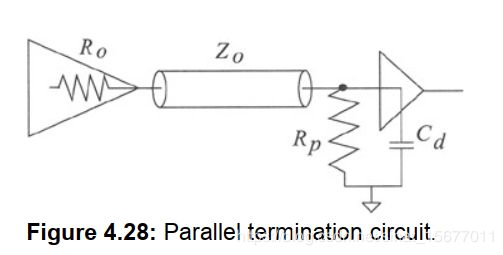

2)接收端并联端接

接收端并联匹配适用于单点对多点的连接,与发送端匹配不同,接收端匹配无需借助反射以建立电平,通过使匹配电阻Rp的阻值等于传输线阻抗,可实现接收端的阻抗匹配。

对于简单的并联匹配是在接收端使用单一的电阻(Rp),这个电阻Rp必须等于传输线的特性阻抗值。

例如,如果传输线的阻抗为55Ω,那么Rp的值也为55Ω。

通常这个电阻的另一端在参考地上(Rp接地或电源取决于逻辑门限要求,对于高频AC信号,地和电源平面都是参考平面)。

由于接收端输入阻抗很高,信号传输到传输线末端感觉到地阻抗接近等于端接电阻地阻值,只要端接电阻和传输线阻抗相匹配,信号不再发送反射。接收端感受到的信号幅度即驱动器加载到传输线上的信号电压幅度。

假设驱动器工作电压为1V,驱动器高电平输出阻抗为20Ω,传输线的阻抗为50Ω,则加载到传输线上的信号幅度为

50/(20+50)x 1V = 0.714V

下图显示了这种情况下发送端和接收端的信号波形,高电平都是0.714V。末端并联端接拉到地会拉低信号的高电平。

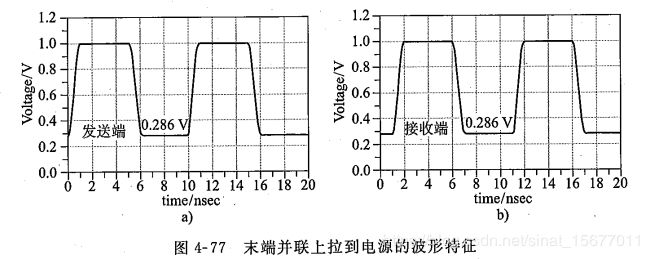

末端并联上拉到电源,同样要求端接电阻等于传输线的特性阻抗。

假设驱动器低电平直流输出阻抗为20Ω,传输线的阻抗为50Ω,驱动器的工作电压为1V,则信号低电平为

20/(20+50) x1V=0.286V

下图显示了低电平的这种变化。所以末端并联到电源会拉高信号的低电平。

综上所述,在末端并联端接方式中,驱动器的直流输出阻抗会影响到信号的稳态电平值。如果直流输出阻抗较高,可能会导致接收端的信号无法满足门限电平的要求。

例如,驱动器低电平直流输出阻抗为20Ω,传输线的特性阻抗为50Ω,驱动器的工作电压为3.3V,末端并联上拉到电源时,信号低电平为0.94V,如果接收端低电平门限为0.8V,则接收端可能永远接收不到0信号。

简单并联匹配很少在TTL或者CMOS电路设计中使用,这是因为这些设计中逻辑高需要很大的驱动电流(比如Rt接地时)。当发送端切换到Vcc 或者逻辑高时,驱动器必须要为终端匹配电阻提供Vcc/R的电流。这会导致过多的能量消耗并引起噪声容限降级,所以当使用并联终端时,必须要考虑接收器可以接受什么程度的降级。

优点:不会影响信号的边沿速率

缺点:需要在电阻Rt上消耗一定的功率(并联电阻常用范围在50~150Ω);在接收端,相对电平判决门限,很容易出现高、低电平不对称的现象。

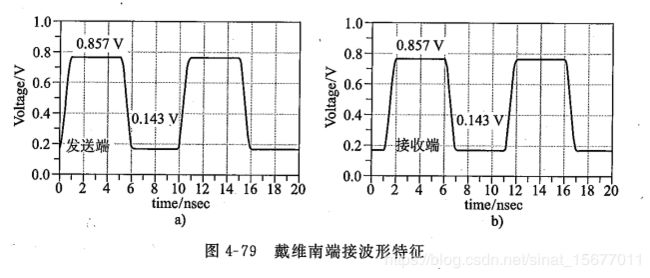

3)戴维南端接

戴维南端接实际上也是末端并联端接的一种形式,包含一个上拉电阻和一个下拉电阻。电阻值满足:R1//R2=Zo。

通常戴维南端接用于驱动器驱动能力不足,而又必须使用末端并联端接的场合。

上拉电阻能够提供一部分驱动电流给负载以帮助驱动器驱动高电平,下拉电阻能够吸收一部分电流以帮助驱动器驱动低电平。

在驱动器输出高电平时,由于有下拉电阻,所以高电平会被拉低。同样当驱动器输出低电平时,由于存在上拉电阻而使信号低电平被抬高。

下图显示了驱动器直流输出阻抗为20Ω,传输线的特性阻抗为50Ω,驱动器的工作电压为1V,上下拉电阻都为100Ω时的信号波形。

上下拉电阻的确定,需要考虑到驱动器高低电平时直流输出阻抗的不对称性。

在选择上下拉电阻的阻值时要适当地调整接收信号地中值电平地位置,尽量使接收器接收高低电平时有近似地噪声容限。

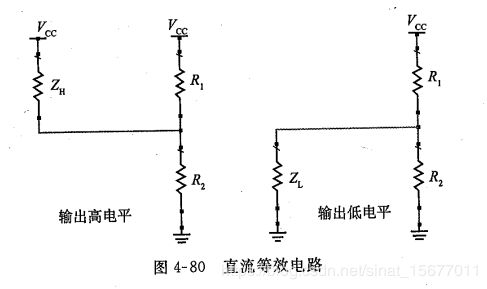

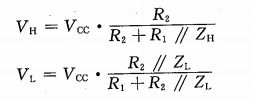

假设高电平输出阻抗为 Z H Z_H ZH,低电平输出阻抗为 Z L Z_L ZL,输出高电平和低电平时直流通路地阻抗连接关系如下图

输出高电平和低电平时稳态电压值分别为

调整R2的值,可以改变低电平电压值。同时,由于必须满足R1//R2=Zo的关系,R2改变的同时,R1也相应变化。因此信号的高低电平都会发生改变。

电阻值可由下式计算:

其中,

V O H V_{OH} VOH、 V O L V_{OL} VOL分别为接收端高电平和低电平的判决门限。

I O H I_{OH} IOH、 I O L I_{OL} IOL分别为高电平和低电平时驱动器的输出电流。

优点:不影响信号的边沿速率;较容易实现接收端高、低电平相对门限电平的对称分布;可满足接收端对共模偏置电平的要求。

缺点:需要在电阻R1和R2上消耗一定的功率,当采用接收端分压匹配方式的信号数目较多时,在功耗评估的过程中,不能忽略匹配电阻上的功耗。

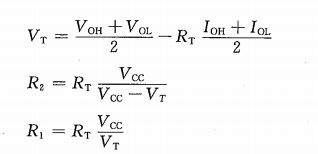

4)接收端AC端接

上述并联匹配、分压匹配方式都存在直流通路,产生了一定的功耗,而在阻容并联匹配中,电容Ct可阻断该通路,有效地减少了功耗,一般Rt的阻值与传输线阻抗近似相等,Ct选取几十至几百皮法的陶瓷电容即可,电容要能承受信号的DC电压。

这样,原驱动器就不需要为终端器件提供电流了,而电容允许RF能量(通常是正弦波而不是信号DC逻辑电平)通过,因此切换状态包含的AC电流(RF能量)会流到地。

AC端接要求链路上传输的是直流平衡信号(比如时钟信号),不适合突发模式的数据传输。

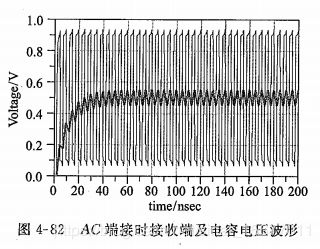

当链路中信号传输进入稳定状态时,电容电压会在某一电平值附件波动。如下图显示了时钟信号进行AC端接时接收端box和电容电压波形(中值电平附件小幅度摆动的波形)

对于时钟信号,电路进入稳定工作状态后,信号输出高电平时电容电压上升量必然等于信号输出低电平的下降量。

否则,电容电压会无限制地增加或降低。

当时钟信号的占空比为50%时,电容电压摆幅的中心为信号的中值电平。

如果占空比高于50%,电容电压摆幅中心大于信号的中值电平。

如果占空比低于50%,电容电压摆幅的中心小于信号的中值电平。

由于AC端接中电容电压一直处于波动状态,电容电压的波动也会影响信号波形。

如果传输的是数据信号,并且数据信号中连0或者连1的比特数过多,电容电压就会大幅度波动,进而影响信号的传输。

综上所述,电容值得选择必须考虑两个方面的因素:

1)传输线的延时

2)信号游程长度对应的时间间隔。

如果传输线的特性阻抗为50Ω,端接阻值为50Ω,则RC时间常数为100*C。

电容值得选择必须使时间常数远大于2倍的传输线延时,即RC>>2Td。

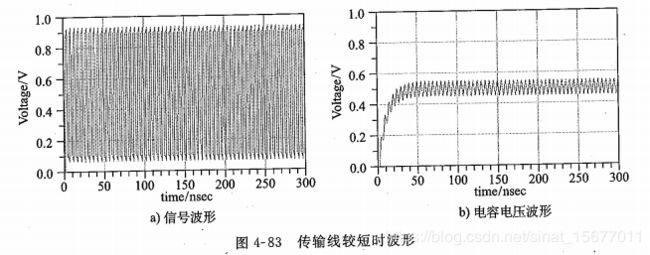

当电容值为200pF时,RC时间常数等于20ns。传输线延时为2ns时,信号波形和电容波形如下所示:

此时时间常数为传输线延时的10倍,很快进入稳定状态,信号波形稳定。电容电压稳定在中值电平附件。

当传输线延时为20ns时,信号波形和电容电压波形如下所示:

接收端信号波形整体上大幅波动,信号长时间不能进入稳定的工作状态,电容电压同样出现大幅波动。

对于数据信号进行AC端接时,要求时间常数远大于信号游程长度对应的时间间隔(码流中最长连0或者连1的时间间隔),即:

RC>>N*Tbit

N表示游程长度,Tbit表示1bit的时间间隔。

工程上使用AC端接最好通过仿真来解决。

优点:相对其他接收方式功耗小,同时也不会产生其他并联端接方式中高电平被拉低或者低电平被抬高的现象。

缺点:同样存在接收端高、低电平不对称的问题;由于Ct的存在,将使信号的边沿变缓。

5)接收端二极管并联匹配

严格来说,二极管并联只能实现对接收端器件的保护,而无法实现阻抗匹配。当在传输线路径上存在阻抗不匹配时,接收端信号可能存在过冲,对器件的使用寿命构成影响。二极管能有效地对过冲电平进行钳位,从而实现了对接收端器件地保护。

一般而言,在许多器件地输入端,片内已内置了类似地并联二极管,在这种情况下,设计时不再需要外加二极管。

优点:保护接收端器件地输入端口

缺点:无法消除反射;且在功能上,受限于二极管地开关速度。

参考文献:

《高速电路设计实践》

《信号完整性揭秘:于博士SI设计手记》

《Printed Circuit Board Design Techniques for EMC Compliance》