什么是“门级网表”(Gate-level netlist)文件?

首先,RTL是寄存器传输层的缩写,RTL既是一个抽象层级概念,又是一种HDL代码编写风格[1]。

RTL是一个抽象层级概念

认识和理解IC集成电路可以从多种不同的角度,其中最好最普遍的一种是:抽象层级,即,将IC做不同程度的抽象,按照抽象程度从高到底,分别为[2]:

- 系统层

- 算法层

- 寄存器传输层

- 逻辑层

- 电路层

而上述的每一抽象层级,均可以用三种不同的方式去描述,分别为[2]:

- 行为描述

- 物理描述

- 结构描述

我们常说的综合其实就是指从高抽象层级转换到低抽象层级的过程,各层级间综合过程如下[3]:

- 算法层--(高层次综合 HLS)-->寄存器传输层

- 寄存器传输层--(逻辑综合 LS)-->逻辑层

- 逻辑层--(版图综合即布局布线Place & Route)-->电路层

2. RTL是一种HDL代码编写风格

HDL描述电路,有三种方式:

- 数据流

- 行为结构

- 门级连接

RTL作为一种HDL代码编写风格是指代码主要采用数据流和行为结构相结合的方式编写[1]。

你所说的RTL文件指的就是用这种风格编写的Verilog或VHDL代码文件。

从图1中可以看出,RTL代码实际对应的结构描述是众多算术运算单元(ALU)、多路选择器(MUX)、寄存器等等,而这些模块实际上都是由各种逻辑门(与非门,或非门等等)和基本触发器(D触发器、JK触发器等等)搭成的,逻辑综合的过程,就是要把RTL文件描述的电路进一步展开,转换成用逻辑门和触发器搭成的电路,而用来描述这些逻辑门和触发器的连接关系的文件就是门级网表文件。

因此,逻辑综合包含两个主要步骤[1]:

- 选择工艺库(标准单元库)

- 设计约束(时序约束、面积约束和功耗约束)

选择的工艺库中就包含了基本的逻辑门和触发器。

不同的综合工具生成的网表文件的文件格式也不太一样,如*.v(Design Compiler, Synopsys)、*.vh(PKS, Cadence)和*.edf(Synplify, Synplicity)。

对于*.v格式的门级网表文件,可以看成代码风格是采用门级连接方式编写的Verilog代码文件。

一个示例[1]:

- 简单组合逻辑块的RTL代码:

module example(

input wire a,

input wire b,

input wire c,

output reg out

);

always @*

out = (a & b) | c;

endmodule

- 选择工艺库

选择某公司名为abc_100的xx纳米的CMOS工艺,该公司提供的工艺库中包含了以下标准单元:

VNAND//两输入与非门

VAND//两输入与门

VNOR//两输入或非门

VOR//两输入或门

VNOT//反相器

VBUF//缓冲器

NDFF//下降沿触发的DFF

PDFF//上升沿触发的DFF

- 设计约束

无面积和功耗约束,只要求优化得到最快的时序

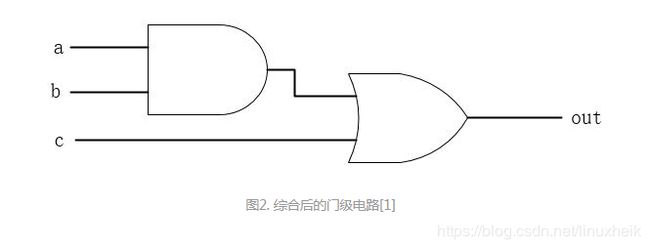

- 逻辑综合得到的门级网表:

module example_after_LS(

input wire a,

input wire b,

input wire c,

output reg out

);

wire net0;

VAND U1 (.in0(a), .in1(b), .out(net0));

VOR U2 (.in0(net0), .in1(c), .out(out));

endmodule

逻辑综合得到的门级电路

参考文献

[1] SamirPalnitkar. Verilog HDL数字设计与综合[M]. 电子工业出版社, 2004。

[2] 金西. 数字集成电路设计 : Digital integrated circuit design[M]. 中国科学技术大学出版社, 2013。

[3] 林敏, 方颖立. VHDL数字系统设计与高层次综合[M]. 电子工业出版社, 2002