NetFPGA-SUME10G以太网接口仿真问题

NetFPGA-SUME使用的是Xilinx的10G 子系统IP核心

![]()

该IP核心包含了PCS/PMA核和MAC核,方便使用,有样板工程,很有意思的是官方根据是否包含share logic分别提供了两个样板工程。example design的仿真TB文件包含了丰富的内容,模拟了 以太网64/66B编码、解码和同步的过程,对理解以太网底层原理很有帮助,1500行左右代码。想借助该TB文件仿真NetFPPGA-SUME工程中封装的10G IP核心,以便加深理解,遇到些问题:

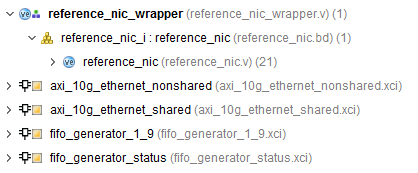

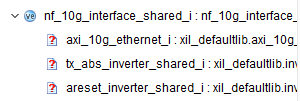

1.NetFPPGA-SUME原工程师block Design模式,而且里面的IP是使用“预定制的官方IP”(实际没有产生)结合自己代码再封装为各个IP,包括网口、PCIE等等,在创建工程时,先创建定制的官方IP,然后再生成block Design,在Vivado2006环境下这样搞,你打开再封装的IP你会发现系统找不到,“预定制的官方IP”,虽然工程里确实有,看下面两张图。明明生成了IP核,但就是找不到。

最神奇的是,整个工程综合、实现和生成bit文件都没啥问题。但是这样仿真是不行的,我试过。最后没办法,我把工程改为了非block design模式,预定制的官方IP”就可以被正常找到了。

2.10G IP核需要使用sim_speedup_control信号,原工程时没有的,需要引出。

3.example design的仿真TB文件用到了core_ready信号,该信号用来判断IP核是否就位,由MAC核PCS/PMA的状态输出向量决定,具体看example design的生成方法,需要注意的NetFPPGA-SUME工程中封装的10G IP核(nf_10g_interface_shared)对MAC核PCS/PMA的状态输出向量进行了二次处理,最好使用官方10G IP核直接出来的状态输出向量生成。

4.nf_10g_interface_shared中nf_10g_attachment用来将数据进行跨时钟域转换和位宽转换,里面用到FIFO36E1,仿真过程中报错如下:

DRC Error : Reset is unsuccessful at time 106722. RST must be held high for at least five RDCLK clock cycles, and RDEN must be low before RST becomes active high, and RDEN remains low during this reset cycle.

DRC Error : Reset is unsuccessful at time 106722. RST must be held high for at least five WRCLK clock cycles, and WREN must be low before RST becomes active high, and WREN remains low during this reset cycle.

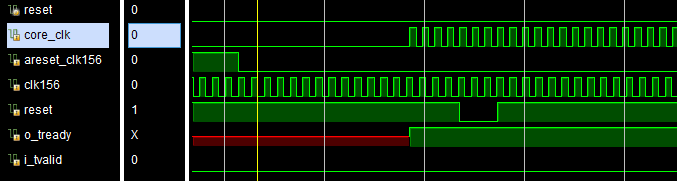

仿真看了下相关信号如下图,发现读时钟(core_clk)晚于复位信号(arest_clk156),分析了下代码,发现主要原因是因为读时钟与复位信号无关联造成,时钟是由MMCM生成,但是arest_clk156却是由10G IP核生成,于是将FIFO36E1的复位信号与MMCM的locked信号进行了关联,使用reference_nic_proc_sys_reset输出的复位信号,问题得到解决

5.原工程的复位控制用的proc_sys_reset IP核心,该IP核心不使用的输入复位信号应当悬空,之前没处理好,导致复位输出异常(见上图)

上述问题解决后,将AXIS总线进行了换回,仿真测试通过,仿真模拟网口收发数据正常