Verilog的三种描述方式(结构化描述、数据流描述、行为级描述)

Verilog对电路功能的描述有三种方式:结构化描述、数据流描述、行为级描述。三种描述方式抽象级别不同,各有优缺点,相辅相成,需要配合使用。

目录

一、结构化描述

1、概念

2、特点

3、示例

真值表:

电路抽象:

实现代码:

测试文件:

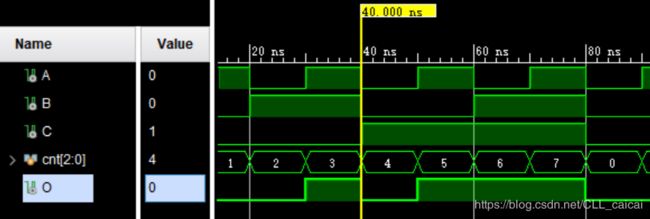

仿真结果:

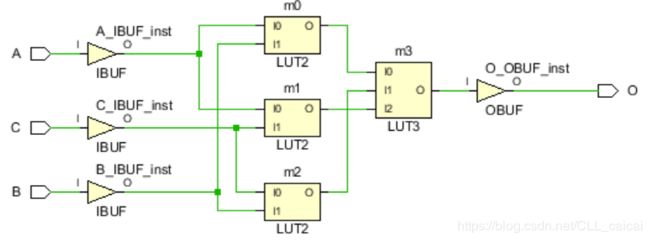

实现电路:

二、数据流描述

1、概念

2、特点

3、示例

实现代码:

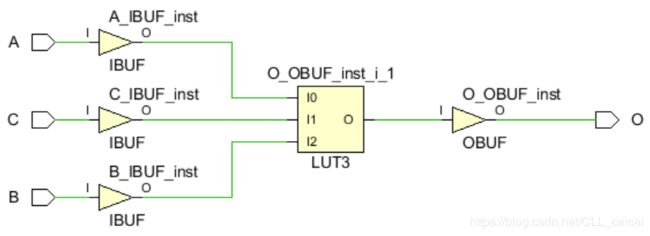

实现电路:

三、行为级描述

1、概念

2、特点

3、示例

实现代码:

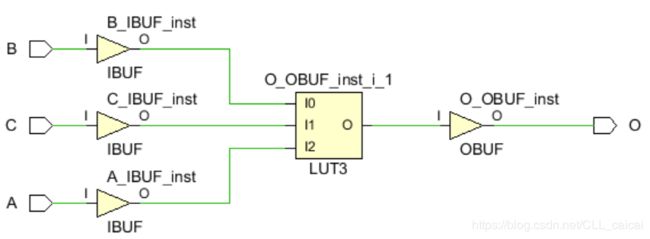

电路实现:

四、参考文献

一、结构化描述

1、概念

结构化描述的抽象级别最低,是最接近实际硬件结构的描述方式。

2、特点

- 直接采用结构化描述语句描述,需要描述实现功能所需数字电路的逻辑关系,及其复杂;

- 结构化描述语句常用于层次化模块间的调用、以及ip核的例化等;

3、示例

为简单起见,以3人投票表决器为例,按照结构化描述方式实现功能:

真值表:

3人投票表决器,只有2人及两人以上同一,输出才为1

| A | B | C | O |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

电路抽象:

要按照结构化描述来实现这一功能,首先应进行电路抽象。即先抽象出用何种电路实现这一功能,才能进行随后的描述。

经过卡诺图化简,拟采用与、非组合逻辑实现这一功能,即:

O = AB+AC+BC

实现代码:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: CLL guoliang

//

// Create Date: 2020/04/22 17:41:37

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module vote1(

input A,

input B,

input C,

output O

);

// mid signal

wire midAB;

wire midAC;

wire midBC;

// vote

AND2 m0(.O(midAB),.I0(A),.I1(B));

AND2 m1(.O(midAC),.I0(A),.I1(C));

AND2 m2(.O(midBC),.I0(C),.I1(B));

OR3 m3(.O(O),.I0(midAB),.I1(midBC),.I2(midAC));

endmodule

测试文件:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: CLL guoliang

//

// Create Date: 2020/04/22 17:53:51

//

//////////////////////////////////////////////////////////////////////////////////

module vote(

);

wire A;

wire B;

wire C;

reg [2:0]cnt;

wire O;

// 激励设置

initial

begin

cnt = 3'b000;

repeat(10) #10 cnt = cnt+3'b1;

end

assign {C,B,A} = cnt;

//实例化

vote1 minst(

.A(A),

.B(B),

.C(C),

.O(O)

);

endmodule

仿真结果:

实现电路:

可以看出,功能的电路实现与设计符合;

二、数据流描述

1、概念

数据流描述抽象级别较高,不再需要清晰的刻画具体的数字电路,而比较直观的表达底层逻辑。其又称为寄存器传输级(RTL)描述。

2、特点

- 从数据的变换和传送角度描述模块

- 抽象级别适中,即显示的表达了模块的行为,又隐式的刻画了模块的电路结构;

3、示例

同样以3人投票表决器为例,按照数据流描述方式实现功能:

实现代码:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: CLL

// //////////////////////////////////////////////////////////////////////////////////

module vote2(

input A,

input B,

input C,

output O

);

// vote

assign O = A&B | A&C | B&C;

endmodule

实现电路:

三、行为级描述

1、概念

行为级描述抽象级别最高,概括能力最强。

2、特点

- 概括能力及强,不关注电路实现,只描述数据逻辑。

- 抽象级别高,综合效率低,电路可控性差;

3、示例

同样以3人投票表决器为例,按照数据流描述方式实现功能:

实现代码:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2020/04/22 18:25:40

// Design Name:

// Module Name: vote3

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module vote3(

input A,

input B,

input C,

output reg O

);

// vote

always@(*)

begin

case({A,B,C})

3'b000:begin

O = 1'b0;

end

3'b001:begin

O = 1'b0;

end

3'b010:begin

O = 1'b1;

end

3'b011:begin

O = 1'b1;

end

3'b100:begin

O = 1'b0;

end

3'b101:begin

O = 1'b1;

end

3'b110:begin

O = 1'b1;

end

3'b111:begin

O = 1'b1;

end

default:begin

O = 1'b0;

end

endcase

end

endmodule

电路实现:

四、参考文献

《FPGA之道》