存储器的层次和结构

从不同角度对存储器进行分类:

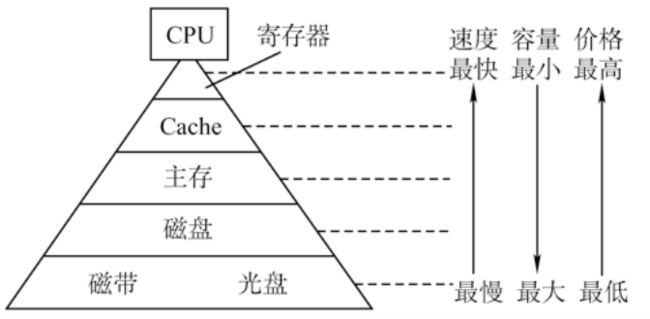

1.按在计算机中的作用(层次)分类

(1)主存储器。简称主存,又称内存储器(内存),用来存放计算机运行期间所需的大量程序和数据,CPU 可以直接随机地对其进行访问,也可以和告诉缓冲存储器(Cache)及辅助存储器交换数据,其特点是容量较小、存取速度较快、单位价格较高。

(2)辅助存储器。简称辅存,又称外存储器(外存),是主存储器的后援存储器,用来存放当前暂时不用的程序和数据,以及一些需要永久性保存的信息,它不能与 CPU 直接交换信息。其特点是容量极大、存取速度较慢、单位成本低。

(3)高速缓冲存储器。简称 Cache,位于主存和 CPU 之间,用来存放正在执行的程序段和数据,以便 CPU 能高速地使用它们。Cache 地存取速度可与 CPU 的速度匹配,但存储容量小、价格高。目前的高档计算机通常将它们制作在 CPU 中。

2.按存储介质分类

按存储介质,存储器可分为磁表面存储器(磁盘、磁带)、磁芯存储器、半导体存储器(MOS型存储器、双极型存储器)和光存储器(光盘)。

3.按存取方式分类

(1)随机存储器(RAM)。存储器的任何一个存储单元的内容都可以随机存取,而且存取时间与存储单元的物理位置无关。其优点是读写方便、使用灵活,主要用作主存或高速缓冲存储器。RAM 又分为静态 RAM (以触发器原理寄存信息,SRAM)和动态 RAM(以电容充电原理寄存信息,DRAM)。

(2)只读存储器(ROM)。存储器的内容只能随机读出而不能写入。信息一旦写入存储器就固定不变,即使断电,内容也不会丢失。因此,通常用它存放固定不变的程序、常数和汉字字库,甚至用于操作系统的固化。它与随机存储器可共同作为主存的一部分,统一构成主存的地址域。

由 ROM 派生出的存储器也包含可反复重写的类型,ROM 与 RAM 的存取方式均为随机存取。广义上的只读存储器已可已可通过电擦除等方式进行写入,其“只读”的概念没有保留,但仍然保留了断电内容保留、随机读取特性,但其写入速度比读取速度慢得多。

(3)串行访问存储器。对存储单元进行 读/写 操作时,需按其物理地址的先后顺序寻址,包括顺序存取存储器(如磁带,SAM)与直接存取存储器(如磁盘,DAM)。

顺序存取存储器的内容只能按照某种顺序存取,存取时间的长短与信息在存储体上的物理位置有关,其特点是存取速度缓慢。直接存取存储器既不像 RAM 那样随机地访问任何一个存储单元,又不像顺序存取存储器那样完全按照顺序存取,而是介于两者之间。存取信息时通常先寻找整个存储器中的某个小区域(如磁盘上的磁道),再在小区域内顺序查找。

4.按信息的可保存性分类

断电后,存储信息消失的存储器称为易失性存储器,如 RAM。断电后,信息仍然保持的信息存储器称为非易失性存储器,如 ROM、磁表面存储器和光存储器。若某个存储单元所存储的信息被读出时,原存储信息被破坏,则称为破坏性读出;若读出时,被读单元存储信息不被破坏,则称为非破坏性读出,具有破坏性读出的存储器,每次读出操作后,必须紧接一个再生的操作,以便恢复被破坏的信息。。

存储器有 3 个主要性能指标,即存储容量、单位成本和存储速度。这 3 个指标相互制约,设计存储器系统所追求的目标就是大容量、低成本和高速度。

(1)存储容量 = 存储字数 * 字长(如 1M * 8 位)。存储字数表示存储器地址空间的大小,字长表示一次存取操作的数据量。

(2)单位成本:每位价格 = 总成本 / 总容量。

(3)存储速度:数据传输率 = 数据的宽度 / 存储周期。

-

- 存取时间(Ta) :存取时间是指从启动一次存储器操作到完成该操作所经历的时间,分为读出时间和写入时间。

- 存取周期(Tm):存取周期又称读写周期或访问周期。它是指存储器进行一次完整的读写操作所需的全部时间,即连续两次独立访问存储器操作(读或写操作)之间所需的最小时间间隔。

- 主存带宽(Bm):主存带宽又称数据传输率,表示每秒从主存进出信息的最大数量,单位为 字/秒、字节/秒(B/s) 或 位/秒(b/s)。

存取时间不等于存储周期,通常存储周期大于存储时间。这是因为对任何一种存储器,在读写操作之后,总要有一段时间恢复内部状态的复原时间。对于破坏性读出的存储器,存取周期往往比存取时间大得多,因为存储器中的信息读出后需要马上进行再生。

操作系统保存在硬盘上,首先需要将其引导到主存中,而引导程序通常存放在 ROM 中,程序运行时需要进行读写操作,因此应采用 RAM。

存储器的层次化结构

为了解决存储系统大容量、高速度和低成本 3 个相互制约的矛盾,在计算机系统中,通常采用多级存储器结构,如下图所示。在图中由上至下,价位越来越低,速度越来越慢,容量越来越大,CPU 访问的频度也越来越低。

实际上,存储系统层次结构主要体现在 “Cache - 主存” 层次和 “主存 - 辅存” 层次。前者主要解决 CPU 和主存速度不匹配的问题,后者主要解决存储系统容量的问题。在存储体系中,Cache、主存能与 CPU 直接交换信息,辅存则要通过主存与 CPU 交换信息;主存与 CPU、Cache、辅存都能交换信息。

三级存储系统的层次结构及其构成

主存和 Cache 之间的数据调动是由硬件自动完成的,对所有程序员均是透明的;而主存和辅存之间的数据调动则是由硬件和操作系统共同完成的,对应用程序员是透明的。

在 “主存 - Cache” 和 “主存 - 辅存” 层次中,上一层的内容都只是下一层中内容的副本,也即 Cache(主存)中的内容只是主存(辅存)中内容的一部分。

半导体随机存储器

74138 译码器当选通端G1为高电平,另两个为低电平时,才可将地址端的二进制编码在一个对应的输出端以低电平译出。

SRAM 的工作原理

静态随机存储器(SRAM)的存储元是用双稳态触发器(六管 MOS)来记忆信息的,因此即使信息被读出后,它仍保持其原状态而不需要再生(非破坏性读出)。但是,只要电源被切断,原来的保存信息便会丢失,故它属于易失性半导体存储器。SRAM 的存取速度快,但集成度低,功耗较大,所以一般用来组成告诉缓冲存储器。

DRAM 的工作原理

动态随机存储器(DRAM)是利用存储元电路中的栅极电容上的电荷来存储信息的,常见的 DRAM 的基本存储电路通常分为三管式和单管式。DRAM 采用地址复用技术,地址线是原来的 1/2,且地址信号分行、列两次传送。相对于 SRAM 来说,DRAM 具有容易集成、价位低、容量大和功耗低等优点,但 DRAM 的存取速度比 SRAM 慢,一般用来组成大容量主存系统。

DRAM 保存的信息会自动消失(易失性存储器),为此,每隔一段时间必须刷新,通常取 2ms,这个时间称为刷新周期。常用的刷新方式有 3 种:集中刷新、分散刷新和异步刷新。

(1)集中刷新:指在一个刷新周期内,利用一段固定的时间,依次对存储器的所有行进行逐一再生,在此期间停止对存储器的读写操作,称为“死时间”,又称访存“死区”。集中刷新的优点是读写操作时不受刷新工作的影响,因此系统的存取速度较高;缺点是在集中刷新期间(死区)不能访问存储器。

(2)分散刷新:把对每行的刷新分散到各个工作周期中。这样,一个存储器的系统工作周期分为两部分:前半部分用于正常读、写或保持;后半部分用于刷新某一行。这种刷新方式增加了系统的存取周期,如存储芯片的存取周期为 0.5μs,则系统的存取周期为 1μs。分散刷新的优点是没有死区;缺点是加长了系统的存取周期,降低了整机的速度。

(3)异步刷新:异步刷新是前两种方法的结合,它既可以缩短“死时间”,又能充分利用最大刷新间隔为 2ms 的特点。具体做法是将刷新周期除以行数,得到两次刷新操作的时间间隔 t,利用逻辑电路每隔时间 t 产生一次刷新请求。这样可以避免使 CPU 连续等待过长的时间,而且减少了刷新次数,从根本上提高了整机速度。

DRAM 的刷新需注意以下问题:(1)刷新对 CPU 是透明的,即刷新不依赖外部的访问;(2)动态 RAM 的刷新单位是行,故刷新操作时仅需要行地址;(3)刷新操作类似于读操作,但又有所不同。刷新操作仅给栅极电容补充电荷,不需要信息输出。另外,刷新时不需要选片,即整个存储器中的所有芯片同时被刷新。

SRAM 和 DRAM 都满足断电内容消失,但需要刷新的只有 DRAM,而 SRAM 不需要刷新。

| 特点 \ 类型 | SRAM | DRAM |

| 存储信息 | 触发器 | 电容 |

| 破坏性读出 | 非 | 是 |

| 需要刷新 | 不要 | 需要 |

| 送行列地址 | 同时送 | 分两次送 |

| 运行速度 | 快 | 慢 |

| 集成度 | 低 | 高 |

| 发热量(功耗) | 大 | 小 |

| 存储成本 | 高 | 低 |

| 主要用途 | 高速缓存 | 主机内存 |

ROM 器件有两个显著的优点:

(1)结构简单,所以位密度比可读写存储器高。

(2)具有非易失性,所以可靠性高。

根据制造工艺不同,ROM 可分为掩膜式只读存储器(MROM)、一次可编程只读存储器(PROM)、可擦除可编程只读存储器(EPROM)、闪速存储器(Flash Memory)和固态硬盘(Solid State Drives)。

MROM 写入后任何人无法改变其内容。PROM 允许用户利用专门的设备(编程器)写入自己的程序,一旦写入,内容就无法改变。EPROM不仅可以由用户利用编程器写入信息,而且可以对其内容进行多次改写。需要修改 EPROM 内容时,先将其全部内容擦除,然后编程。

主存容量的扩展:位扩展法,字扩展法,字位同时扩展法。

双端口 RAM 和多模块存储器

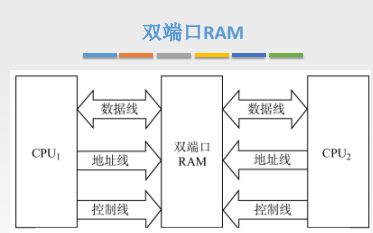

双端口 RAM 是指同一个存储器有左、右两个独立的端口,分别具有两组相互独立的地址线、数据线和控制线,允许两个独立的控制器同时异步地访问存储单元。当两个端口的地址不相同时,在两个端口上进行读写操作一定不会发生冲突。

两个端口同时存取存储器地同一地址单元时,会因数据冲突造成数据存储或读取错误。两个端口对同一主存操作有以下4 种情况:

- 两个端口不同时对同一地址单元存取数据。

- 两个端口同时对同一地址单元读出数据。

- 两个端口同时对同一地址单元写入数据。

- 两个端口同时对同一地址单元操作,一个写入数据,另一个读出数据。

其中,第 1 种和第 2 种情况不会出现错误;第 3 种情况会出现写入错误;第 4 种情况会出现读出错误。

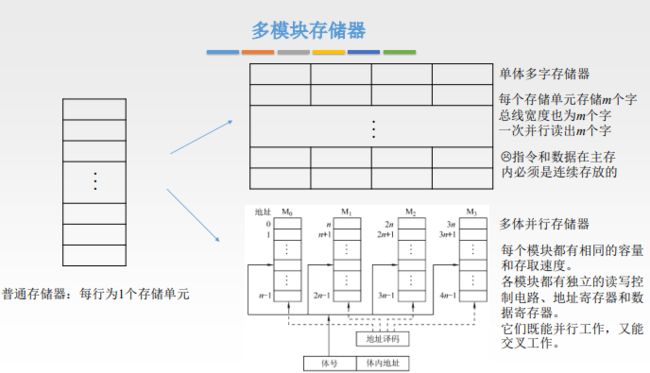

为提高访存速度,常采用多模块存储器,常用的有单体多字存储器和多体低位交叉存储器。

1.单体多字存储器

单体多字系统的特点是存储器中只有一个存储体,每个存储单元存储 m 个字,总线宽度也为 m 个字。一次并行读出 m 个字,地址必须顺序排列并处于同一存储单元。

单体多字系统在一个存取周期内,从同一地址取出 m 条指令,然后将指令逐条送至 CPU 执行,每隔 1/m 存取周期,CPU 向主存取一条指令。这增大了存储器的带宽,提高了单体存储器的工作速度。

缺点:指令和数据在主存内必须是连续存放的,一旦遇到转移指令,或操作数不能连续存放,这种方法的效果就不明显。

2.多体并行存储器

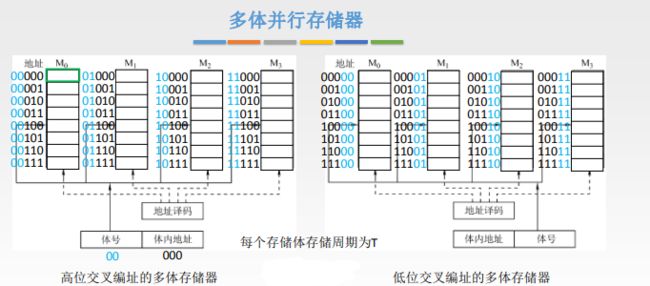

多体并行存储器由多体模块组成。每个模块都有相同的容量和存取速度,各模块都有独立的读写控制电路、地址寄存器和数据寄存器,它们既能并行工作,又能交互工作。多体并行存储器分为高位交叉编址(顺序方式)和低位交叉编址(交叉方式)两种。

(1)高位交叉编址:高位地址表示体号,低位地址为体内地址。采用高位交叉编址方式的存储器仍是顺序存储器。

(2)低位交叉编址:低位地址为体号,高位地址为体内地址。由于程序连续存放在相邻体中,因此采用此编址方式的存储器称为交叉存储器。

多体模块结构的存储器采用低位交叉编址后,可在不改变每个模块存取周期的前提下,采用流水线的方式并行存取,提高存储器的带宽。

高速缓冲存储器

高速缓冲技术是利用程序访问的局部性原理,把程序中正在使用的部分存放在一个高速的、容量较小的Cache中。使 CPU 的访存操作大多数针对 Cache 进行,从而大大提高程序的执行速度。

Cache 位于存储器层次结构的顶层,通常由 SRAM 构成。

CPU 与 Cache 之间的数据交换以字为单位,而 Cache 与主存之间的数据交换则以 Cache 块为单位。

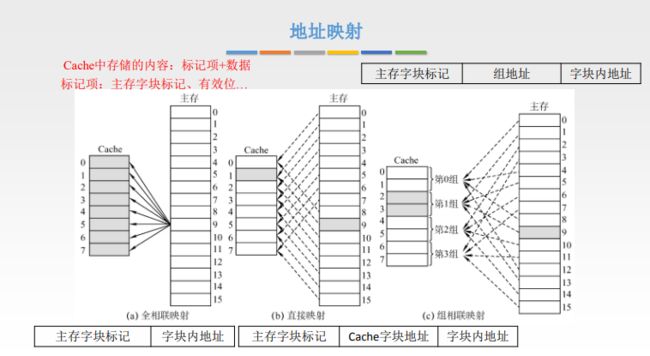

在Cache 中,地址映射是指把主存地址空间映射到 Cache 地址空间,即把存放在主存中的程序按照某种规则装入Cache。地址映射不同于地址变换。地址变换是指 CPU 在访存时,将主存地址按映射规律换算成 Cache 地址的过程。地址映射的方式有以下 3 种。

1.直接映射

主存数据块只能装入 Cache 中唯一的位置。若这个位置已有内容,则产生块冲突,原来的块将无条件地被替换出去(无须使用替换算法)。直接映射的块冲突概率最高,空间利用率低。直接映射的关系可定义为 j = i mod 2c

直接映射的地址结构为

| 主存字块标记 | Cache 字块地址 | 字块内地址 |

2.全相联映射

可以把主存数据块装入 Cache 中的任何位置。

全相联映射的地址结构为

| 主存字块标记 | 字块内地址 |

3.组相联映射

将 Cache 空间分成大小相同的组,主存的一个数据块可以装入一组内的任何一个位置,即组间采取直接映射,而组内采取全相联映射。两个 Cache 块为一组即二路组相联。

组相联映射的地址结构为

| 主存字块标记 | 组地址 | 字块内地址 |

Cache 总容量包括:存储容量、标记列阵容量(有效位、标记位、一致性维护位、替换算法控制位)。

每个 Cache 行对应一个标记项(有效位、标记位……)

Cache 中主存块常用的替换算法有随机(RAND)算法、先进先出(FIFO)算法、近期最少使用(LRU)算法和最不经常使用(LFU)算法。与操作系统算法类似,不再赘述。

Cache 中的内容是主存块的副本,当对 Cache 中的内容进行更新时,就需选用写操作策略,使 Cache 内容和主存内容保持一致。此时分两种情况:

对于 Cache 写命中(write hit),有两种处理方法。

(1)全写法(写直通法、write - through)。当 CPU 对 Cache 写命中时,必须把数据同时写入 Cache 和主存。

(2)写回法(write - back)。当 CPU 对 Cache 写命中时,只修改 Cache 的内容,而不立即写入主存,只有当此块被换出时才写回主存。这种方法减少了访存次数,但存在不一致的隐患。采用这种策略时,每个 Cache 行必须设置一个标志位(脏位),以反应此块是否被修改过。

对于 Cache 不命中,也有两种处理方法

(1)写分配法(write - allocate)。加载主存中的块到 Cache 中,然后更新这个 Cache 块。它试图利用程序的空间局部性,但缺点是每次不命中都需要从主存中读取一块。

(2)非写分配法(not - write - allocate)。只写入主存,不进行调块。

Cache的写命中和写未命中,就是磁盘或者内存上的存储区域之前有没有写过数据。如果有,这次再写到相同的区域叫写命中;如果写到其他区域,叫写未命中。

非写分配法常与全写法合用,写分配法通常和写回法合用。

对于由高速缓存、主存、硬盘构成的三级存储体系,CPU 访问该存储系统时发送的地址为主存物理地址。当 CPU 访存时,先要到 Cache 中查看该主存地址是否在 Cache 中,所以发送的是主存物理地址。只有在虚拟存储器中,CPU 发出的才是虚拟地址。磁盘地址是外存地址,外存中的程序由操作系统调入主存中,然后在主存中执行,因此 CPU 不可能直接访问磁盘。

采用 指令Cache 和 数据Cache 分离的主要目的是减少指令流水线的资源冲突。

局部性原理的基本含义是:在程序执行过程中,程序对主存的访问是不均匀的(即局部)。

页式虚拟存储方式和段页式都以页为单位和主存交互。

虚存对应用程序员透明,对系统程序员不透明。

在虚拟存储器中,当程序正在执行时,由操作系统完成地址映射。

若 Cache 行长太大,Cache 项数变少,因而命中的可能性减小。

以上内容均来自王道书籍及相关课程等