DC(Design Compile)如何使用

Design Compile 是 synopsys 的综合软件,它的功能是把 RTL 级的代码转化为门级网表。

综合包括:

- 转译(translation),在转译的过程中,软件自动将源代码翻译成每条语句所对应的功能模块以及模块之间的拓扑结构,这一过程是在综合器内部生成电路的布尔函数的表达,不做任何的逻辑重组和优化。

- 优化(Opitimization),基于所施加的一定时序和面积的约束条件,综合器按照一定的算法对转译结果作逻辑优化和重组。

- 映射(Mapping),在映射过程中,根据所施加的一定的时序和面积的约束条件,综合器从目标工艺库中搜索符

合条件的单元来构成实际电路。

DC有两种界面:

(1)图形界面,通过design vision&调用出来

(2)命令行界面,通过dc_shell-t调用

因为门级和代码级不同,代码级考虑的是理想情况,但是实际电路不是这样的,它有门级的延时,线的延时,信号的转换时间,甚至时钟信号到达各个触发器的时间不相等。基于这些考虑, DC 通过施加约束,模拟实际环境,根据实际情况得出门级网表。 因此如何适当的施加约束是 DC 的关键所在。

(二)库的配置

DC所用的工艺库是.db或者.lib格式的,其中.lib 格式的文件是可读得,通过此文件可以了解库的详细信息,比如说工作电压,操作温度,工艺偏差等等。 .db 格式的库是二进制的,不可读。 .db 格式的库由.lib 格式的库通过命令 read_lib 生成。

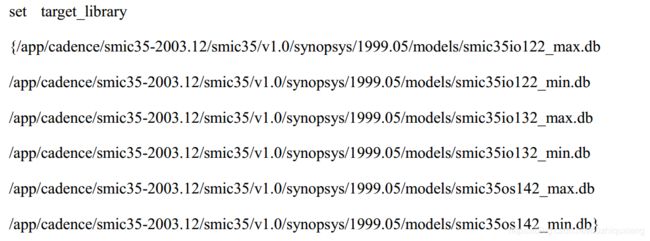

1、目标工艺库(Target_library)

是指将 RTL 级的 HDL 描述到门级时所需的标准单元综合库,它是由芯片制造商(Foundry)提供的,包含了物理信息的单元模型。一般有:与非,或非,非门等基本的逻辑单元;还有选择器,与或非,或与非等较复杂的组合逻辑,以及锁存器 (LATCH)和触发器(DFF)等时序逻辑单元。

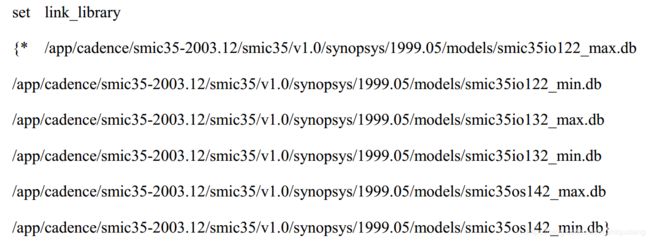

2、链接库(link_library)

链接库可以是同 target_library 一样的单元库,或者是已综合到门级的底层模块设计,其作用如下:在由下而上的综合过程中,上一层的设计调用底层已综合模块时,将从 link_library中寻找并链接起来(设置里面不仅有Target library,还有其他东西,例如IP核)。

如果需要将已有的设计从一个工艺 A 转到另一个工艺 B 时,可以将当前单元综合库 A 设为link_library,而将单元综合库 B 设为 target_library,重新映射一下即可

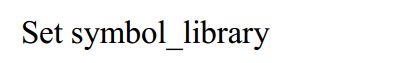

3、符号库(symbol_library)

显示电路时,用于标识器件,单元的符号库

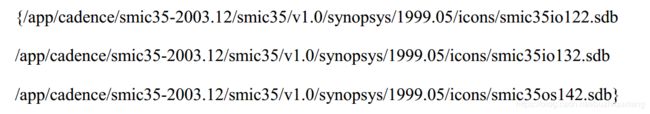

搜寻路径(search_path)(包括综合库和设计文件)

setup文件:一般包含初始化参数变量、设计工艺库名称及路径等相关内容

分析工艺库,得出相关信息

芯片供应商提供的库通常有 max,type,min 三种类型,代表操作环境为最坏(worst),典型(type),最好(best)三种情况。芯片的操作环境包括:操作温度,供电电压,制造工艺偏差和RC 树模型。

导线负载模型(导线也具有电阻和电容,也会有延时)

库里面对每个单元都有描述,比如该单元的功能,时间,面积等等。除此之外,对于单元的每个引脚还提供有设计规则约束(DRC), 这些值由设计工艺决定,只有满足这些条件的单元在运行时才会操作正常,因此在设计中有很高的权重。

延时计算最常见的是 CMOS 非线性查找表模型。

工艺库文件的配置放在三个地方,A:软件安装目录$SYNOPSYS/admin/setup。B:~user,用户安装目录。C:DC startup directory前两个目录是早已配置好,最好不要动的;第三个目录放在工作目录下的隐藏目录:.synopsys_dc.setup,通过ls -al才能看到此文件。

时序约束的基本知识:

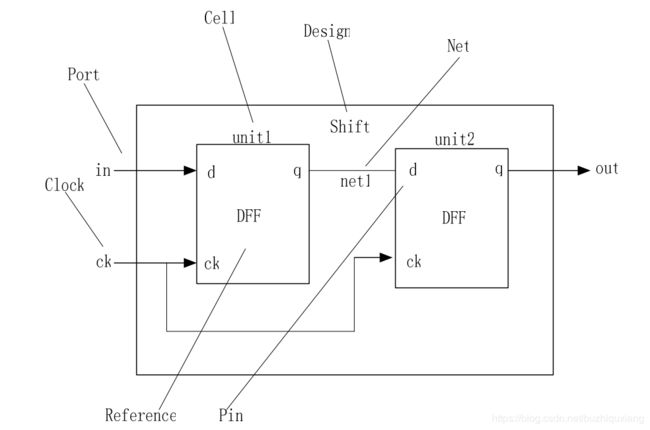

约束对象:

静态时序分析:

不需要使用动态仿真,提取整个电路的所有时序路径,通过计算信号沿在路径上的延迟传播,找出违背时序约束的主要错误。用于检查建立时间和保持时间是否满足时序要求。

与动态仿真相比,静态时序分析具有耗时短,不需要加激励,所耗资源小,可以穷尽所有路径等优点。但是静态时序分析存在的问题在于不了解电路的动态行为,并且受到伪路径的困扰,因此目前只用于同步电路。

1、建立时间(setup time):数据在时钟信号源到达之前必须要稳定的时间

2、保持时间(hold time):数据在时钟信号源到达之后必须要稳定的时间

3、基本单元的延时(Td):对于所有的电路,电信号通过都需要时间,这在逻辑电路中反映为信号的延时,在时序逻辑单元中,反映为从时钟沿开始,到数据输出需要的时间。

4、连线的延时:信号除了在基本单元中有延时,在连线中也有延时,因为连线也有电容电阻

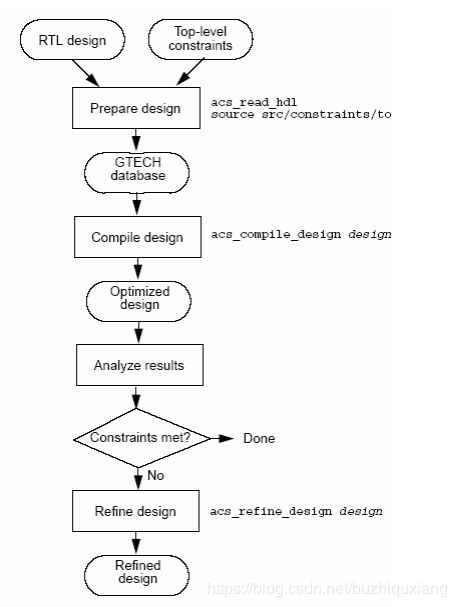

逻辑综合的概述

对于ASIC,使用DC工具;对于FPGA,使用ISE,QUARTUS都可

(1)Translation

主要把描述RTL级的HDL语言,在约束下转换成DC内部的同意用门级描述的电路,以GTECH或者没有映射的ddc形式展现

(2)logic optimization

逻辑优化,就是把统一用门级描述的电路进行优化,例如把路径调整一下,门改一下

(3)Gate mapping

门级映射,DC用工艺库把电路给映射出来,得到一个ddc文件;包括映射的门电路信息与网表,.v格式的网表,延时信息(sdf),工作约束(sdc);.ddc这个包含的网表文件是实际意义的网表文件,而.v这个形式的网表是用来做后仿真的文件。

求延迟的方式:

(1)线负载模式:将负载等效成RC模型,得到延迟信息;但延迟包括互连线延迟和基本单元延迟,所以有误差

(2)拓扑模式:在DC综合中通过物理库,预布局吐出脚本约束,得到延迟信息。

综合目标:area,delay(性能)的trade off

一般有两种文件,后缀名为lib(人看,可转化为db文件)和db(工具读)

例如:

set target_library 22nm.db

set_app_var target_library 22nm.db #对于DC内部原变量,最好使用第二种方法,set_app_var会检查变量拼写是否为内部变量,若拼写错误,则出现error。

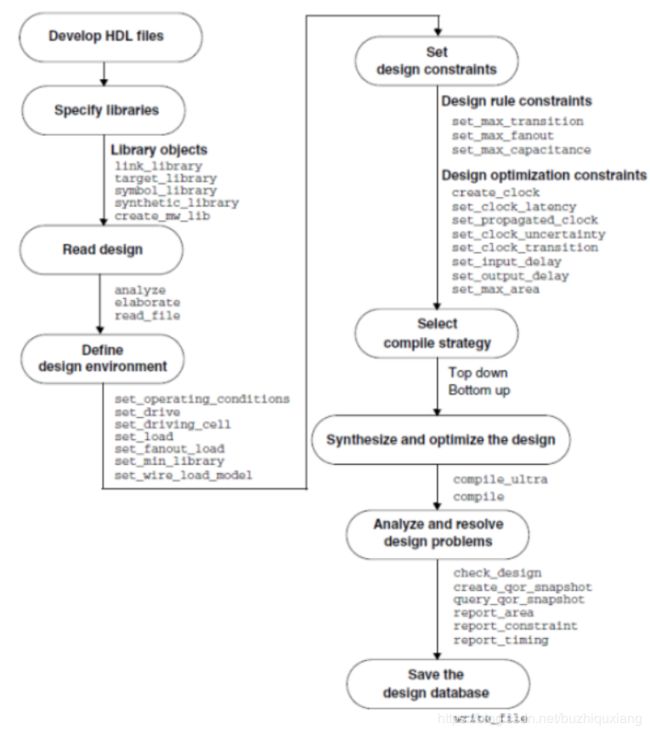

(1)准备设计文件,DC 的设计输入文件一般为 HDL 文件

(2)指定库文件

(3)读入设计:设计的读入过程是将设计文件载入内存,并将其转换为 DC 的中间格式,即GTECH 格式,GTECH 格式由“soft macros” 如 adders, comparators 等组成,这些组件来自 synopsys 的 synthetic lib,每种组件具有多种结构。

(4)定义设计环境: 定义对象包括工艺参数(温度、电压等),I/O 端口属性(负载、驱动、扇出), 统计 wire-load 模型,设计环境将影响设计综合及优化结果。

(5)设置设计约束:设计约束包括设计规则约束和优化约束,设计规则约束(design rule constraint)由工艺库决定,在设计编译过程中必须满足,用于使电路能按功能要求正常工作。设计优化约束定义了 DC 要达到的时序和面积优化目标,该约束由用户指定,DC 在不违反设计规则约束的前提下,遵循此约束综合设计。

(6)选择编译策略:

对于层次化设计,DC 中有两种编译策略供选择,分别为 top down 和 bottom up。在 top down 策略中,顶层设计和子设计在一起编译,所有的环境和约束设置针对顶层设计,虽然此种策略自动考虑到相关的内部设计,但是此种策略不适合与大型设计,因为 top down 编译策略中,所以设计必须同时驻内存,硬件资源耗费大。在 bottom up 策略中,子设计单独约束,当子设计成功编译后,被设置为 dont_touch 属性,防止在之后的编译过程中被修改,所有同层子设计编译完成后,再编译之上的父设计,直至顶层设计编译完成。Bottom up 策略允许大规模设计,因为该策略不需要所有设计同时驻入内存。

(7)编译:

用 Compile 命令执行综合与优化过程,还可以利用一些选项指导编译和优化过程。

(8)分析及解决设计中存在的问题 :

DC可以产生一些报告以反应设计的综合和优化结果,如:时序、面积、约束等报告,这些报告有助于分析和解决设计中存在的问题以改善综合结果,我们还可以利用 check_design 命令检验综合的设计的一致性。

(9)存储设计数据:

DC不会自动存储综合后的设计结果,因而需要在离开 DC 时手动存储设计数据。比如存储网表、延时信息等数据文件,ddc文件。

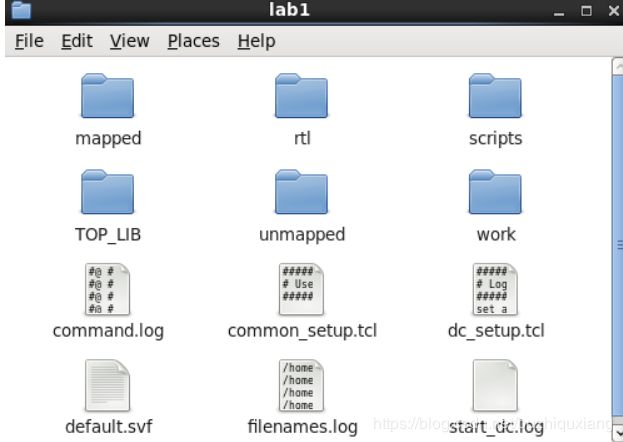

1:准备好rtl代码(放在rtl文件夹里),约束文件(scripts里),库文件(.synopsys_dc.setup)

$ ls -al #可以看到.synopsys_dc.setup文件,gvim打开该文件

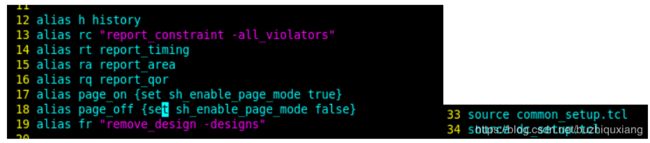

12-19行,alias命令是对后面的变量起简称;

33-34行,source命令,在当前命令下引用该文件;

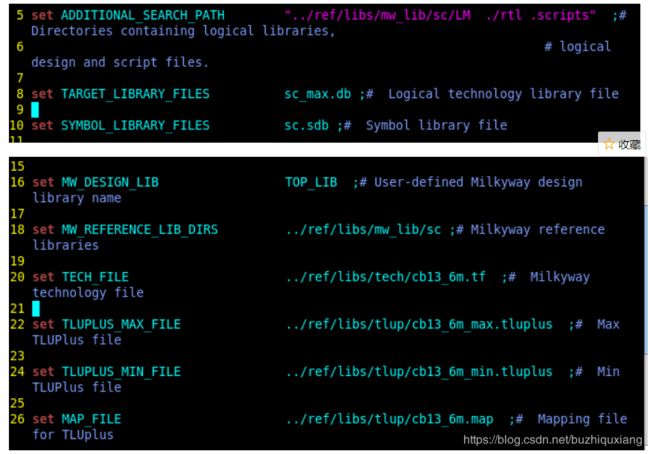

打开common_setup.tcl文件,如下图

common_setup.tcl文件定义了库的名字和名称,上面是逻辑库,下面物理库:

5行:定义库的搜索路径,当找不到库时,从这个路径中寻找

8行:定义target library使用的库(注意,只是定义一个变量)

10行:定义图形库变量

15行:定义顶层设计库的变量名称

17行:定义milkyway(参考)库(的位置)

19行:定义工艺库(的位置)

21行:定义寄生参数库(的位置)

23行:定义工艺库和寄生参数库的映射关系库(的位置)

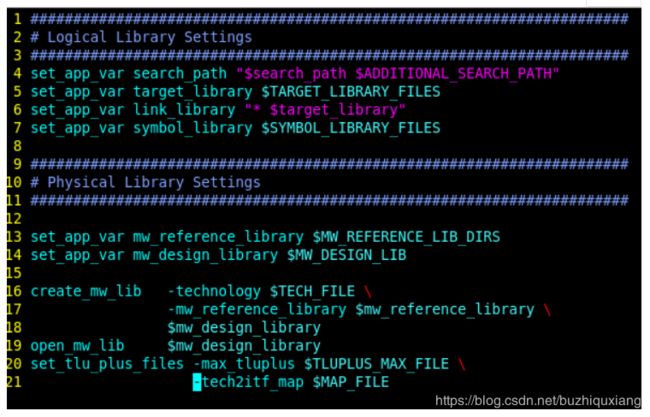

打开dc_setup.tcl文件,如下图

dc_setup.tcl文件就是指定库了,而不是单单地定义了,set_app_var是定义DC内部变量,4~7这是指定搜索路径个各种库的路径和名称

4行:search_path搜索路径

下面的物理库设置中:

13行:指定milkyway(参考)库的名称

14行:指定当前设计的库的名称

16行:创建milkyway库,格式如图上面,需要工艺库、参考、当前设计库

19行:打开当前的设计库

20行:加载寄生参数(库)

2、启动DC

3、读代码前的检查

- 检查库是否正确设置

- 检查逻辑库和物理库的一致性(检查可能不会通过,结果不影响综合的话,可以忽略)

- 检查寄生参数文件和工艺库文件的一致性:(物理综合的时候需要检查)

4、读入代码和查看设计

- 读入代码

read file - format verilog ./rtl/TOP.v

- 读入代码后,查看顶层设计

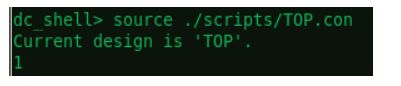

- link设计:查看当前综合的设计是否缺少子模块,返回值为1,说明子模块完整。

- 检查当前设计的连接性层次性(设计是否有问题)check_design:check_design 返回值为1则正确

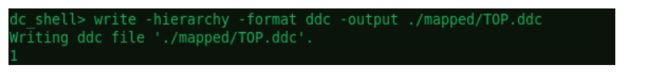

- 以ddc的格式保存未映射的设计(注意需要先创建unmapped文件夹,但每次改变verilog时,都要重新刷新此句)

Write -hierarchy -f ddc -out unmapped/TOP.ddc

- 查看内存中的设计与库

compile_ultra

7、 综合后的检查(检查不通过的需要优化,这里只作为一般流程,没有进行优化)

report_constraint -all (查看是否违规)

report_timing (查看时序报告)

report_timing -delay_type max ;#查看最差路径

report_area (查看面积情况)