6-1设备管理IO组成IO软件

一、I/O系统

1.I/O系统的组成

3.I/O系统的基本功能

- 隐藏物理设备细节,方便用户

- 实现设备无关性,方便用户

- 提高处理机和设备的并行性

- 对I/O设备进行控制

- 确保对设备正确共享

- 错误处理

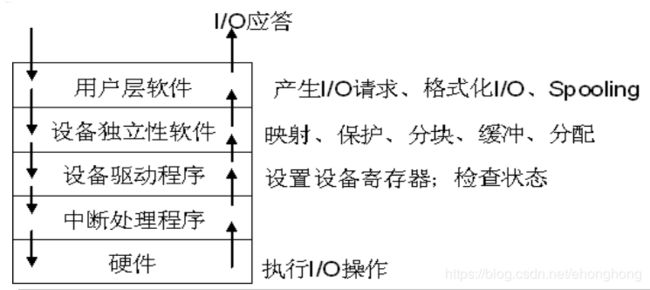

4.I/O系统的层次结构和模型

- 层次结构:系统中的设备管理模块分为若干个层次

- 层间操作:下层为上层提供服务,完成输入输出功能中的某些子功能,并屏蔽功能实现的细节。

5.I/O系统接口

- 块设备:数据的存取和传输都是以数据块为单位的设备。基本特征是传输速率较高、可寻址。磁盘设备的I/O常采用DMA方式。

- 流设备接口:数据的存取和传输是以字符为单位的设备。如键盘、打印机等。基本特征是传输速率较低、不可寻址,常采用中断驱动方式。

- 网络通信接口:操作系统必须提供相应的网络软件和网络通信接口,使得计算机能通过网络与网络上的其它计算机进行通信,或上网浏览。

6.I/O设备中的接口

与控制器的接口有三种类型的信号:

- 数据信号线(进出数据转换、缓冲后传送)

- 控制信号线(读\写\移动磁头等控制)

- 状态信号线

7.I/O设备的分类 - 按传输速率分类: 低速、中速、高速(键盘、打印机、磁盘)

- 使用:存储设备、输入输出设备

- 按信息交换的单位分类: 块设备:有结构、速率高、可寻址、DMA方式控制 字符设备:无结构、速率低、不可寻址、中断方式控制

二、设备控制器

1.关于设备管理:

- 管理对象*: I/O设备和相应的设备控制器(I/O系统组成)

- 基本任务*: 完成用户提出的I/O请求, 提高I/O速率、改善I/O设备的利用率。 为更高层进程方便使用设备提供手段

2.设备控制器的基本功能

- 接收和识别CPU命令(控制寄存器:存放命令和参数)

- 标识和报告设备的状态(状态寄存器)

- 数据交换(数据寄存器)

- 地址识别(控制器识别设备地址、寄存器地址。地址译码器)

- 数据缓冲(协调I/O与CPU的速度差距)

- 差错控制

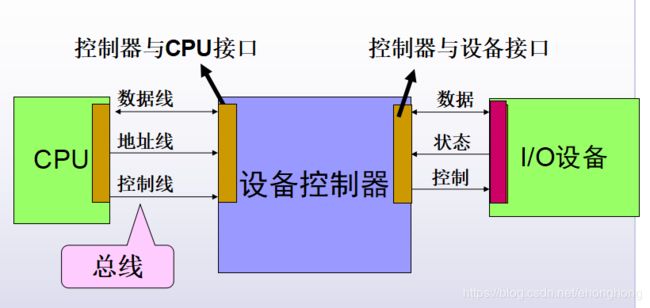

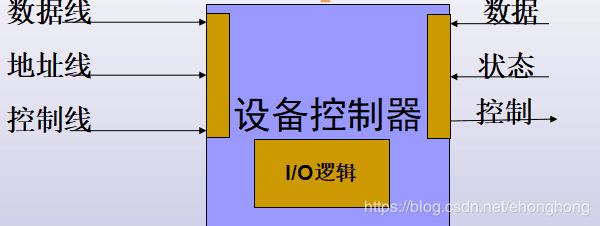

3.设备控制器组成

- 设备控制器与处理机的接口

- 设备控制器与设备的接口

- I/O逻辑

- 通过一组控制线与处理机交互

- CPU要启动一个设备时, 将启动命令发送给控制器; 同时通过地址线把地址发送给控制器

控制器的I/O逻辑对收到的地址和命令进行译码,再根据所译出的命令选择设备进行控制。

4.CPU要启动一个设备时,

将启动命令发送给控制器;

同时通过地址线把地址发送给控制器

控制器的I/O逻辑对收到的地址和命令进行译码,再根据所译出的命令选择设备进行控制。

5.处理机与设备控制器间

实现CPU与设备控制器之间的通信。

共有三类信号线:

数据线:数据线通常与两类寄存器相连接,第一类是数据寄存器;第二类是控制/状态寄存器。

地址线

控制线

6.I/O通道——CPU和设备控制器之间增设一个硬件机构

主要目的:建立更独立的I/O操作,解放CPU。

7.通道类型

根据其控制的外围设备的不同类型,信息交换方式也可分为以下三种类型:

- 字节多路通道

- 数组选择通道

- 数组多路通道

三、中断机构和中断处理程序

1.中断和陷入

- 中断:CPU对I/O设备发来的中断信号的一种响应,中断是由外部设备引起的,又称外中断。

- 陷入:由CPU内部事件所引起的中断,通常把这类中断称为内中断或陷入(trap)。

2.对多中断源的处理方式

- 屏蔽(禁止)中断:

- 嵌套中断

3.中断处理流程 - 测定是否有未响应的中断信号

- 保护被中断进程的CPU环境

- 转入相应的设备处理程序

- 中断处理

- 恢复CPU的现场

四、I/O控制方式

数据走向:设备(磁盘)–控制器缓冲—进程的内存

- 1.程序I/O方式(忙—等待方式)

向控制器发送一条I/O指令;启动输入设备输入数据;把状态寄存器busy=1。

然后不断测试标志。为1:表示输入机尚未输完一个字,CPU继续对该标志测 试;直到为0:数据已输入控制器数据寄存器中。

CPU取控制器中的数据送入内存单元,完成一个字的I/O 。

高速CPU空闲等待低速I/O设备,致使CPU极大浪费。

- 2.中断驱动I/O方式

CPU向相应的设备控制器发出一条I/O命令,然后立即返回继续执行任务。

设备控制器按照命令的要求去控制指定I/O设备。

这时CPU与I/O设备并行操作。

I/O设备输入数据中,无需CPU干预,因而可使CPU与I/O设备并行工作。从而提高了整个系统的资源利用率及吞吐量。

- 3.直接存储器访问DMA 方式(适用于读一个连续的数据块)

特点:

数据传输的基本单位是数据块;

所传送的数据是从设备直接送入内存的,或者直接从内存进设备;不需要CPU操作。

CPU干预进一步减少:仅在传送一个或多个数据块的开始和结束时,才需CPU干预,整块数据的传送是在控制器的控制下完成的。

DMA控制器的组成:

主机与DMA控制器的接口;

DMA控制器与块设备的接口;

I/O控制逻辑。

DMA控制器中的寄存器:

数据寄存器DR:暂存设备到内存或从内存到设备的数据。

内存地址寄存器MAR:它存放把数据从设备传送到内存的起始的目标地址或内存原地址。

数据计数器DC:存放本次CPU要读或写的字(节)数。

命令/状态寄存器CR:用于接收从CPU发来的I/O命令或有关控制和状态信息。

工作过程:

CPU先向磁盘控制器发送一条读命令。

该命令被送到命令寄存器CR中,同时发送数据读入到内存的起始地址,该地址被送入MAR中;

要读数据的字数则送入数据计数器DC中;

将磁盘中的数据原地址直接送入DMA控制器的I/O控制逻辑上,按设备状态启动磁头到相应位置。

启动DMA控制器控制逻辑开始进行数据传送

DMA控制器读入一个数据到数据寄存器DR中,然后传到内存MAR地址中;

接着MAR+1,DC-1,判断DC是否为0,如否,继续,反之控制器发中断请求,传送完毕。

4.I/O通道控制方式

DMA适用于读一个连续的数据块;

再进一步减少CPU的干预(减少中断), 引入通道。

实现对一组数据块的读(写)及有关的控制和管理为单位的干预。

此时,CPU只需发一条I/O指令,给出通道程序的首地址及要访问设备即可。

5.通道程序

- 通道是一种通过执行通道程序管理I/O操作的控制器,它使主机(CPU和内存)与I/O操作之间达到更高的并行程度。

通道 通过执行通道程序,与设备控制器共同实现对I/O设备的控制。

CPU指令——>设备驱动程序解读——>通道程序——>通道

五、设备独立性(无关性)

1.用户编程时所用的设备名(逻辑上的)与实际物理设备无关;

2.好处

设备分配时的灵活性

易于实现I/O重定向

3.逻辑设备名到物理设备名的映射

a.逻辑设备表LUT(Logical Unit Table)

b.LUT的设置问题

整个系统设置一张LUT(设备重名问题)

为每个用户设置一张LUT,记入各自PCB。

4.设备分配

- 所需数据结构:

设备控制表(DCT)

控制器控制表(COCT)

通道控制表(CHCT)

系统设备(总)表(SDT)

- 独占设备的分配过程

基本分配步骤(一个有通道的例子):

分配设备:

根据请求设备名,查找SDT,找到DCT;

状态、安全性等因素都可能导致本申请进程阻塞,挂入DCT等待队列中。

分配控制器

通过1步分配设备后,从DCT找到COCT;

检查COCT状态字,若忙碌,进程PCB挂到其等待队列

分配通道

COCT找到CHCT

判断状态,…

当上述三步都通过后,才可启动设备进行数据传输