S5PV210开发 -- TTL和CMOS电平

接着 S5PV210开发 -- UART 详解 来讲,里面提到 TTL和RS232电平。

RS232 电平

逻辑1:-3V~-15V

逻辑0:+3V~+15V

TTL 电平

逻辑1:+2V~+5V

逻辑0:+0V~+0.8V

一、什么是逻辑电平

要了解逻辑电平的内容,首先要知道以下几个概念的含义:

1:输入高电平(Vih):保证逻辑门的输入为高电平时所允许的最小输入高电平,当输入电平高于Vih时,则认为输入电平为高电平。

2:输入低电平(Vil):保证逻辑门的输入为低电平时所允许的最大输入低电平,当输入电平低于Vil时,则认为输入电平为低电平。

3:输出高电平(Voh):保证逻辑门的输出为高电平时的输出电平的最小值,逻辑门的输出为高电平时的电平值都必须大于此Voh。

4:输出低电平(Vol):保证逻辑门的输出为低电平时的输出电平的最大值,逻辑门的输出为低电平时的电平值都必须小于此Vol。

5:阈值电平(Vt):数字电路芯片都存在一个阈值电平,就是电路刚刚勉强能翻转动作时的电平。它是一个界于Vil、Vih之间的电压值,对于CMOS电路的阈值电平,基本上是二分之一的电源电压值,但要保证稳定的输出,则必须要求输入高电平> Vih,输入低电平

对于一般的逻辑电平,Vih,Vil,Voh,Vol以及Vt的关系可表示如下:

Voh> Vih > Vt > Vil > Vol。

6:Ioh:逻辑门输出为高电平时的负载电流(为拉电流)。

7:Iol:逻辑门输出为低电平时的负载电流(为灌电流)。

8:Iih:逻辑门输入为高电平时的电流(为灌电流)。

9:Iil:逻辑门输入为低电平时的电流(为拉电流)。

门电路输出极在集成单元内不接负载电阻而直接引出作为输出端,这种形式的门称为开路门。开路的TTL、CMOS、ECL门分别称为集电极开路(OC)、漏极开路(OD)、发射极开路(OE),使用时应审查是否接上拉电阻(OC、OD门)或下拉电阻(OE门),以及电阻阻值是否合适。对于集电极开路(OC)门,其上拉电阻阻值RL应满足下面条件:

(1): RL < (VCC-Voh)/(n*Ioh+m*Iih)

(2):RL > (VCC-Vol)/(Iol+m*Iil) 其中n:线与的开路门数;m:被驱动的输入端数。

常用的逻辑电平:有 TTL、CMOS、LVTTL、ECL、PECL、GTL;RS232、RS422、LVDS等。

·其中TTL和CMOS的逻辑电平按典型电压可分为四类:5V系列(5V TTL和5V CMOS)、3.3V系列,2.5V系列和1.8V系列。

5V TTL 和 5V CMOS逻辑电平是通用的逻辑电平。

3.3V及以下的逻辑电平被称为低电压逻辑电平,常用的为LVTTL电平。

低电压的逻辑电平还有2.5V和1.8V两种。

ECL/PECL和LVDS是差分输入输出。

RS-422/485和RS-232是串口的接口标准,RS-422/485是差分输入输出,RS-232是单端输入输出。

二、TTL

参看:TTL -- 维基百科

晶体管-晶体管逻辑(英语:Transistor-Transistor Logic,缩写为TTL),是市面上较为常见且应用广泛的一种逻辑门数字集成电路,由电阻器和晶体管而组成。TTL最早是由德州仪器所开发出来的,现虽有多家厂商制作,但编号命名还是以德州仪器所公布的资料为主。其中最常见的为74系列。

(1)TTL电压准位:

使用标准供电电压5V的TTL电压准位规范

- 输入电压准位

- Hi输入电压:2.0V以上

- Low输入电压:0.8V以下

- 输出电压准位

- Hi输出电压:2.4V以上

- Low输出电压:0.4V以下

- 由以上规范可以算出:前一级输出至次一级输入电压准位间,可以容忍的噪声边际电压是0.4V。

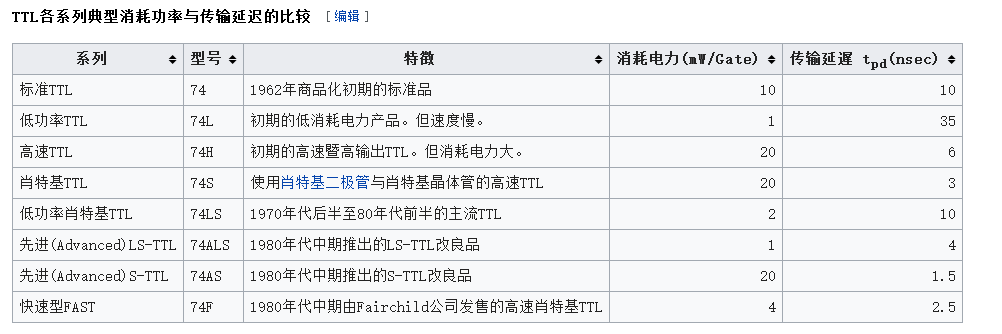

(2)74系列TTL IC的分类

1》以内部结构区分

- 标准型

- 结构跟构成的材料最简单,相对的特性也是不理想,所以此类型已经被淘汰多时。无英文简写,范例:7400。

- 早期的低功率型与高速型

- 低功率型,(英文 Low Power简写“L”),耗电低,但速度慢。范例:74L00。

- 高速型,(英文 High Speed简写“H”),速度较快,输出较强,但耗电高。范例:74H00。

- 由于 S 型耗电与 H 型相近,但速度极快。 LS 型的耗电与 L 型相近,但速度却快很多,甚至比 H 型还快。 因此 L 型与 H 型很快就退出市场。

- 肖特基(Schottky)

-

除了电阻器一样是做控流跟偏置用途,肖特基型最主要是采用

肖特基二极管跟

肖特基晶体管,改善切换速度。在市面上跟教育单位非常普及,特性也很不错,常常被用来搭配Intel 8051使用。LS型逐渐成为TTL中的主流。

- 肖特基型(英文 Schottky Logic,简写“S”),范例:74S00。

- 高级肖特基型(英文 Advanced Schottky Logic,简写“AS”),范例:74AS00。

- 低功率肖特基型(英文 Low Power Schottky Logic,简写“LS”),范例:74LS00。

- 高级低功率肖特基型(英文 Advanced Low Power Schottky Logic,简写“ALS”),范例:74ALS00。

- 快速(英文Fast,简写“F”)

- 快速型是有别于肖特基型所另外发展的高速TTL,范例:74 F00。

- CMOS(英语:Complementary Metal Oxide Semiconductor)

-

虽然此类型的编号与接脚规格跟TTL一样,但内部的实际结构是 CMOS,而不是TTL所使用的接面晶体管。此系列具有CMOS的高输入阻抗特性与低耗电,但工作电压范围有别于先前RCA所发展的40跟45系列的CMOS逻辑IC。除早期的C系列外,此类CMOS的运作速度非常快。

- CMOS,英文简写“C”,范例:74C00。

- 高级CMOS(英文 Advanced CMOS Logic,简写“AC”),范例:74AC00。

- 高速CMOS(英文 High Speed CMOS Logic,简写“HC”),范例:74HC00。

- 高级高速CMOS(英文 Advanced High Speed CMOS Logic,简写“AHC”),范例:74AHC00。

2》以输出型态分类

- 图腾式输出(Totem-pole Output)

- 大部分74系列的组合逻辑IC,都是采用图腾式输出。此种输出可以输出高电位与低电位。被称为图腾式则是因为电路形式像图腾一样配置。

- 开集电极式输出(Open Collector,简称O.C.)

此种输出不能输出高电位,输出只有开路与低电位两种状态。

- 可以承受较高的电压或与不同工作电压的电路连接。 有时开集电极式输出可用来应付比较重的负载(例继电器)。

- 可以允许多个开集电极式逻辑输出进行并联,作为Wired-AND使用。图腾式的逻辑门输出不能并联连接。

- 三态式输出(Tri-state或3-state)

- 在数字电路除了0跟1以外,另一种状态则是高阻抗,高阻抗对电路来说即是断路。主要是用于总线(bus)等。

- 史密特触发型输入(Schmitt Trigger)

- 此类型逻辑门具有所谓的迟滞电压,不易因为输入在0/1交界电压附近的小幅变化而产生输出跳动,主要用途是抗噪声、消除机械式接点的弹跳(暂态)现象,也可用来做RC振荡器等。

(3)代表性IC

- 与非门(NAND):7400、7410、7412、7420、7430

- 或非门(NOR):7402、7427

- 非门(NOT):7404、7414

- 与门(AND):7408、7411、7421

- 或门(OR):7432

- 异或门(XOR):7486

- 同或门(XNOR):74266

- 缓冲闸(Buffer):7407、74244

- BCD(十进制)转七段数码管解码器:7447、7448

- 全加器(Full Adders):7483、74283

- D型栓锁器(D-type Latches):74373

- 异步计数器(Asynchronous Counter):7490 (十进制,Decade)、7492(十六进制)

(4)注意事项

- 避免在带有静电的情况下接触IC

- TTL的电源电压要5V,建议最低不低于4.75V,最高不高于5.25V

- 若输入端空接,逻辑门会把输入端视为HI的状态

- 注意第一只脚的位置,以免错接

- 若某一逻辑门的输出要并接许多负载或是逻辑门,最好先装缓冲器或是提升电阻,以免发生负载效应

三、CMOS

参看:CMOS -- 维基百科

互补式金属氧化物半导体(简称互补式金氧半;英语:Complementary Metal-Oxide-Semiconductor,缩写:CMOS)乃是一种集成电路的设计工艺,可以在硅质晶圆模板上制出NMOS(n-type MOSFET)和PMOS(p-type MOSFET)的基本元件,由于NMOS与PMOS在物理特性上为互补性,因此被称为CMOS。此一般的工艺上,可用来制作电脑电器的静态随机存取内存、微控制器、微处理器与其他数字逻辑电路系统、以及除此之外比较特别的技术特性,使它可以用于光学仪器上,例如互补式金氧半图像传感装置在一些高级数码相机中变得很常见。

(1)CMOS电压

CMOS电路临界值(电源电压为+5V)

VOHmin = 4.99V VOLmax = 0.01V

VIHmin = 3.5V VILmax = 1.5V

(2)74 系列

- CMOS(英语:Complementary Metal Oxide Semiconductor)

-

虽然此类型的编号与接脚规格跟TTL一样,但内部的实际结构是 CMOS,而不是TTL所使用的接面晶体管。此系列具有CMOS的高输入阻抗特性与低耗电,但工作电压范围有别于先前RCA所发展的40跟45系列的CMOS逻辑IC。除早期的C系列外,此类CMOS的运作速度非常快。

- CMOS,英文简写“C”,范例:74C00。

- 高级CMOS(英文 Advanced CMOS Logic,简写“AC”),范例:74AC00。

- 高速CMOS(英文 High Speed CMOS Logic,简写“HC”),范例:74HC00。

- 高级高速CMOS(英文 Advanced High Speed CMOS Logic,简写“AHC”),范例:74AHC00。

(3)与TTL比较

参看:TTL电平、CMOS电平、RS232电平

1、电平的上限和下限定义不一样,CMOS具有更大的抗噪区域。 同是5v供电的话,TTL一般是1.7V和3.5V的样子,CMOS一般是2.2V,2.9V的样子,不准确,仅供参考。

2、电流驱动能力不一样,TTL一般提供25毫安的驱动能力,而CMOS一般在10毫安左右。

3、需要的电流输入大小也不一样,一般TTL需要2.5毫安左右,CMOS几乎不需要电流输入。

4、很多器件都是兼容TTL和CMOS的,datasheet会有说明。如果不考虑速度和性能,一般器件可以互换。但是需要注意有时候负载效应可能引起电路工作不正常,因为有些TTL电路需要下一级的输入阻抗作为负载才能正常工作。

5、TTL和CMOS的逻辑电平转换

CMOS电平能驱动TTL电平,TTL电平不能驱动CMOS电平,需加上拉电阻。

四、了解更多

参看:TTL和CMOS集成电路

集成电路(integrated circuit)是一种微型电子器件或部件。采用一定的工艺,把一个电路中所需的晶体管、二极管、电阻、电容和电感等元件及布线互连一起,制作在一小块或几小块半导体晶片或介质基片上,然后封装在一个管壳内,成为具有所需电路功能的微型结构;其中所有元件在结构上已组成一个整体,使电子元件向着微小型化、低功耗和高可靠性方面迈进了一大步。它在电路中用字母“IC”表示。集成电路发明者为杰克·基尔比(基于硅的集成电路)和罗伯特·诺伊思(基于锗的集成电路)。当今半导体工业大多数应用的是基于硅的集成电路。目前应用最广泛的数字电路是TTL电路和CMOS电路。

1、TTL电路

TTL电路以双极型晶体管为开关元件,所以又称双极型集成电路。双极型数字集成电路是利用电子和空穴两种不同极性的载流子进行电传导的器件。它具有速度高(开关速度快)、驱动能力强等优点,但其功耗较大,集成度相对较低。

根据应用领域的不同,它分为54系列和74系列,前者为军品,一般工业设备和消费类电子产品多用后者。74系列数字集成电路是国际上通用的标准电路。其品种分为六大类:74××(标准)、74S××(肖特基)、74LS××(低功耗肖特基)、74AS××(先进肖特基)、74ALS××(先进低功耗肖特基)、74F××(高速)、其逻辑功能完全相同。

2、 CMOS电路

MOS电路又称场效应集成电路,属于单极型数字集成电路。单极型数字集成电路中只利用一种极性的载流子(电子或空穴)进行电传导。它的主要优点是输入阻抗高、功耗低、抗干扰能力强且适合大规模集成。特别是其主导产品CMOS集成电路有着特殊的优点,如静态功耗几乎为零,输出逻辑电平可为VDD或VSS,上升和下降时间处于同数量级等,因而CMOS集成电路产品已成为集成电路的主流之一。其品种包括4000系列的CMOS电路以及74系列的高速CMOS电路。其中74系列的高速CMOS电路又分为三大类:HC为CMOS工作电平;HCT为TTL工作电平(它可与74LS系列互换使用);HCU适用于无缓冲级的CMOS电路。74系列高速CMOS电路的逻辑功能和引脚排列与相应的74LS系列的品种相同,工作速度也相当高,功耗大为降低。74系列可以说是我们平时接触的最多的芯片,74系列中分为很多种,而我们平时用得最多的应该是以下几种:74LS,74HC,74HCT这三种。

输入电平 输出电平

74LS TTL电平 TTL电平

74HC COMS电平 COMS电平

74HCT TTL电平 COMS电平

另外,随着推出BiCMOS集成电路,它综合了双极和MOS集成电路的优点,普通双极型门电路的长处正在逐渐消失,一些曾经占主导地位的TTL系列产品正在逐渐退出市场。CMOS门电路不断改进工艺,正朝着高速、低耗、大驱动能力、低电源电压的方向发展。BiCMOS集成电路的输入门电路采用CMOS工艺,其输出端采用双极型推拉式输出方式,既具有CMOS的优势,又具有双极型的长处,已成为集成门电路的新宠。

3、 CMOS集成电路的性能及特点

功耗低

CMOS集成电路采用场效应管,且都是互补结构,工作时两个串联的场效应管总是处于一个管导通另一个管截止的状态,电路静态功耗理论上为零。实际上,由于存在漏电流,CMOS电路尚有微量静态功耗。单个门电路的功耗典型值仅为20mW,动态功耗(在1MHz工作频率时)也仅为几mW。工作电压范围宽

CMOS集成电路供电简单,供电电源体积小,基本上不需稳压。国产CC4000系列的集成电路,可在3~18V电压下正常工作。逻辑摆幅大

CMOS集成电路的逻辑高电平"1"、逻辑低电平"0"分别接近于电源高电位VDD及电源低电位VSS。当VDD=15V,VSS=0V时,输出逻辑摆幅近似15V。因此,CMOS集成电路的电压利用系数在各类集成电路中指标是较高的。抗干扰能力强

CMOS集成电路的电压噪声容限的典型值为电源电压的45%,保证值为电源电压的30%。随着电源电压的增加,噪声容限电压的绝对值将成比例增加。对于VDD=15V的供电电压(当VSS=0V时),电路将有7V左右的噪声容限。输入阻抗高

CMOS集成电路的输入端一般都是由保护二极管和串联电阻构成的保护网络,故比一般场效应管的输入电阻稍小,但在正常工作电压范围内,这些保护二极管均处于反向偏置状态,直流输入阻抗取决于这些二极管的泄露电流,通常情况下,等效输入阻抗高达103~1011Ω,因此CMOS集成电路几乎不消耗驱动电路的功率。温度稳定性能好

由于CMOS集成电路的功耗很低,内部发热量少,而且,CMOS电路线路结构和电气参数都具有对称性,在温度环境发生变化时,某些参数能起到自动补偿作用,因而CMOS集成电路的温度特性非常好。一般陶瓷金属封装的电路,工作温度为-55 ~ +125℃;塑料封装的电路工作温度范围为-45 ~ +85℃。扇出能力强

扇出能力是用电路输出端所能带动的输入端数来表示的。由于CMOS集成电路的输入阻抗极高,因此电路的输出能力受输入电容的限制,但是,当CMOS集成电路用来驱动同类型,如不考虑速度,一般可以驱动50个以上的输入端。抗辐射能力强

CMOS集成电路中的基本器件是MOS晶体管,属于多数载流子导电器件。各种射线、辐射对其导电性能的影响都有限,因而特别适用于制作航天及核实验设备。可控性好

CMOS集成电路输出波形的上升和下降时间可以控制,其输出的上升和下降时间的典型值为电路传输延迟时间的125%~140%。接口方便

因为CMOS集成电路的输入阻抗高和输出摆幅大,所以易于被其他电路所驱动,也容易驱动其他类型的电路或器件。TTL—Transistor-Transistor Logic 三极管-三极管逻辑

MOS—Metal-Oxide Semiconductor 金属氧化物半导体晶体管

CMOS—Complementary Metal-Oxide Semiconductor 互补型金属氧化物半导体晶体管

Q:为什么BJT比CMOS速度要快?

A:很多人只知道BJT比CMOS快,但不知道为什么。主要是受迁移率的影响。以NPN管和NMOS为例,BJT中的迁移率是体迁移率,大约为1350cm2/vs。NMOS中是半导体表面迁移率,大约在400-600cm2/vs。所以BJT的跨导要高于MOS的,速度快于MOS。这也是NPN(NMOS)比PNP(PMOS)快的原因。

NPN比PNP快也是因为载流子迁移率不同,NPN中的基区少子是电子,迁移率大(1350左右);PNP的基区少子是空穴(480左右)。所以同样的结构和尺寸的管子,NPN比PNP快。所以在双极工艺中,是以作NPN管为主,PNP都是在兼容的基础上做出来的。MOS工艺都是以N阱PSUB工艺为主,这种工艺可做寄生的PNP管,要做NPN管就要是P阱NSUB工艺。

BJT是之所以叫bipolar,是因为基区中既存在空穴又存在电子,是两种载流子参与导电的;而MOS器件的反形层中只有一种载流子参与导电。但并不是因为两种载流子导电总的迁移率就大了。而且情况可能恰恰相反。因为载流子的迁移率是与温度和掺杂浓度有关的。半导体的掺杂浓度越高,迁移率越小。而在BJT中,少子的迁移率起主要作用。

NPN管比PNP管快的原因是NPN的基子少子是电子,PNP的是空穴,电子的迁移率比空穴大。NMOS比PMOS快也是这个原因。而NPN比NMOS快的原因是NPN是体器件,其载流子的迁移率是半导体内的迁移率;NMOS是表面器件,其载流子的迁移率是表面迁移率(因为反形层是在栅氧下的表面形成的)。而半导体的体迁移率大于表面迁移率。

![]()