数字逻辑实验篇_logisim模拟

这篇博客记录数字逻辑实验的实验过程,解析自己遇到的知识和细节。

包含器件:JK触发器、74LS00、74LS08、74LS90、74LS390、CD4511、十六进制计数器(无七段数码管)、六十进制计数器(七段数码管显示)

发现一个神仙网站,先推一下。右侧两个文件夹,第一个文件夹是guide,也就是教程,第二个文件夹reference是所有元件的介绍,简单易懂,就是纯英不太友好,建议和翻译器配合使用。

logisim教程网站

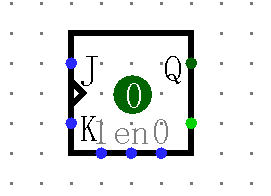

触发器

JK触发器

logisim上JK触发器有label,我们可以清楚的看到

JK触发器左侧三个连接端,J K连接端还有时钟端;

右侧两个连接端,Q 非Q 连接端;

下方三个连接端,置1端,使能控制端,置0端。

logisim上使能控制端默认为1,比较方便。

真值表:

| J | K | 输出Q |

|---|---|---|

| 0 | 0 | 不变 |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | 反转 |

记清楚真值表哦,后面要用的。

芯片

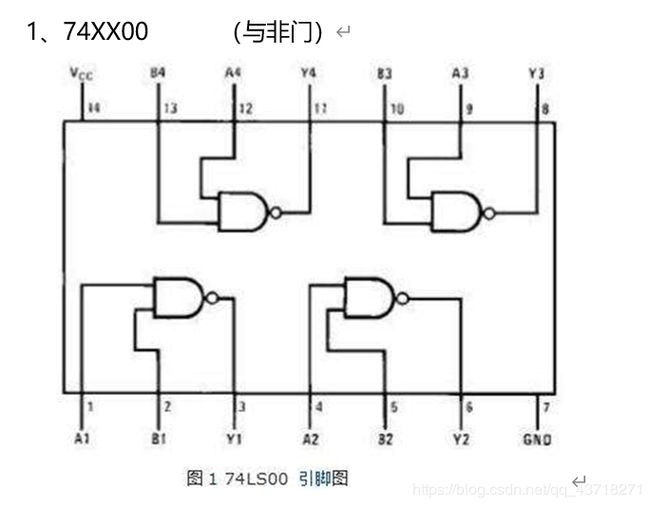

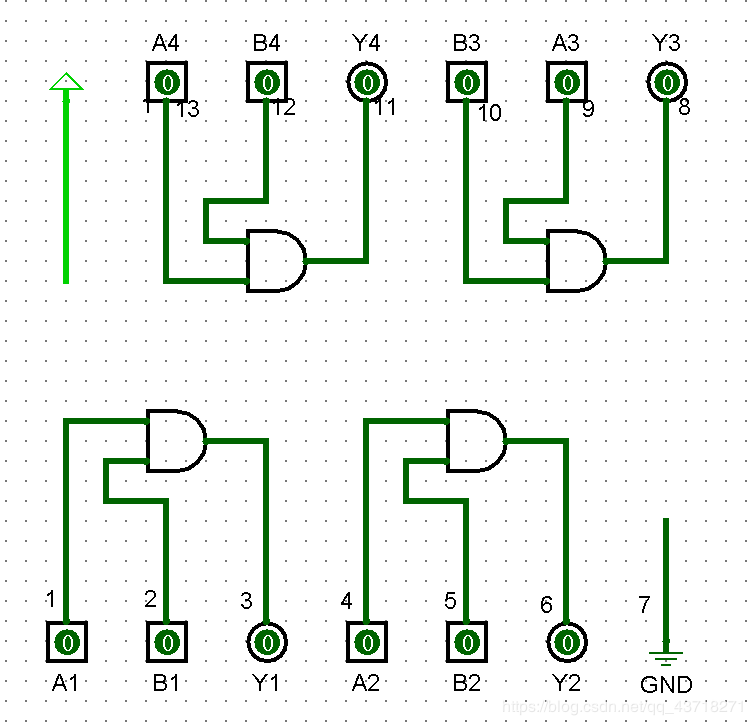

74LS00

简单来说就是四个与非门,电源和接地端暂时不需要制作。

引脚图

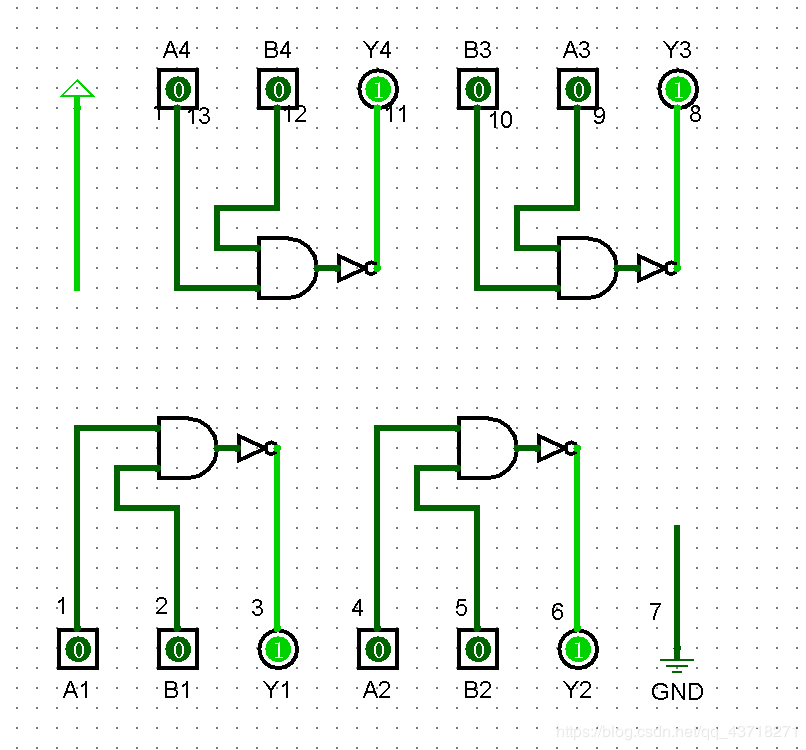

74LS08

74LS08和74LS00类似,简单来说就是四个与门

引脚图

原理图

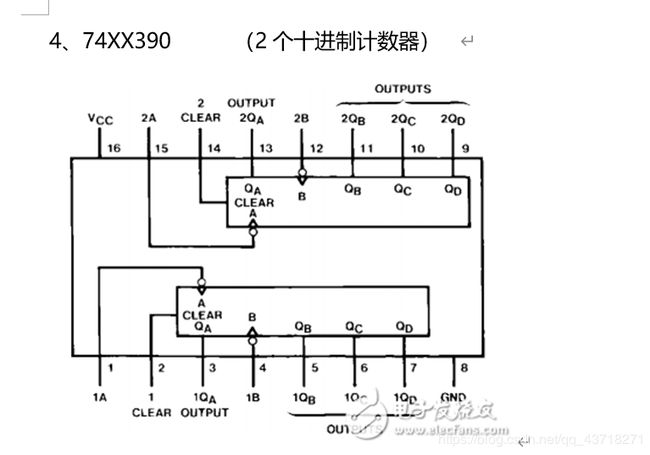

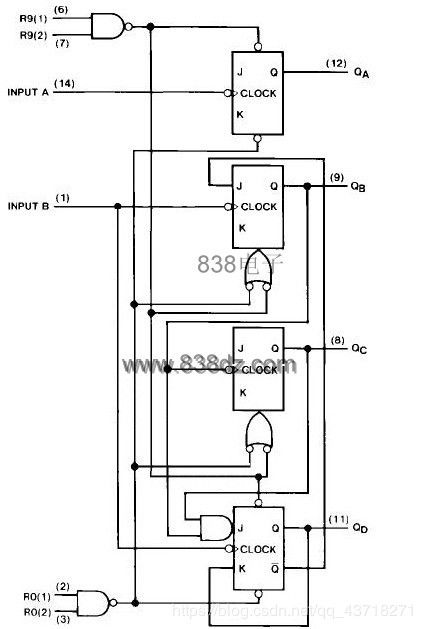

74LS90

从这里开始比较难,74LS90(分频器)在我们的实验中用作十进制计数器,其本质是用JK触发器构成的一个二进制计数器和一个五进制计数器,我们通过外部连接(没错,就是QA和INPUT B),可以把二进制计数器和五进制计数器连接在一起,构成一个十进制计数器,实际上也可以用作其他进制,资料可以自查。

引脚图

引脚图很复杂,但是别被吓到了,下面有解释,先看解释,然后对照着图一点点看,可以的,没那么难,理清结构就好。

首先从左右两部分看,左侧的长线基本都属于置0端或者置9端,忽略这些之后,我们会发现整个电路从上下还可以分成两个部分,从上到下四个JK触发器,第一个触发器为第一部分,后三个触发器为第二部分。我们不妨将其分别称为ABCD触发器。不难看出A触发器并没有直接与其他三个触发器有直接联系,它就是我们的二进制计数器,且其仅被INPUT A控制,也就是说,下方BCD三个触发器构成一个五进制触发器,且其仅由INPUT B控制。

五进制触发器必须表示0~4五个数字,也就是

000,001,010,011,100,

当数字到达101时,必须跳转回000,即清零;

(如果仅仅从这个角度出发,我们完全可以通过一个三输入的与门实现,后面我也的确这么做了。)

但我们的74LS90没有这么做,它选择了使用JK触发器之间的巧妙约束。

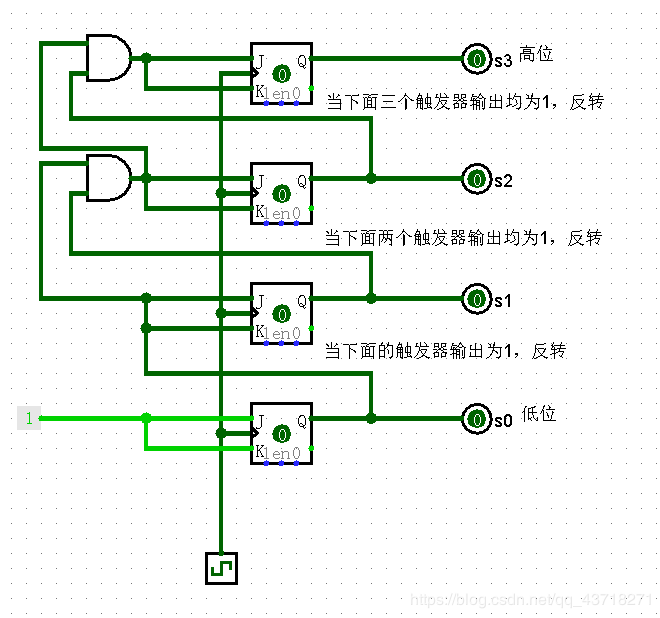

这里的理解要有理解JK触发器正常计数做法的基础。

五进制这里不同的是,在0~4这五个数字,触发器C的输出Q,当且仅当数字为4的时候为1,也就是如果我们把触发器D的输出Q连入触发器D的K,那么在数字0 ~ 3,由于Q恒为0,则K端恒为0,当且仅当数字为3时,J端为1,K端为0,JK触发器输出置1,得到数字4。

同时,触发器D的K端输入变成1,触发器D的J端为0,当我们再次点积脉冲,就会使得触发器D置零,Q非信号,即0,也会传入触发器B前面的与门,使得触发器B的J端为0,发生置0。至此,清零结束。

当然,这个过程我们也可以通过与门来实现,多连几根线就可以了。

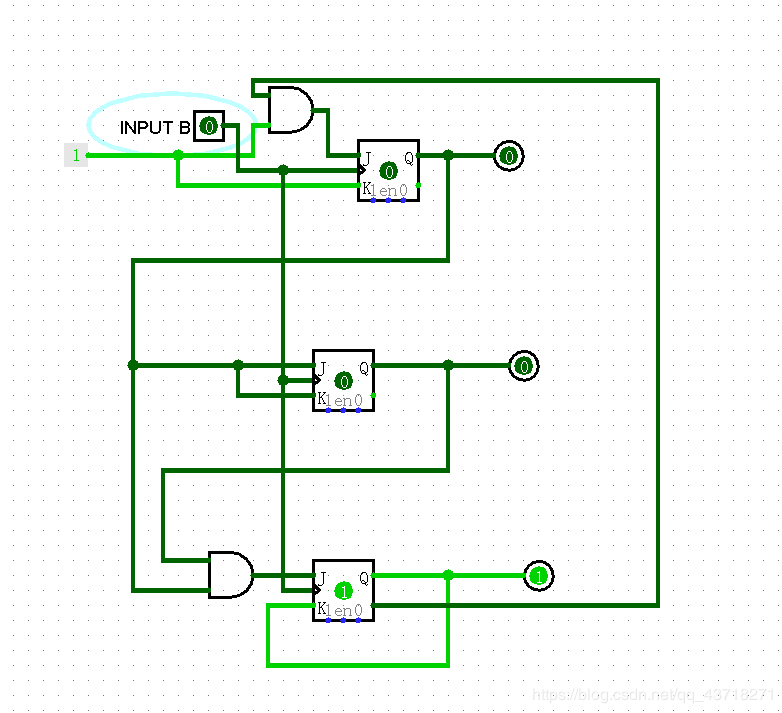

五进制计数器原理图(JK触发器版本)

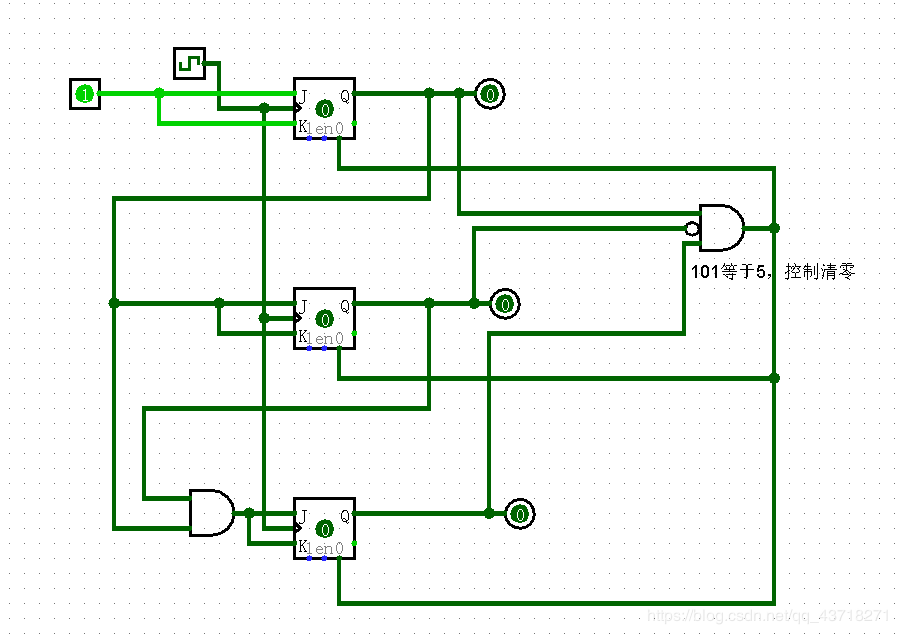

五进制计数器原理图(与门控制版本)

74LS90完整原理图

最后就是原理图中的R0和R9,分别表示把结果强制表示为0和9,很好理解。

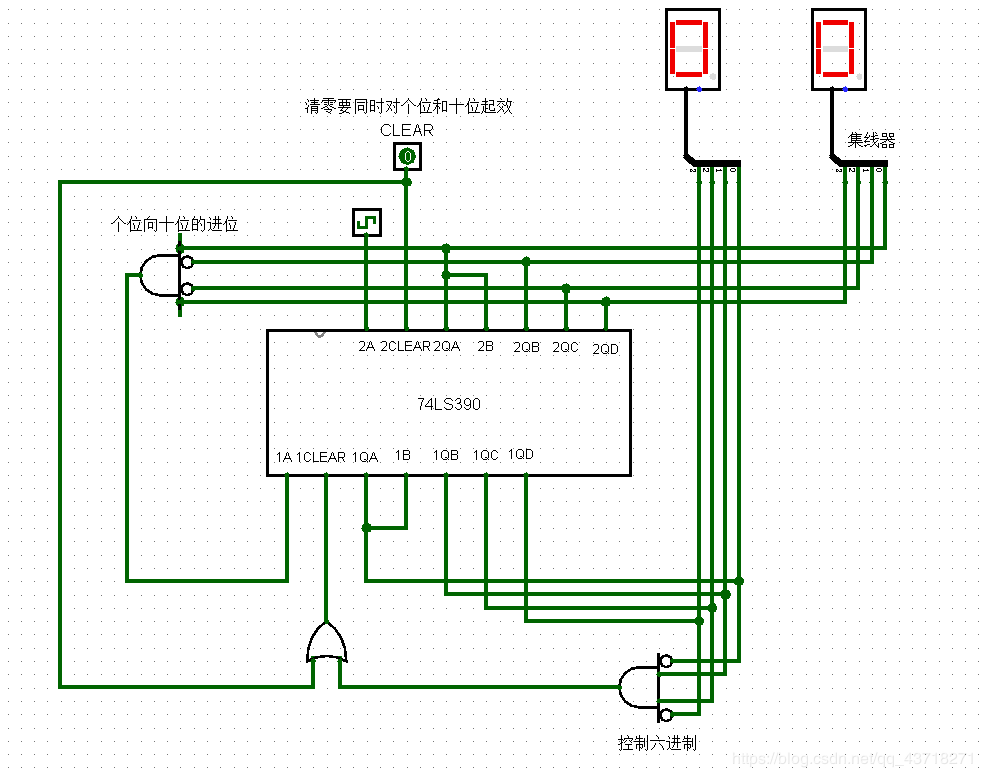

74LS390

组件

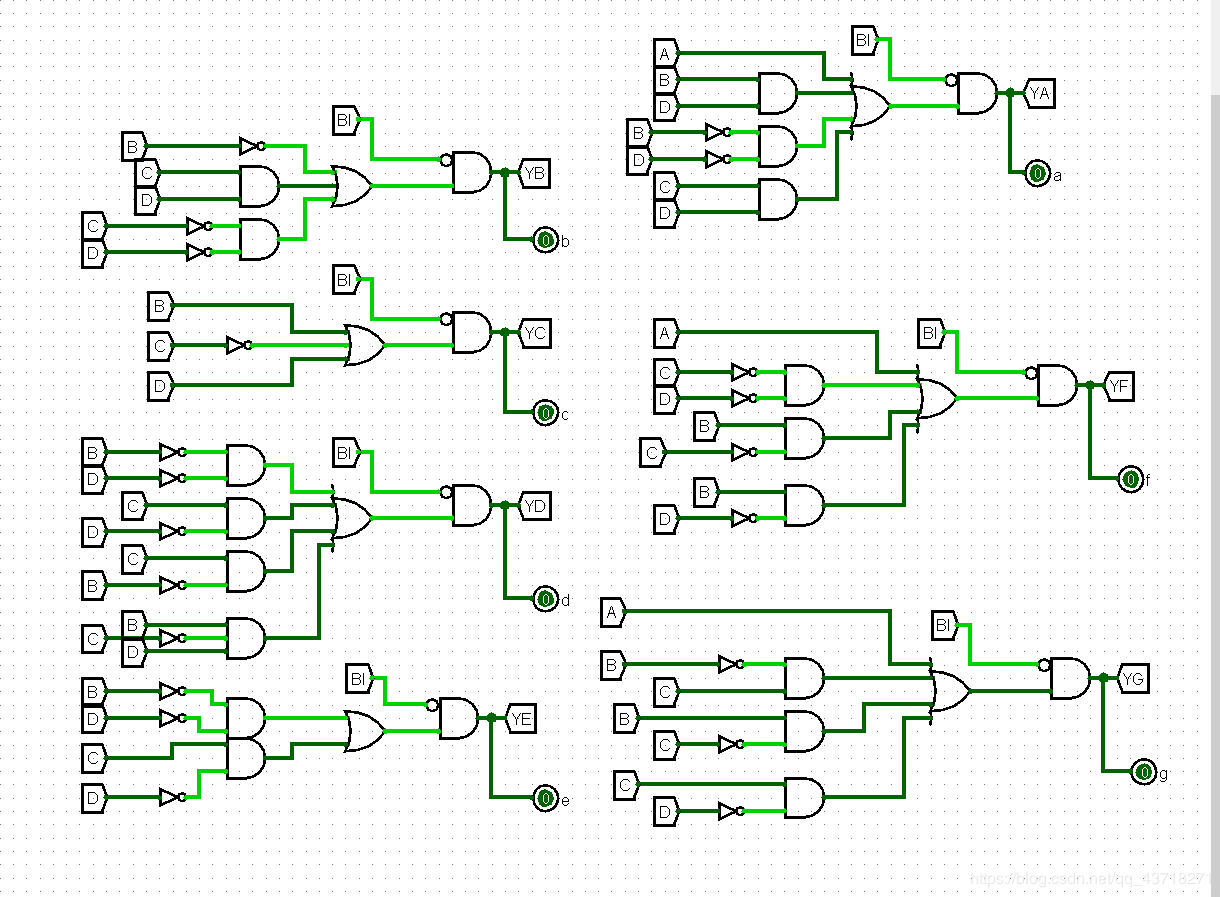

CD4511

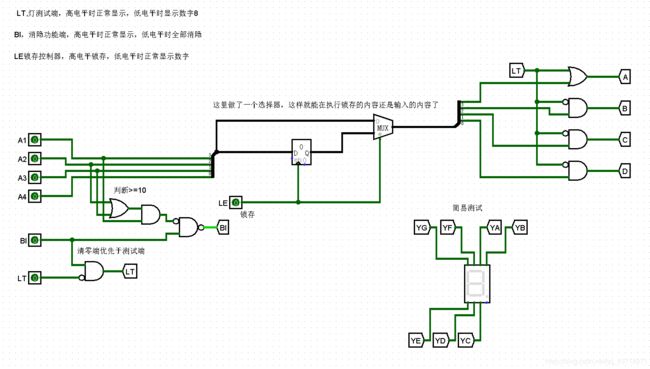

CD4511 是一片锁存/7 段译码/驱动器芯片,总计十四个端口,四个输入端A0··A3用来BCD码输入,七个输出端YA~YG,以及三个控制端LT,BI,LE。

LT为灯测试端,加高电平时,显示器正常显示,加低电平时,显示器一直显示数码“8”,以检查显示器是否有故障。

BI为消隐功能端,高电平时,显示器正常显示,低电平时使所有笔段均消隐。

LE是锁存控制端,高电平时锁存,外部输入无效,低电平时正常传输数据。

另外 CD4511有拒绝伪码的特点,当输入数据超过十进制数9(1001)时,显示字形也自行消隐。

然后是设计思路, CD4511我自己也确实做了很久,希望都能耐着性子慢慢来吧,其实控制输入应该是非常耗时间的一件事,列出真值表,化简,再设计,但是我们老师直接给出了现成的,十分友好,给老师点赞。

1 首先要完成的就是把BCD码输入转换成七段电子数码管的信号,这一点可以通过列七个电子数码管的某一段亮灭情况与BCD码输入的真值表得到当前段和输入的逻辑表达式实现,然后通过门电路组合完成转换。

2 为了配合灯测试端LT和消隐功能端BI的使用,我把LT和BI的信号也和转换的结果直接相连,方便控制,即七段数码管的某一段亮的条件除了数字本身的要求,再加上BI端和LT端的控制要求。

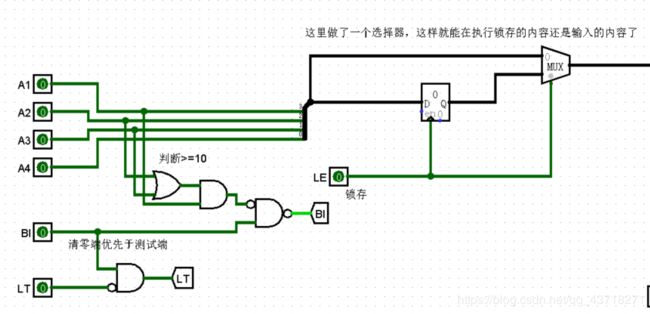

3 锁存控制端LE则依赖寄存器的使用,LE和寄存器的时钟端相连控制寄存器的使用,如果LE为高电平,使用寄存器存储信号,否则直接传输即可。

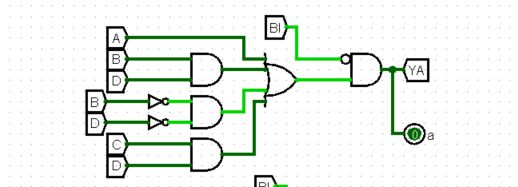

原理图(全图有点糊,最后部分放 左右分开高清版本)

左侧是主电路,右侧是将输入的BCD码分别转化为七段数码管的七个控制信号,分别控制七段数码管的a b c d e f g七个灯段亮灭状况。

右侧一大片都是BCD码的转换部分,取其中a段举例,

当输入的数字为十进制的0,2,3,5,7,8,9时,输出YA均必须为1,写成真值表可得:

| A | B | C | D | YA |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 |

上图恰好满足真值表中的数据要求,设计很费心思。具体方法就是真值表+卡诺图化简+列出真值表达式,十分繁琐,而且要做七次······

继续讲解输出部分,YA输出要受到消隐功能端BI和灯测试端LT的控制,所以YA正常输出时必须有BI端为0。LT端的控制则体现的更早,如果LT输入端为0且不消隐,直接把数字转换为数字8。

BCD码的数值十进制情况下大于10的时候,直接通过消隐功能完成消隐即可。锁存功能主要通过寄存器实现,即把锁存控制器LE端用作寄存器的时钟,如果锁存端从0变1,寄存器接收数字,同时选择器选择输出第二路信号,第一路信号不再输出,保证输出信号不再受输入影响,从而实现寄存功能。(用控制缓冲器也可实现,上图解释一下我是用了什么结构寄存的)

高清大图

十六进制计数器(无七段数码管)

不是很难理解,就直接上原理图了,4个JK触发器,好好看图,你可以的。