简单介绍I2C总线

转自 《I2C

总线协议应用指导书》 魏芬 编著

说的简单通俗,所以转载了。

第7章 I2C 总线简介

ZLG7290B与微控制器的接口形式是I2C串行总线,因此有必要简要地介绍一下I2C总线协议标准。第8章还给出了用C51编写的I2C总线软件包,以供参考学习。7.1 I2C总线概述

飞利浦(Philips)于20多年前发明了一种简单的双向二线制串行通信总线,这个总线被称为Inter-IC或者I2C总线。目前I2C总线已经成为业界嵌入式应用的标准解决方案,被广泛地应用在各式各样基于微控器的专业、消费与电信产品中,作为控制、诊断与电源管理总线。多个符合I2C总线标准的器件都可以通过同一条I2C总线进行通信,而不需要额外的地址译码器。由于I2C是一种两线式串行总线,因此简单的操作特性成为它快速崛起成为业界标准的关键因素。7.2 I2C总线的信号线

I2C总线只需要由两根信号线组成,一根是串行数据线SDA,另一根是串行时钟线 SCL。一般具有I2C总线的器件其SDA和SCL引脚都是漏极开路(或集电极开路)输出结构。因此实际使用时,SDA和SCL信号线都必须要加上拉电阻(Rp,Pull-Up Resistor)。上拉电阻一般取值3~10KΩ。开漏结构的好处是:当总线空闲时,这两条信号线都保持高电平,几乎不消耗电流;电气兼容性好,上拉电阻接5V电源就能与 5V 逻辑器件接口,上拉电阻接3V电源又能与 3V逻辑器件接口;因为是开漏结构,所以不同器件的SDA与SDA之间、SCL与 SCL之间可以直接相连,不需要额外的转换电路。

图7.1 I2C总线信号连接示意图

7.3 I2C总线基本概念

(1) 发送器(Transmitter):发送数据到总线的器件;(2) 接收器(Receiver):从总线接收数据的器件;

(3) 主机(Mater):初始化发送、产生时钟信号和终止发送的器件;

(4) 从机(Slave):被主机寻址的器件。

I2C 总线是双向传输的总线,因此主机和从机都可能成为发送器和接收器。如果主机向从机发送数据,则主机是发送器,而从机是接收器;如果主机从从机读取数据,则主机是接收器,而从机是发送器。

7.4 I2C总线数据传送速率

I2C总线的通信速率受主机控制,能快能慢。但是最高速率是有限制的,I2C总线上数据的传输速率在标准模式(Standard-mode)下最快可达100Kb/s。7.5 I2C总线上数据的有效性(Data validity)

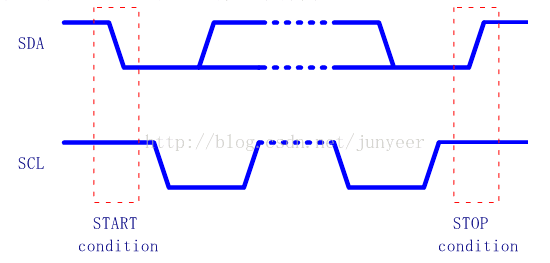

数据线SDA的电平状态必须在时钟线SCL处于高电平期间保持稳定不变。SDA 的电平状态只有在SCL处于低电平期间才允许改变。但是在I2C总线的起始和结束时例外。某些其它的串行总线协议可能规定数据在时钟信号的边沿(上升沿或下降沿)有效,而I2C总线则是电平有效。

图7.2 I2C总线上数据有效性的示意图

7.6 起始条件和停止条件(START and STOP conditions)

起始条件:当SCL处于高电平期间时,SDA从高电平向低电平跳变时产生起始条件。 总线在起始条件产生后便处于忙的状态。起始条件常常简记为S。停止条件:当SCL处于高电平期间时,SDA从低电平向高电平跳变时产生停止条件。总线在停止条件产生后处于空闲状态。停止条件简记为 P。

图7.3 I2C起始条件和停止条件示意图

7.7 从机地址(Slave Address)

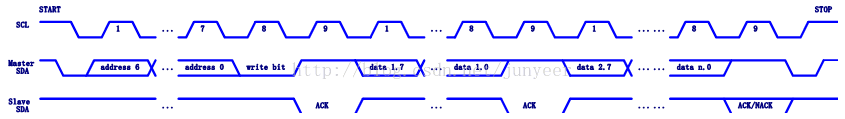

I2C总线不需要额外的地址译码器和片选信号。多个具有I2C总线接口的器件都可以连接到同一条I2C总线上,它们之间通过器件地址来区分。主机是主控器件,它不需要器件地址,其它器件都属于从机,要有器件地址。必须保证同一条I2C总线上所有从机的地址都是唯一确定的,不能有重复,否则I2C总线将不能正常工作。一般从机地址由7位地址位和一位读写标志(R/W)组成,7位地址占据高7位,读写位在最后。读写位是0,表示主机将要向从机写入数据;读写位是1,则表示主机将要从从机读取数据。7.8 数据传输的基本格式

I2C总线以字节为单位收发数据。传输到SDA线上的每个字节必须为8位。每次传输的字节数量不受限制。首先传输的是数据的最高位(MSB,第7位),最后传输的是最低位(LSB,第0位)。另外,每个字节之后还要跟一个响应位,称为应答。7.9 应答(Acknowledge)

在I2C总线传输数据过程中,每传输一个字节,都要跟一个应答状态位。接收器接收数据的情况可以通过应答位来告知发送器。应答位的时钟脉冲仍由主机产生,而应答位的数据状态则遵循“谁接收谁产生”的原则,即总是由接收器产生应答位。主机向从机发送数据时,应答位由从机产生;主机从从机接收数据时,应答位由主机产生。I2C总线标准规定:应答位为0表示接收器应答(ACK),常常简记为A;为1则表示非应答(NACK),常常简记为A。发送器发送完LSB之后,应当释放SDA线(拉高 SDA,输出晶体管截止),以等待接收器产生应答位。如果接收器在接收完最后一个字节的数据,或者不能再接收更多的数据时,应当产生非应答来通知发送器。发送器如果发现接收器产生了非应答状态,则应当终止发送。7.10 基本的数据传输格式示意图

图7.4 主机向从机发送数据的基本格式

图7.5 主机从从机接收数据的基本格式

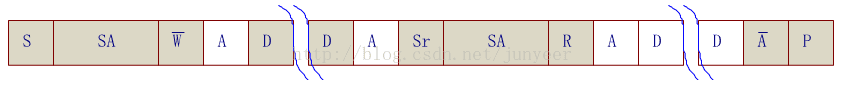

在图 7.4 和图 7.5 中,各种符号的意义为:

S:起始位(START);

SA:从机地址(Slave Address),7位从机地址;

W:写标志位(Write),1位写标志;

R:读标志位(Read),1位读标志;

A:应答位(Acknowlege),1位应答;

A:非应答位(Not Acknowledge) ,1位非应答;

D:数据(Data),每个数据都必须是8位;

P:停止位(STOP);

阴影:主机产生的信号;

无阴影:从机产生的信号。

应当注意的是,与图7.5中的情况不同的是,在图7.4 中,主机向从机发送最后一个字节的数据时,从机可能应答也可能非应答,但不管怎样主机都可以产生停止条件。如果主机在向从机发送数据(甚至包括从机地址在内)时检测到从机非应答,则应当及时停止传输。

7.11 传输一个字节数据的时序图

为了更清楚地了解I2C 总线的基本数据传输过程,下面画出了只传输1个字节的时序图,这是最基本的传输方式。在图7.6和图7.7中,SDA信号线被画成了两个,一个是主机产生的,另一个是从机产生的。实际上主机和从机的SDA信号线总是连接在一起的,是同一根SDA。画成两个SDA有助于进一步理解在I2C总线上主机和从机的不同行为。图7.6 主机向从机发送1字节数据的时序图

图7.7 主机从从机接收1字节数据的时序图

7.12 传输多个字节数据的时序图

主机连续向从机发送或从从机接收多个字节数据的情况也很容易理解,下面直接给出相关时序图。

图7.8 主机向从机连续发送多个字节数据的时序图

图7.9 主机从从机连续接收多个字节数据的时序图

7.13 重复起始条件(Repeated START condition)

主机与从机进行通信时,有时需要切换数据的收发方向,例如访问某一具有I2C 总线接口的E2PROM存储器时,主机先向存储器输入存储单元的地址信息(发送数据),然后再读取其中的存储内容(接收数据)。在切换数据的传输方向时,可以不必先产生停止条件再开始下次传输,而是直接再一次产生开始条件。I2C总线在已经处于忙的状态下,再一次直接产生起始条件的情况被称为重复起始条件。重复起始条件常常简记为Sr。正常的起始条件和重复起始条件在物理波形上并没有什么不同,区别仅仅是在逻辑方面。在进行多字节数据传输过程中,只要数据的收发方向发生了切换,就要用到重复起始条件。图7.10 带有重复起始条件的多字节数据传输格式示意图

图 7.10 给出了带有重复起始条件的多字节数据传输格式示意图,图中的各种符号的意义与第 7.10 节中的相同。要特别注意图中重复起始条件Sr的用法。如果读者有兴趣的话,可以自行画出其对应的时序图。

7.14 无子地址器件与有子地址器件

带有I2C总线的器件除了有从机地址 (Slave Address)外,还可能有子地址(Sub-Address)。 从机地址是指该器件在I2C总线上被主机寻址的地址,而子地址是指该器件内部不同部件或存储单元的编址。例如,带I2C总线接口的 E2PROM就是拥有子地址器件的典型代表。另外一些器件(只占少数)内部结构比较简单,可能没有子地址,只有必须的从机地址。与从机地址一样,子地址实际上也是像普通数据那样进行传输的,传输格式仍然是与数据相统一的,区分传输的到底是地址还是数据要靠收发双方具体的逻辑约定。子地址的长度必须由整数个字节组成,可能是单字节(8位子地址),也可能是双字节(16位子地址),还可能是3字节以上,这要看具体器件的规定。在第8章的I2C总线软件包中,已经同时考虑到了无子地址器件和有子地址器件的情况。