IIC总线协议基础1

|

|

文档类别 |

| 文档标识 |

IIC总线协议基础1 |

| 当前版本 |

V0.2 |

| 作 者 |

Louis |

| 完成时间 |

2015-05-27 |

IIC总线协议基础1

IIC总线协议基础1. 1

1. IIC时序基础知识... 2

1.1 信号线... 2

1.2 开始和结束条件... 2

1.3 数据保持时间... 2

1.4 应答ACK和非应答NACK. 3

1.4.1 应答 ACK. 3

1.4.2 非应答 NO ACK. 4

1.4.3 注意事项... 4

1.5 重复开始【Repeat start】... 5

1.6 写入周期【write cycle】... 5

1.7 数据传送完整周期... 6

2. IIC设备... 6

2.1 设备操作... 6

2.1.1 时钟和数据发送... 6

2.1.2 开始条件... 7

2.1.3 结束条件... 7

2.1.4 应答(ACK)... 7

2.1.5 待机模式... 8

2.1.6 软件复位IIC. 8

2.2 设备地址... 8

2.3 写操作... 9

2.3.1 写Byte字节... 9

2.3.2 写PAGE页... 9

2.3.3 轮询应答(ACK POLLING)... 10

2.4 读操作... 10

2.4.1 当前地址读... 10

2.4.2 随机地址读... 11

2.4.3 连续地址读... 11

3. 参考文献... 12

1.IIC时序基础知识

1.1 信号线

SDA:双向数据线引脚,用来传输串行数据。引脚一般为开漏结构,可以和其他的开漏极或开集电极进行“线与”。【不同手册上看到有“线或”的说法,应该不对】

SCL:时钟输入引脚。【有些资料说是在SCL的上升沿才能将数据写入AT24C02中,在SCL的下降沿才能从 AT24C02 中读出数据,这是不正确的。实际测试:在SCL的下降沿后再从SDA总线上去读取数据,数据有误。】

1.2 开始和结束条件

开始时序:在SCL高电平时SDA出现一个下降沿;

结束时序:在SCL高电平时SDA出现一个上升沿;

1.3 数据保持时间

数据SDL变化必须在SCL低电平的时候变化。并且在SCL高电平时保持不变,否则会被误认为是命令(开始/结束)条件。

1.4 应答ACK和非应答NACK

SCL一直由Master控制,SDA依照数据传送的方向,读数据时由Slave控制SDA,写数据时由Master控制SDA。当8位数据传送完毕之后,应答位ACK或者非应答位NACK的SDA控制权与数据位传送时相反。

写数据的时候,Master每发送完8个数据位,Slave设备如果还有空间接受下一个字节应该回答“ACK”,Slave设备如果没有空间接受更多的字节应该回答“NACK”,Master当收到“NACK”或者一定时间之后没收到任何数据将视为超时,此时Master放弃数据传送,发送“Stop”。

读数据的时候,Slave设备每发送完8个数据位,如果Master希望继续读下一个字节,Master应该回答“ACK”以提示Slave准备下一个数据,如果Master不希望读取更多字节,Master应该回答“NACK”以提示Slave设备准备接收Stop信号。

MASTER 指主控制端,在一般系统中就是我们常说的单片机了;

SLAVE是指具备I2C协议的专用IC,比如24C16、14C32等。

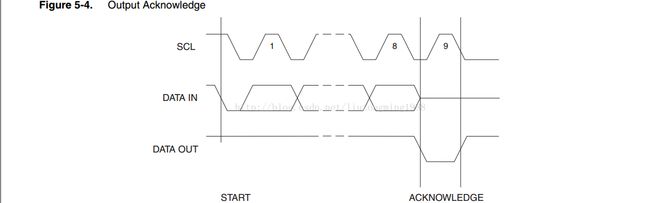

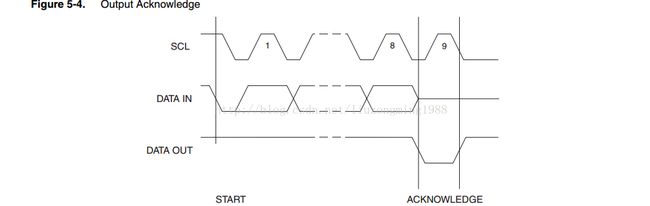

1.4.1应答 ACK

在数据发送器发送完8个位数据后,就会把SDA释放(拉高,因为IIC外部上拉)。设备在接收完毕8个位后,在第9个时钟SCL,设备将SDA拉低,产生应答ACK,来告诉数据发送器收到数据了。当发送器检测到SDA被拉低,就知道设备接收器接收完毕数据了。

1.4.2非应答 NO ACK

非应答(NACK)一般发生在主机读取数据时,当主机要结束读取数据时,就会发出非应答NACK。

如果slave方是硬件i2c要求一定要标准的NACK,master方是GPIO软件模拟i2c若没有正确的发送NACK,就会出现“slave收不到stop”导致i2c挂死。

1.4.3注意事项

MASTER向SLAVE发送数据

MASTER每次向SLAVE端发送8位数据后,就会将SDA置1,等待SLAVE端的确认;SLAVE端如果正确接受到数据,就会自动将SDA置0。程序能做的只是检测确认信号,即每发送完8位数据后就检测一次SDA的状态,如果是0,则让程序继续往下执行,如果是1则强迫MASTER将刚才的8位数据再发送一遍;当然,如果SDA一直是1,也就是SLAVE一直未能正确接受到数据,也不能一直让MASTER反复发送,要做TIMEOUT处理,以防系统死机。

MASTER从SLAVE读取数据:

MASTER从SLAVE端读取数据,情况与发送数据有所区别,在读到最后8位数据时,要将SDA置1,也就是做NACK动作,让系统知道读取数据到此结束;这个置1动作由程序来做,因为数据读到哪里结束,只有程序员知道。

IIC数据传输方式

NOTE:IIC是MSB FIRST传送的

1.5 重复开始【Repeat start】

即在发送完一个字节后(开始+8数据+ACK),没有发送STOP的情况下,继续下一次START(就是指repeatstart)。这个需要注意的是在第9个时钟之后和REPEAT START之间SDA要有一定的延时Tbuf(一般有个最小值)。

1.6 写入周期【write cycle】

内部写入周期器件,STOP和下一次的START之间需要有个延时Twr,保证设备写好数据。一般手册给出一个Twr最大值。

注意:英文资料里要求24c02内部写数据最大时间为10ms,也就是说在软件设计时,应该把2次写记忆时间间隔控制在大于Twr时间即间隔大于10ms,这样就不会有问题了,不同的芯片Twr时间相差很大,一般以参考手册为准。

1.7 数据传送完整周期

NOTE:IIC是MSB FIRST传送的

2.IIC设备

(以AT24C02器件为对象来介绍)

2.1 设备操作

2.1.1时钟和数据发送

SDA引脚通常由外部设备上拉。SDA上的数据只有在SCL是low的时候才可以变化。如果SDA上的数据在SCL的high期间内变化,那么将会被认为是开始/结束条件。

2.1.2开始条件

在SCL的high期间,SDA从high-到-low变化,就会触发一个开始条件。这个条件必须在其他任何指令开始之前发出的。

2.1.3结束条件

在SCL的high期间,SDA从low-到-high变化,就会触发一个结束条件。在读时序之后,收到一个停止条件,将会使EEPROM进入待机模式。

2.1.4应答(ACK)

所有的数据和地址信息都是通过8-bit的形式进行来回传输的。EEPROM将发送一个0来应答,表示它已经接收到每个字节了。这个时刻发生在第9个SCL。

2.1.5待机模式

AT24C02有待机模式的特性,如下形式将进入待机模式:

(1) 上电后;

(2) 接收到STOP,或者完成了内部所有操作后;

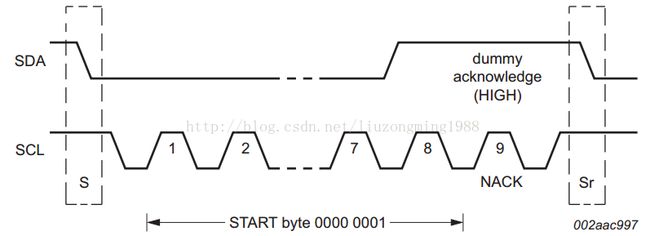

2.1.6 软件复位IIC

在协议中断,掉电或者系统复位后,可以通过如下步骤进行复位:

(1) 发送一个START条件;

(2) 发送9个时钟;

(3) 再发送一个START条件,并紧跟着一个STOP条件。

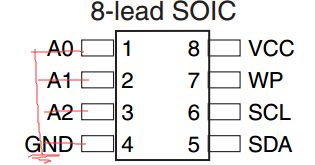

2.2 设备地址

2K EEPROM设备需要在一个START条件后面,跟上一个8-bit的设备地址使能芯片读、写功能。

设备地址的高4位由固定的1和0组成。通常在EEPROM设备中的高四位地址都是一样的。【不知道为什么???】

紧接着3位是2K EEPROM的A2、A1、A0设备地址位,这三位是用来区分EEPROM设备的,需要和硬件地址相等。

最后,第8位是设备地址的READ/WRITE读/写位。此位置1表示读操作,此为置0为写操作。

当设备地址对比之后,EEPROM将会反馈输出一个0.假如比较结果不对,那么芯片(EEPROM)将进入待机状态。

| 1010 111 R/W |

1010 000 R/W |

2.3 写操作

AT24C02设备地址的高4位由固定的1和0组成。接着3位是EEPROM的设备地址位A2、A1、A0。第8位是设备地址的READ/WRITE读/写位。此位置1表示读操作,此为置0为写操作。

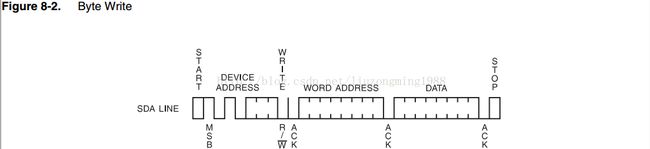

2.3.1写Byte字节

写操作需要发送设备地址,并跟随一个8-bit位数据地址和ACK。在接收到地址后,EEPROM将再次响应输出0,然后进入第一个8-bit数据的时钟。接收到8-bit数据后,EEPROM将输出一个0,寻址设备(主设备)必须发送一个STOP条件结束写操作。这样EEPROM就进入内部写入阶段(internally timed write cycle .[twr]),避免外部对memory进行操作。在这个阶段,所有输入无效,并且EEPROM不会有任何响应,直到内部写完毕。

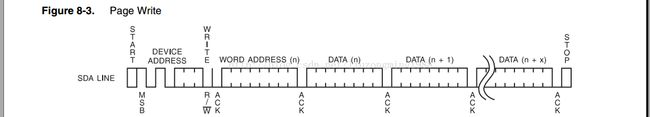

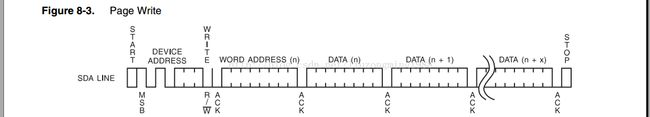

2.3.2写PAGE页

这个2K的EEPROM能够进行8-byte页写入。

Page写入和byte写入的初始化是一样的,只是控制器在发送完第一个数据后,不发送STOP条件。而是在第一个数据的ACK后,连续在发送后面的7个数据字节。EEPROM将在接收到每个数据字节后,均会产生一个ACK来响应(控制器)。发送完8个字节后,控制器必须发送一个STOP条件来结束PAGE写入。

数据地址的低3位bit在接收到每个数据后,都会自动增加。数据地址的高5位bit数据不增加,保持在当前页【row location】。

如果写入数据的地址,自动增加达到了PAGE边缘,那么接下去的字节将会从本页从头开始覆盖存储(“roll over”)。就是所如果在写入页的数据大于8byte(8-byte容量的page),那么多于的数据将会从本页从头写入,并覆盖掉先前的数据。所以在写入数据大于PAGE容量时,在写完一个PAGE,就需要STOP,然后重新开始,并写入下一页的地址,在开始写入数据。

2.3.3轮询应答(ACKPOLLING)

一旦进入内部写周期,将开启轮询应答,外部对EEPROM的输入将失效。此时如果发送一个START条件,和设备地址给EEPROM,只有当内部写周期完成后,EEPROM设备才会产生应答ACK。

2.4 读操作

有三种读操作:读取当前地址数据,随机地址读取,连续地址读取。

2.4.1当前地址读

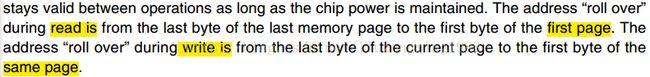

只要芯片电源没有掉电,在进行上一次A地址的读写操作之后,(A+1)地址就会一直有效。在读取数据中出现的“roll over”,指的是从最后一页的最后一个字节,跳到第一页的第一个字节。【和写时候出现的“roll over”是不一样的】

一旦在发送设备地址时,write/read位被设为1,并得到EEPROM应答ACK,那么当前地址(就是前文中的【A+1】地址)的数据就会被输出。控制器接收到数据后,不产生应答ACK【即产生非应答(NACK)】,而是在后面产生一个STOP条件。

【非应答:当控制器想结束访问数据后,就将SDA拉高,结束读取数据。但记得在NACK后要跟随一个STOP】。

2.4.2随机地址读

随机读取数据,需要一个“dummy”操作,即:发送设备地址+写操作(得到EEPROM应答ACK),并跟随发送需要访问数据的地址。当这个动得到EEPROM的应答ACK,控制器必须再次产生一个START条件,接着发送设备地址+读操作,在得到EEPROM应答ACK后,EEPROM接着就会发送出控制器要访问数据的地址。控制器接收到数据后,不产生应答ACK【即产生非应答(NACK)】,而是在后面产生一个STOP条件。

可以看出“随机地址读”比“当前地址读”多了一个“伪写入”动作:

2.4.3 连续地址读

连续读取初始化,可以通过“当前地址读取”或者“随机地址读取”操作来启动。只是在控制器接收到以第一字节后,控制器需要产生一个应答ACK给EEPROM。EEPROM一旦收到ACK,EEPROM就会继续将数据地址+1,发送数据。

当EEPROM的memory地址到达极限后,数据地址将会“roll over”,同时会继续读取数据。当控制器要终止连续读操作,控制器不产生应答ACK【即产生非应答(NACK)】,而是在后面产生一个STOP条件。

注意:

当控制器要终止连续读操作,直接给停止信号也是可以结束此次读操作,但是会对后面的操作带来影响。非应答信号在需要的时候必须给。

3.参考文献

[1] Atmel AT24C02B datasheet

[2] NXP Semiconductors UM10204 datasheet

[3] http://blog.csdn.net/bmbm546/article/details/8833956

[4] http://blog.csdn.net/skyflying2012/article/details/8237881

[5] http://www.52rd.com/bbs/Archive_Thread.asp?SID=196579&TID=3

[6]http://blog.sina.com.cn/s/blog_5f103c9c0100ly0r.html