STM32F429 >> 22. FMC_扩展外部SDRAM(Code)

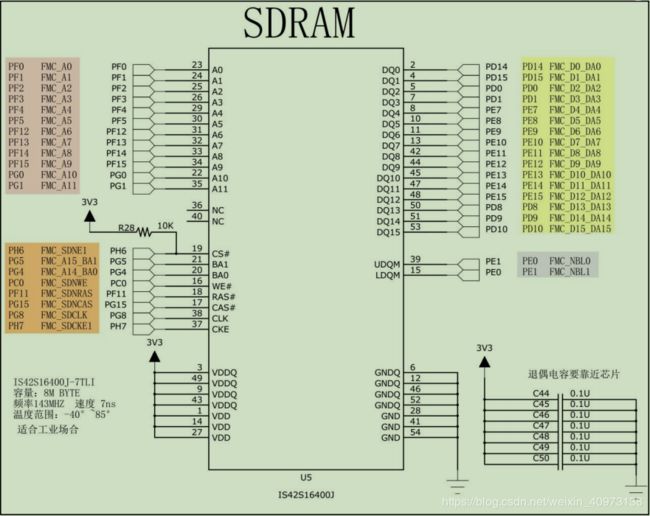

本代码用型号为“IS42S16400J”的 SDRAM 芯片为 STM32 扩展内存。

它的行地址宽度为 12 位,列地址宽度为 8 位,内部含有 4 个 Bank,数据线宽度为 16 位,容量大小为8MB。

SDRAM 硬件连接图:

SDRAM 与 STM32 相连的引脚非常多,主要是地址线和数据线。

bsp_sdram.h

/**

******************************************************************************

* @file bsp_sdram.c

* @author Waao

* @version V1.0.0

* @date 24-Feb-2019

* @brief This file contains some board support package's functions for the configuration of the SysTick.

*

******************************************************************************

* @attention

*

* None

*

******************************************************************************

*/

#ifndef __BSP_SDRAM_H_

#define __BSP_SDRAM_H_

#include bsp_sdram.c

/**

******************************************************************************

* @file bsp_sdram.c

* @author Waao

* @version V1.0.0

* @date 24-Feb-2019

* @brief This file contains some board support package's functions for the FMC-SDRAM

*

******************************************************************************

* @attention

*

* None

*

******************************************************************************

*/

#include main.c

/**

******************************************************************************

* @file main.c

* @author Waao

* @version V1.0.0

* @date 24-Feb-2019

* @brief MAIN.

* On this project, you can configure the SDRAM through the FMC peripheral

* and check if it works properly

*

******************************************************************************

* @attention

*

* None

*

******************************************************************************

*/

#include