stm32学习笔记 -根据外接存储器时序初始化FSMC结构体

文章目录

- 一. FSMC结构体

- FSMC_NORSRAMTimingInitTypeDef 结构体

- FSMC_NORSRAMInitTypeDef 结构体

- 二. 根据SRAM时序配置结构体

- i. 根据SRAM时序配置FSMC写时序结构体

- ii. 根据SRAM时序配置FSMC读时序结构体

- iii. FSMC总初始化结构体

- 根据SRAM时序配置配置SRAM总结

- 三. 根据ILI9341时序配置结构体

- i. 根据ILI9341时序配置FSMC写时序结构体

- ii. 根据ILI9341时序配置FSMC读时序结构体

- iii. FSMC总初始化结构体

一. FSMC结构体

控制FSMC使用SRAM存储器时主要是配置时序寄存器以及控制寄存

器,利用ST标准库的SRAM时序结构体以及初始化结构体可以很方便地写入参

数。

时序结构体: FSMC_ NORSRAMTimingInitTypeDef

初始化结构体: FSMC NORSRAMInitTypeDef

与其他的初始化相似,是由对应的XXX_Init()函数就可以初始化了。

FSMC_NORSRAMTimingInitTypeDef 结构体

这个FSMC_NORSRAMTimingInitTypeDef 时序结构体配置的延时参数,将作为下一节的FSMC SRAM初始化结构体的一个成员。

typedef struct

{

uint32_t FSMC_AddressSetupTimz; /*地址建立时间,0-0xF 个HCLK周期*/

uint32_t FSMC_AddressHoldTime; /*地址保持时间,0-0xF 个HCLK周期*/

uint32_t FSMC_DataSetupTime ; /*地址建立时间,0-0xF 个HCLK周期*/

uint32_t FSMC_BusTurnAroundDuration; /* 总线转换周期,0-0xF个HCLK周期,在NOR FLASH */

uint32_t FSMC_CLKDivision; /*时钟分频因子, 1-0xE,若控制异步存储器,本参数无效*/

uint32_t FSMC_DataLatency; /*数据延迟时间,若控制异步存储器,本参数无效*/

uint32_t FSMC_AccessMode; /*设置访问模式 */

} FSMC_NORSRAMTimingInitTypeDef;

- FSMC_AddressSetupTime

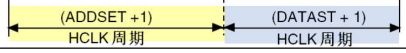

本成员设置地址建立时间,它可以被设置为0~0xF个 THCLK,按STM32标准库的默认配置,HCL K的时钟频率为72MHz,即一个 THCLK 为 1/72us=0.0138us=13.8us。

FSMC_AddressSetupTime用来设置ADDSET周期,用来控制写使能NWE信号高电平的时间。

- FSMC_AddressHoldTime(用于NorFLASH,SRAM无用,跳)

本成员设置地址保持时间,它可以被设置为0-0xF个HCLK周期数。在模式D或复用模式中拥有,用于NORFLASH。

看时序图,其作用式延迟写使能NWE信号为高电平的时间。

- FSMC_DataSetupTime

本成员设置数据建立时间,它可以被设置为0-0xF个HCLK周期数。

FSMC_DataSetupTime用来设置DATAST周期,用来控制写使能NWE信号变为低电平的时间。

- FSMC_Bus TurnAroundDuration(用于NorFLASH,SRAM无用,跳)

本成员设置总线转换周期,在操作NOR FL ASH存储器的复用读操作中,地址线数据线公用一线,地址线与数据线可以分时复用,总线转换周期就是指总线在这两种状态间切换需要的延时,防止冲突。控制其它存储器时这个参数无效,配置为0即可。

- FSMC_CLKDivision

本成员用于设置时钟分频,它以HCLK时钟作为输入,经过FSMC_CLKDivision分频后输出到FSMC_CLK引 脚作为通讯使用的同步时钟。

控制其它异步通讯的存储器时这个参数无效,配置为0即可。

- FSMC_DataLatency(用于NorFLASH,SRAM无用,跳)

本成员设置数据保持时间,它表示在读取第个数据之前要等待的周期数,该周期指同步时钟的周期,本参数仅用于同步NOR FLASH类型的存储器,控制其它类型的存储器时,本参数无效。 - FSMC_ AccessMode

本成员设置存储器访问模式,不同的模式下FSMC访问存储器地址时引脚输出的时序不一样,可选FSMC_ AccessMode_ A/B/C/D模式。一般 来说控制SRAM时使用A模式。

FSMC_NORSRAMInitTypeDef 结构体

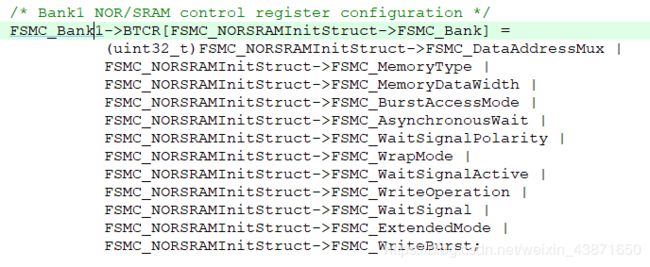

FSMC初始化结构体,除最后两个成员是上一小节讲解的时序配置外,其它结构体成员的配置都对应到FSMCBCR中的寄存器位。

typedef struct

{

uint32_t FSMC_Bank; /*设置要控制的Bank区域*/

uint32_t FSMC_DataAddressMux; /*设置地址总线与数据总线是否复用*/

uint32_t FSMC_MemoryType; /*设置存储器的类型*/

uint32_t FSMC_MemoryDatawidth; /*设置存储器的数据宽度*/

uint32_t FSMC_BurstAccessMode; /*设置是否支持突发访问模式, 只支持同步类型的存储器*/

uint32_t FSMC_AsynchronousWait; /* 设置是否使能在同步传输时的等待信号,*/

uint32_t FSMC_WaitSignalPolarity; /* 设置等待信号的极性*/

uint32_t FSMC_WrapMode; /*设置是否支持对 齐的突发模式*/

uint32_t FSMC_WaitsignalActive; /*配置等待信 号在等待前有效还是等待期间有效*/

uint32_t FSMC_WriteOperation; /* 设置是否写使能*/

uint32_t FSMC_WaitSignal; /*设置是否使能等待状态插入*/

uint32_t FSMC_ExtendedMode ; /*设置是否使能扩展模式*/

uint32_t FSMC_WriteBurst; /* 设置是否使能写突发操作*/

/*当不使用扩展模式时,本参数用于配置读写时序,否则用于配置读时序*/

FSMC_NORSRAMTimingInitTypeDef* FSMC_ReadWriteTimingStruct;

/*当使用扩展模式时,本参数用于配置写时序*/

FSMC_NORSRAMTimingInitTypeDef* FSMC_WriteTimingStruct;

} FSMC_NORSRAMInitTypeDef; .

- FSMC_Bank

本成员用于选择FSMC映射的存储区域,它的可选参数以及相应的内核地址映射范围见下面的表格

我们知道FSMC把外设存储器分成了4个块,每个块分为4个区,而通过这个FSMC_Bank参数选择对应区的寄存器组。

根据外接存储器接了那个片选引脚设置成相应的宏,如外接存储器接NE4,就使用 FSMC_Bank1_NORSRAM4 这个宏。

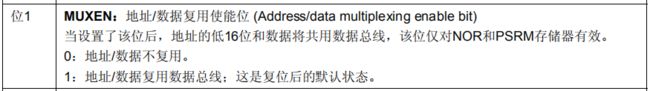

- FSMC_ DataAddressMux(用于NorFLASH,SRAM无用,跳)

本成员用于设置地址总线与数据总线是否复用(FSMC_ DataAddressMux_ _Enable /Disable),在控制NOR FLASH时,可以地址总线与数据总线可以分时复用,以减少使用STM32信号线的数量。

外设存储器是SRAM设置为DISABLE

- FSMC_MemoryType

本成员用于设置要控制的存储器类型,它支持控制的存储器类型为SRAM、PSRAM以及NOR FL ASH(FSMC_MemoryType_SRAM/PSRAMNOR)。

SRAM 设置为FSMC_MemoryType_SRAM 这个宏定义就行。

- FSMC_MemoryDataWidth

本成员用于设置要控制的存储器的数据宽度,可选择设置成8或16位(FSMC_MemoryDataWidth_8b /16b)。

使用的SRAM是16位的,配置成FSMC_MemoryDataWidth_b16b就行。 - FSMC_BurstAccessMode(异步存储器无用)

本成员用于设置是否使用突发访问模式(FSMC_BurstAccessMode_Enable/Disable), 突发访问模式是指发送一地址

后连续读取多个数据,非突发模式下每访问一个数据都需要输入一个地址,仅在控制同步类型的存储器时才能使用突发模式。

异步存储器SRAM设置成FSMC_BurstAccessMode_Disable就行 - FSMC_AsynchronousWait(异步存储器无用)

本成员用于设置是否使能在同步传输时使用的等待信号(FSMC_ AsynchronousWait_ Enable/Disable), 在控制同步类型的NOR或PSRAM时,存储器可以使用FSMC_ NWAIT 引脚通知STM32需要等待。

异步存储器SRAM设置成FSMC_AsynchronousWait_Disable就行 - FSMC_WaitSignalPolarity(异步存储器无用)

本成员用于设置等待信号的有效极性,即要求等待时,使用高电平还是低电平(FSMC_WaitSignalPolarity_High/L ow)。

异步存储器SRAM随便设置一个宏就行,如FSMC_WaitSignalPolarity_Low - FSMC_WrapMode(异步存储器无用,不使用突发模式,跳)

本成员用于设置是否支持把非对齐的AHB突发操作分割成2次线性操作(FSMC_WrapMode_Enable/Disable), 该配置仅在突发模式下有效。 - FSMC_WaitSignalActive(异步存储器无用,不使用突发模式,跳)

本成员用于配置在突发传输模式时,决定存储器是在等待状态之前的个数据周期有效还是在等待状态期间有效(FSMC_WaitSignalActive_BeforeWaitState/DuringWaitState)。

异步存储器SRAM随便设置一个宏就行,如FSMC_WaitSignalActive_BeforeWaitState - FSMC_ WriteOperation

这个成员用于设置是否写使能(FSMC_WriteOperation_Enable/Disable),禁止写使能的话FSMC只能从存储器中读取数据,不能写入。

需要开启写使能,设置成 FSMC_WriteOperation_Enable - FSMC_ WaitSignal(异步存储器无用,不使用突发模式,跳)

本成员用于设置当存储器牌突发传输模式时,是否允许通过NWAIT信号插入等待状态(FSMC_ WaitSignal_ Enable/Disable)。 - FSMC_ExtendedMode

本成员用于设置是否使用扩展模式(FSMC_ ExtendedMode_ Enable/Disable),

在非扩展模式下,对存储器的读写时序使用同样的配置,对存储器读写的时序都只使用FSMC_BCR寄存器中的配置,即下面的FSMC_ReadWrite_TimingStruct结构体成员;

在扩展模式下,对存储器的读写时序可以分开配置,读时序使用FSMC_BCR寄存器,写时序使用FSMC_ BWTR寄存器的配置,即下面的FSMC_Write_TimingStruct结构体。

- FSMC_WriteBurst(异步存储器无用,不使用突发模式,跳)

不使用突发写操作,设置成FSMC_WriteBurst_Disable - FSMC_ ReadWriteTimingStruct

本成员是一个指针,赋值时使用上一小节中讲解的时序结构体FSMC_ NORSRAMInitTypeDef设置, 当不使用扩展模式时,读写时序都使用本成员的参数配置。

二. 根据SRAM时序配置结构体

i. 根据SRAM时序配置FSMC写时序结构体

- tWC:

SRAM WriteCycleTime写时序周期,最小55ns,所以拟时序的周期要大于55ns.

((ADDSET+1) + (DATAST+1))HCLK > 55ns

- tSA:

Address Setup Time 地址建立时间 ,最小位0,故要地址建立周期(ADDSET+1)大于0ns

(ADDSET+1)HCLK > 0ns - tPWE:

WE Pulse Width 写使能宽度,最小是40ns,故数据建立周期(DATAST+1)要大于40ns

(DATAST+1)HCLK > 40ns

代码如下:

//一个 HCLK时钟周期 为 1/72us = 0.0138us = 13.8ns。

//按照如下配置(ADDSET+1) + (DATAST+1) = 13.8 +41.4 = 55.2ns >55ns

FSMC_NORSRAMInitTypeDef FSMC_NORSRAMInitStructure;//初始化结构体

FSMC_NORSRAMTimingInitTypeDef writeTiming;//读时序结构体

writeTiming.FSMC_AddressSetupTime = 0x00; //地址建立时间为0+1个HCLK :1*13.8ns = 13.8ns

writeTiming.FSMC_DataSetupTime = 0x03; //数据保存时间为2+1个HCLK:3*13.8ns = 41.4ns

writeTiming.FSMC_AddressHoldTime = 0x00; //地址保持时间(ADDHLD)模式A未用到

writeTiming.FSMC_BusTurnAroundDuration = 0x00;

writeTiming.FSMC_CLKDivision = 0x00;

writeTiming.FSMC_DataLatency = 0x00;

writeTiming.FSMC_AccessMode = FSMC_AccessMode_A; //模式A

ii. 根据SRAM时序配置FSMC读时序结构体

- tRC:

SRAM Read CycleTime写时序周期,最小55ns,所以我们模拟时序的周期要大于55ns.

((ADDSET+1) + (DATAST+1))HCLK > 55ns

- tAA:

Address Access Time 地址到达时间 ,最大55ns,所以要地址建立时间(ADDSET+1)小于55ns.

(ADDSET+1)HCLK > 0ns - tDOE:

OE Access Time 数据到达时间,最大25ns,即最多在25ns后给出有效的数据,所以数据采样时间(DATAST+1)要大于25ns.

(DATAST+1)HCLK > 25ns

//一个 HCLK时钟周期 为 1/72us = 0.0138us = 13.8ns。

//按照如下配置(ADDSET+1) + (DATAST+1) + 2HCLK = 13.8 + 27.6 + 27.6 = 69ns >55ns

FSMC_NORSRAMInitTypeDef FSMC_NORSRAMInitStructure;//初始化结构体

FSMC_NORSRAMTimingInitTypeDef readWriteTiming; //写时序结构体

readWriteTiming.FSMC_AddressSetupTime = 0x00; //地址建立时间为0+1个HCLK :1*13.8ns = 13.8ns

readWriteTiming.FSMC_DataSetupTime = 0x01; //数据保存时间为1+1个HCLK:2*13.8ns = 27.6ns

readWriteTiming.FSMC_AddressHoldTime = 0x00; //地址保持时间(ADDHLD)模式A未用到

readWriteTiming.FSMC_BusTurnAroundDuration = 0x00;

readWriteTiming.FSMC_CLKDivision = 0x00;

readWriteTiming.FSMC_DataLatency = 0x00;

readWriteTiming.FSMC_AccessMode = FSMC_AccessMode_A; //模式A

iii. FSMC总初始化结构体

FSMC_NORSRAMInitStructure.FSMC_Bank = FSMC_Bank1_NORSRAM4;// 这里我们使用NE4 ,也就对应BTCR[6],[7]。

FSMC_NORSRAMInitStructure.FSMC_DataAddressMux = FSMC_DataAddressMux_Disable; // 不复用数据地址

FSMC_NORSRAMInitStructure.FSMC_MemoryType =FSMC_MemoryType_SRAM;//SRAM

FSMC_NORSRAMInitStructure.FSMC_MemoryDataWidth = FSMC_MemoryDataWidth_16b;//存储器数据宽度为16bit

FSMC_NORSRAMInitStructure.FSMC_BurstAccessMode =FSMC_BurstAccessMode_Disable;//不使用突发访问模式

FSMC_NORSRAMInitStructure.FSMC_WaitSignalPolarity = FSMC_WaitSignalPolarity_Low;//设置等待信号的有效极性

FSMC_NORSRAMInitStructure.FSMC_AsynchronousWait=FSMC_AsynchronousWait_Disable; //是否使能等待信号

FSMC_NORSRAMInitStructure.FSMC_WrapMode = FSMC_WrapMode_Disable; //不支持部队去的突发操作

FSMC_NORSRAMInitStructure.FSMC_WaitSignalActive = FSMC_WaitSignalActive_BeforeWaitState; //设置等待信号插入时间

FSMC_NORSRAMInitStructure.FSMC_WriteOperation = FSMC_WriteOperation_Enable; // 存储器写使能

FSMC_NORSRAMInitStructure.FSMC_WaitSignal = FSMC_WaitSignal_Disable; //不使用等待信号

FSMC_NORSRAMInitStructure.FSMC_ExtendedMode = FSMC_ExtendedMode_Enable; // 读写使用不同的时序

FSMC_NORSRAMInitStructure.FSMC_WriteBurst = FSMC_WriteBurst_Disable; //不开启突发写操作

FSMC_NORSRAMInitStructure.FSMC_ReadWriteTimingStruct = &readWriteTiming; //读写时序

FSMC_NORSRAMInitStructure.FSMC_WriteTimingStruct = &writeTiming; //写时序

FSMC_NORSRAMInit(&FSMC_NORSRAMInitStructure); //初始化FSMC配置

FSMC_NORSRAMCmd(FSMC_Bank1_NORSRAM4, ENABLE); // 使能BANK1

根据SRAM时序配置配置SRAM总结

三. 根据ILI9341时序配置结构体

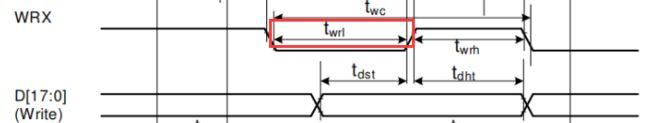

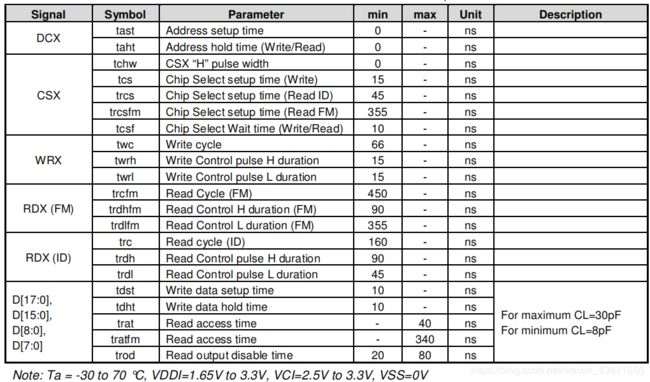

i. 根据ILI9341时序配置FSMC写时序结构体

注意:

在((ADDSET+1) + (DATAST+1))HCLK中,((ADDSET+1) + (DATAST))HCLK这段时间是保持写使能信号NWE低电平的时间,剩下的1HCLK是NWE保持高电平的默认时间

在数据建立周期FSMC才会操作数据总线传输数据

-

twrl:

写控制低电平信号最小时间为15ns,故可以设置FSMC模式B的地址建立周期(ADDSET+1)要15ns, 用来保证写控制低电平信号有效。

(ADDSET+1)HCLK > 15ns, (1+1) * 13.8 > 15 ,所以ADDSET可以设置为1保证写低电平有效 -

tdst、tdht:

tdst:数据设置时间最小是10ns,在这个周期内WRX线处于低电平。

tdht:数据保持时间,与 twrh写控制高电平的最小时间相同,是10ns,在这个周期内WRX线处于高电平。

观察时序图,我们设置 tdst数据设置时间 为1HCLK(13.8>10)就能满足数据设置最小时间的要求,我们不需要考虑tdht数据保持时间(看上面模式B时序图,NWE变成高电平后,会持续1HCLK=13.8ns,默认满足tdht了)

故我们只需考虑数据建立周期 DATAST 要大于10ns就行.

(DATAST )HCLK > 10ns,13.8>10 ,故DATAST 至少设置为1 -

twc

写时序周期,最小66ns,所以FSMC的一个写入操作周期((ADDSET+1) + (DATAST+1))HCLK要大于66ns.

((ADDSET+1) + (DATAST+1))HCLK > 66ns ,((1+1)+(2+1))·13.8 = 5·13.8 = 69ns>66ns

故ADDSET可以设置为1,DATAST可以设置为2

代码如下:

//一个 HCLK时钟周期 为 1/72us = 0.0138us = 13.8ns。

//按照如下配置(ADDSET+1) + (DATAST+1) = 13.8 +41.4 = 55.2ns >55ns

FSMC_NORSRAMInitTypeDef FSMC_NORSRAMInitStructure;//初始化结构体

FSMC_NORSRAMTimingInitTypeDef writeTiming;//读时序结构体

writeTiming.FSMC_AddressSetupTime = 0x01; //地址建立时间为1+1个HCLK :2*13.8ns = 27.6ns

writeTiming.FSMC_DataSetupTime = 0x02; //数据设置时间为2个HCLK:2*13.8ns = 27.6ns,数据保存时间为1个HCLK = 13.8ns

writeTiming.FSMC_AddressHoldTime = 0x00; //地址保持时间(ADDHLD)模式B未用到

writeTiming.FSMC_BusTurnAroundDuration = 0x00;

writeTiming.FSMC_CLKDivision = 0x00;

writeTiming.FSMC_DataLatency = 0x00;

writeTiming.FSMC_AccessMode = FSMC_AccessMode_B; //模式B

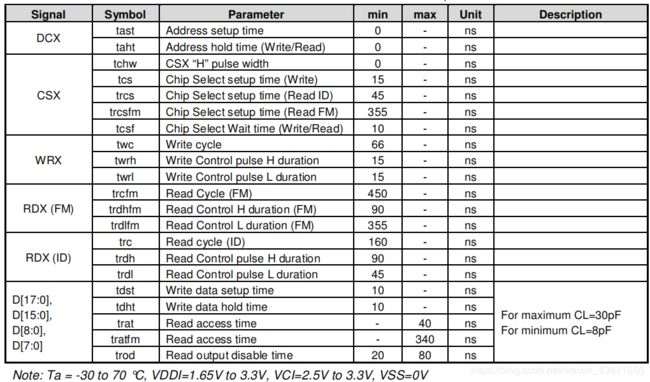

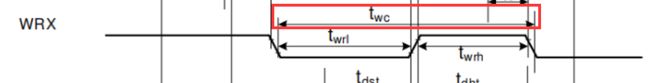

ii. 根据ILI9341时序配置FSMC读时序结构体

注意:RDX(ID)ID指LCD的ID号, RDX(FM)FM指帧缓存,即:GRAM

- trat,tratfm:

trat 表示读取ID的数据访问时间,最大为40ns

tratfm 表示读取GRAM的数据访问时间,最大为340ns

我们以读取ID数据的trat最大时间40ns为标准,设置小于trat的读取访问时间,这时也可以满足读GRAM的 tratfm的最大时间。

由时序图可以知道,经过这段trat/tratfm数据访问时间后,ILI9341将操作数据线传输被读取的数据。FSMC在(ADDSET+1)周期之后,进入(DATAST+1)HCLK周期之后将会进行数据采样。

所以我们设置(ADDSET+1)HCLK的时间要小于trat数据访问的最大时间,确保ILI9341芯片传输被读取的数据在FSMC在进行数据采样的之后再在数据线上传输。

(ADDSET+1)HCLK <40ns,(0+1)·13.8 = 13.8ns<40ns,所以ADDSET可以设置为0就可保证满足小于trat数据访问最大时间 - trdlfm:

trdlfm 表示 读取数据低电平的时间,最小为355ns

ILI9341时序图没有给出ILI9341操作数据线传输被读取的数据时的相关信息,我们最好做到满足其读取数据低电平的最小时间。

当然不做到也行,影响不大,只要在FSMC在(DATAST+1)的这个周期的数据采样中获取所有的要访问的数据就行。

(DATAST+1)要足够大,一般设置(DATAST+1)=16就可以了,这时DATAST设置为15。

//一个 HCLK时钟周期 为 1/72us = 0.0138us = 13.8ns。

//按照如下配置(ADDSET+1) + (DATAST+1) + 2HCLK = 13.8 + 27.6 + 27.6 = 69ns >55ns

FSMC_NORSRAMInitTypeDef FSMC_NORSRAMInitStructure;//初始化结构体

FSMC_NORSRAMTimingInitTypeDef readWriteTiming; //写时序结构体

readWriteTiming.FSMC_AddressSetupTime = 0x00; //第一段低电平时间为0+1个HCLK :1*13.8ns = 13.8ns

readWriteTiming.FSMC_DataSetupTime = 0x0f; //第二段低电平时间为15+1个HCLK:16*13.8ns = 220.8ns

readWriteTiming.FSMC_AddressHoldTime = 0x00; //地址保持时间(ADDHLD)模式A未用到

readWriteTiming.FSMC_BusTurnAroundDuration = 0x00;

readWriteTiming.FSMC_CLKDivision = 0x00;

readWriteTiming.FSMC_DataLatency = 0x00;

readWriteTiming.FSMC_AccessMode = FSMC_AccessMode_B; //模式A

iii. FSMC总初始化结构体

FSMC_NORSRAMInitStructure.FSMC_Bank = FSMC_Bank1_NORSRAM4;// 这里我们使用NE4 ,也就对应BTCR[6],[7]。

FSMC_NORSRAMInitStructure.FSMC_DataAddressMux = FSMC_DataAddressMux_Disable; // 不复用数据地址

FSMC_NORSRAMInitStructure.FSMC_MemoryType =FSMC_MemoryType_NOR;//NOR

FSMC_NORSRAMInitStructure.FSMC_MemoryDataWidth = FSMC_MemoryDataWidth_16b;//存储器数据宽度为16bit

FSMC_NORSRAMInitStructure.FSMC_BurstAccessMode =FSMC_BurstAccessMode_Disable;//不使用突发访问模式

FSMC_NORSRAMInitStructure.FSMC_WaitSignalPolarity = FSMC_WaitSignalPolarity_Low;//设置等待信号的有效极性

FSMC_NORSRAMInitStructure.FSMC_AsynchronousWait=FSMC_AsynchronousWait_Disable; //是否使能等待信号

FSMC_NORSRAMInitStructure.FSMC_WrapMode = FSMC_WrapMode_Disable; //不支持部队去的突发操作

FSMC_NORSRAMInitStructure.FSMC_WaitSignalActive = FSMC_WaitSignalActive_BeforeWaitState; //设置等待信号插入时间

FSMC_NORSRAMInitStructure.FSMC_WriteOperation = FSMC_WriteOperation_Enable; // 存储器写使能

FSMC_NORSRAMInitStructure.FSMC_WaitSignal = FSMC_WaitSignal_Disable; //不使用等待信号

FSMC_NORSRAMInitStructure.FSMC_ExtendedMode = FSMC_ExtendedMode_Enable; // 读写使用不同的时序

FSMC_NORSRAMInitStructure.FSMC_WriteBurst = FSMC_WriteBurst_Disable; //不开启突发写操作

FSMC_NORSRAMInitStructure.FSMC_ReadWriteTimingStruct = &readWriteTiming; //读写时序

FSMC_NORSRAMInitStructure.FSMC_WriteTimingStruct = &writeTiming; //写时序

FSMC_NORSRAMInit(&FSMC_NORSRAMInitStructure); //初始化FSMC配置

FSMC_NORSRAMCmd(FSMC_Bank1_NORSRAM4, ENABLE); // 使能BANK1

总结

想要编写时序相关的内容时,时序图一定要看懂。所以要懂得如何取看时序图。