NG Toolset开发笔记--5GNR Resource Grid(51)

4/1 update:

sendMsg3 is ok now, including:

*determine DMRS for Msg3 PUSCH

*Msg3 PUSCH time-domain/freq-domain resource mapping

*misc. update and bugfix to ngapp

(1) determine DMRS for msg3 PUSCH

freq-domain pattern of DMRS for msg3 PUSCH is similar to DMRS for PDSCH, while time-domain pattern of DMRS for msg3 PUSCH is different in case intra-slot frequency hopping is enabled for Msg3.

def getDmrsPuschTdFdPattern(self, dmrsType, tdMappingType, slivS, slivL, numFrontLoadSymbs, dmrsAddPos, cdmGroupsWoData, freqHop):

if freqHop == 'disabled' or freqHop == 'inter-slot':

if tdMappingType == 'Type A':

tdL0 = 3 if self.nrMibDmRsTypeAPosComb.currentText() == 'pos3' else 2

tdLd = slivS + slivL

else:

tdL0 = 0

tdLd = slivL

if numFrontLoadSymbs == 1:

tdLbar = self.nrDmrsPuschPosOneSymbWoIntraSlotFh['%s_%s_%s' % (tdLd, tdMappingType, dmrsAddPos)]

tdLap = [0] #ap for apostrophe, the (') character

else:

tdLbar = self.nrDmrsPuschPosTwoSymbsWoIntraSlotFh['%s_%s_%s' % (tdLd, tdMappingType, dmrsAddPos)]

tdLap = [0, 1] #ap for apostrophe, the (') character

tdLbar = list(tdLbar)

tdLbar[0] = tdL0

tdL = []

for i in tdLbar:

for j in tdLap:

tdL.append(i+j)

else:

#intra-slot frequency hopping

numSymbsPerHop = [math.floor(slivL / 2), slivL - math.floor(slivL / 2)]

tdL = [[], []]

for hop in range(2):

if tdMappingType == 'Type A':

tdL0 = 3 if self.nrMibDmRsTypeAPosComb.currentText() == 'pos3' else 2

tdLd = numSymbsPerHop[hop]

else:

tdL0 = 0

tdLd = numSymbsPerHop[hop]

#refer to 3GPP 38.211 vf40 6.4.1.1.3

#if the higher-layer parameter dmrs-AdditionalPosition is not set to 'pos0' and intra-slot frequency hopping is enabled according to clause 7.3.1.1.2 in [4, TS 38.212] and by higher layer, Tables 6.4.1.1.3-6 shall be used assuming dmrs-AdditionalPosition is equal to 'pos1' for each hop.

if dmrsAddPos != 'pos0':

dmrsAddPos = 'pos1'

if numFrontLoadSymbs == 1:

tdLbar = self.nrDmrsPuschPosOneSymbWithIntraSlotFh['%s_%s_%s_%s_%s' % (tdLd, tdMappingType, tdL0, dmrsAddPos, '1st' if hop == 0 else '2nd')]

tdLap = [0] #ap for apostrophe, the (') character

else:

return (None, None)

for i in tdLbar:

for j in tdLap:

tdL[hop].append(i+j)For example:

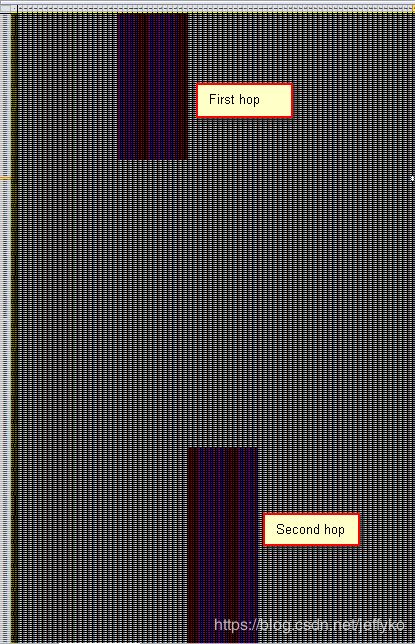

partial configurations for msg3 pusch

contents of ["msg3Pusch"]: {'muPusch': '1', 'tdRa': '14', 'tdMappingType': 'Type A', 'tdK2': '4', 'tdDelta': '3', 'tdSliv': '27', 'tdStartSymb': '0', 'tdNumSymbs': '14', 'fdRaType': 'RA Type1', 'fdFreqHop': 'enabled', 'fdRa': '0100000100001101', 'fdStartRb': '0', 'fdNumRbs': '62', 'fdSecondHopFreqOff': '68', 'mcsCw0': '2', 'tbs': '3624'}

contents of ["dmrsMsg3"]: {'dmrsType': 'Type 1', 'dmrsAddPos': 'pos1', 'maxLength': 'len1', 'dmrsPorts': '0', 'cdmGroupsWoData': '2', 'numFrontLoadSymbs': '1'}time/freq-domain DMRS pattern:

'tdL': [[2, 6], [0, 4]], 'fdK': [1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1]}(2) Msg3 PUSCH time/freq-domain resource mapping

First thing is convert RAR UL Grant slot which is based on mibCommonScs into PUSCH slot which is based on iniUlBwpScs:

#convert 'slot'+'msg2LastSymb' which based on commonScs into puschScs(initial ul bwp)

tmpStr = 'converting from commonScs(=%dKHz) to puschScs(=%dKHz): [hsfn=%d, sfn=%d, slot=%d, msg2LastSymb=%d] --> ' % (self.nrMibCommonScs, self.nrIniUlBwpScs, hsfn, sfn, slot, self.msg2LastSymb)

scaleTd = self.nrIniUlBwpScs / self.nrMibCommonScs

slotInPuschScs = math.ceil(((slot * self.nrSymbPerSlotNormCp + self.msg2LastSymb) * scaleTd - 1) // self.nrSymbPerSlotNormCp)

tmpStr = tmpStr + '[hsfn=%d, sfn=%d, slot=%d]' % (hsfn, sfn, slotInPuschScs)

self.ngwin.logEdit.append(tmpStr)

qApp.processEvents()Msg3 PUSCH slot is calculated as: n + k2 + delta

slotMsg3 = slotInPuschScs + self.nrMsg3TdK2 + self.nrMsg3TdDeltaIf intra-slot frequency hopping is enabled, we need to calculate numSymbsPerHop and startRbPerHop:

#intra-slot frequency hopping

numSymbsPerHop = [math.floor(self.nrMsg3TdNumSymbs / 2), self.nrMsg3TdNumSymbs - math.floor(self.nrMsg3TdNumSymbs / 2)]

startRbPerHop = [self.nrMsg3FdStartRb, (self.nrMsg3FdStartRb + self.nrMsg3FdSecondHopFreqOff) % self.nrIniUlBwpNumRbs]Note: Freq-domain resource assignment of Msg3 configuration is a bit tricky:

*the 14bits 'frequency domain resource assignment' in RAR UL grant, may needs truncation and insertion in order to be interpereted as valid DCI 0_0 fields.

*when freq-hopping is enabled, the first 1/2 MSBs(N_UL_hop) determines 'second hop frequency offset' and the possible inserted bits must be all zeros as specified in 38.213 8.3.

*when freq-hopping is enabled, L_RB field(part of RIV) needs careful design so that, Msg3 of both hops don't across the upper boundary of the carrier.

Example valid configuration as below:

Example configurations:

contents of ["freqBand"]: {'opBand': 'n41', 'duplexMode': 'TDD', 'maxDlFreq': 2690, 'freqRange': 'FR1'}

contents of ["ssbGrid"]: {'scs': '30KHz', 'pattern': 'Case C', 'minGuardBand240k': 'NA', 'kSsb': '0', 'nCrbSsb': '30'}

contents of ["ssbBurst"]: {'maxL': 8, 'inOneGroup': '10000000', 'groupPresence': 'NA', 'period': '10ms'}

contents of ["mib"]: {'sfn': '0', 'hrf': '0', 'dmrsTypeAPos': 'pos2', 'commonScs': '30KHz', 'rmsiCoreset0': '10', 'rmsiCss0': '0', 'coreset0MultiplexingPat': 1, 'coreset0NumRbs': 48, 'coreset0NumSymbs': 1, 'coreset0OffsetList': (12,), 'coreset0Offset': 12, 'coreset0StartRb': 0}

contents of ["carrierGrid"]: {'scs': '30KHz', 'bw': '100MHz', 'numRbs': '273', 'minGuardBand': '3'}

contents of ["pci"]: 0

contents of ["numUeAp"]: 4Tx

contents of ["tddCfg"]: {'refScs': '30KHz', 'pat1Period': '5ms', 'pat1NumDlSlots': '7', 'pat1NumDlSymbs': '6', 'pat1NumUlSymbs': '4', 'pat1NumUlSlots': '2', 'pat2Period': 'not used', 'pat2NumDlSlots': '', 'pat2NumDlSymbs': '', 'pat2NumUlSymbs': '', 'pat2NumUlSlots': ''}

contents of ["css0"]: {'aggLevel': '4', 'numCandidates': 'n4'}

contents of ["dci10Sib1"]: {'rnti': '0xFFFF', 'muPdcch': '1', 'muPdsch': '1', 'tdRa': '0', 'tdMappingType': 'Type A', 'tdK0': '0', 'tdSliv': '53', 'tdStartSymb': '2', 'tdNumSymbs': '12', 'fdRaType': 'RA Type1', 'fdRa': '00001011111', 'fdStartRb': '0', 'fdNumRbs': '48', 'fdVrbPrbMappingType': 'interleaved', 'fdBundleSize': 'n2', 'mcsCw0': '2', 'tbs': '2408'}

contents of ["dci10Msg2"]: {'rnti': '0x0001', 'muPdcch': '1', 'muPdsch': '1', 'tdRa': '11', 'tdMappingType': 'Type A', 'tdK0': '0', 'tdSliv': '40', 'tdStartSymb': '1', 'tdNumSymbs': '13', 'fdRaType': 'RA Type1', 'fdRa': '00001011111', 'fdStartRb': '0', 'fdNumRbs': '48', 'fdVrbPrbMappingType': 'interleaved', 'fdBundleSize': 'n2', 'mcsCw0': '2', 'tbScaling': '0', 'tbs': '2600'}

contents of ["msg3Pusch"]: {'muPusch': '1', 'tdRa': '14', 'tdMappingType': 'Type A', 'tdK2': '4', 'tdDelta': '3', 'tdSliv': '27', 'tdStartSymb': '0', 'tdNumSymbs': '14', 'fdRaType': 'RA Type1', 'fdFreqHop': 'enabled', 'fdRa': '0100000100001101', 'fdStartRb': '0', 'fdNumRbs': '62', 'fdSecondHopFreqOff': '68', 'mcsCw0': '2', 'tbs': '3624'}

contents of ["iniDlBwp"]: {'bwpId': '0', 'scs': '30KHz', 'cp': 'normal', 'locAndBw': '12925', 'startRb': '0', 'numRbs': '48'}

contents of ["dmrsSib1"]: {'dmrsType': 'Type 1', 'dmrsAddPos': 'pos2', 'maxLength': 'len1', 'dmrsPorts': '0', 'cdmGroupsWoData': '2', 'numFrontLoadSymbs': '1', 'tdL': [2, 7, 11], 'fdK': [1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1]}

contents of ["dmrsMsg2"]: {'dmrsType': 'Type 1', 'dmrsAddPos': 'pos2', 'maxLength': 'len1', 'dmrsPorts': '0', 'cdmGroupsWoData': '2', 'numFrontLoadSymbs': '1', 'tdL': [2, 7, 11], 'fdK': [1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1]}

contents of ["iniUlBwp"]: {'bwpId': '0', 'scs': '30KHz', 'cp': 'normal', 'locAndBw': '1099', 'startRb': '0', 'numRbs': '273'}

contents of ["rach"]: {'prachConfId': '160', 'raFormat': 'B4', 'raX': 1, 'raY': (0,), 'raSubfNumFr1SlotNumFr2': (9,), 'raStartingSymb': 2, 'raNumSlotsPerSubfFr1Per60KSlotFr2': 1, 'raNumOccasionsPerSlot': 1, 'raDuration': 12, 'scs': '30KHz', 'msg1Fdm': '1', 'msg1FreqStart': '0', 'raRespWin': 'sl20', 'totNumPreambs': '64', 'ssbPerRachOccasion': 'one', 'cbPreambsPerSsb': '64', 'msg3Tp': 'disabled', 'raLen': 139, 'raNumRbs': 12, 'raKBar': 2}

contents of ["dmrsMsg3"]: {'dmrsType': 'Type 1', 'dmrsAddPos': 'pos1', 'maxLength': 'len1', 'dmrsPorts': '0', 'cdmGroupsWoData': '2', 'numFrontLoadSymbs': '1', 'tdL': [[2, 6], [0, 4]], 'fdK': [1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1]}

contents of ["advanced"]: {'bestSsb': 'NA', 'sib1PdcchSlot': '1', 'sib1PdcchCand': 'NA', 'prachOccasion': 'NA', 'msg2PdcchOcc': '1', 'msg2PdcchCand': 'NA'}Msg3 PUSCH mapping when 'intra-slot FH' is enabled:

(3) Misc update and bugfix to ngapp

*add function to import configurations directly, so that we don't need to live with the frustrating 'ui config-failed-ui config once more' process;

*as listed below: