- FPGA小白到项目实战:Verilog+Vivado全流程通关指南(附光学类岗位技能映射)

阿牛的药铺

算法移植部署fpga开发verilog

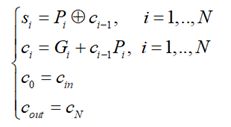

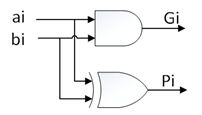

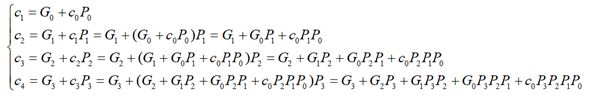

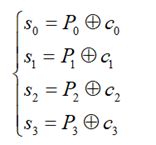

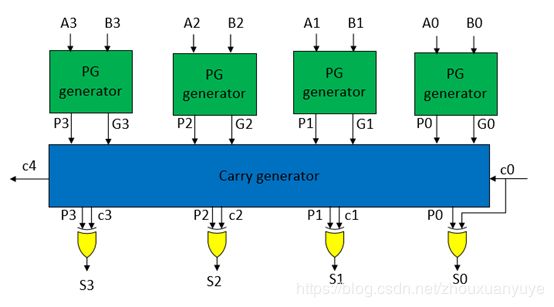

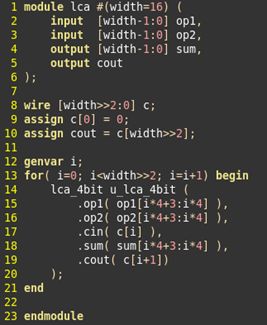

FPGA小白到项目实战:Verilog+Vivado全流程通关指南(附光学类岗位技能映射)引言:为什么这个FPGA入门路线能帮你快速上岗?本文设计了一条**"Verilog语法→工具链操作→光学项目实战→岗位技能对标"的阶梯式学习路径。不同于泛泛而谈的FPGA教程,我们聚焦光学类产品开发**核心能力(时序接口设计、图像处理算法移植、高速接口应用),通过3个递进式项目(从LED闪烁到图像边缘检测),

- Java设计模式实战:高频场景解析与避坑指南

mckim_

笔记学习java设计模式

引言设计模式是软件开发的基石,但许多开发者面对23种模式时容易陷入“学完就忘”或“滥用模式”的困境。本文从工业级项目视角出发,精选10种高频设计模式,结合真实代码案例与主流框架应用,帮你建立模式思维,拒绝纸上谈兵。一、创建型模式:告别new的暴力美学1.工厂方法模式(FactoryMethod)核心痛点:对象创建逻辑散落各处,难以统一管理。场景案例:电商平台需要支持多种支付方式(支付宝、微信、银联

- 比亚迪创新脉冲自加热技术深度解析

百态老人

算法数据库

一、技术原理与核心创新比亚迪脉冲自加热技术通过电池包内部能量闭环利用实现低温环境下的高效自加热,其核心原理可分解为以下三级机制:内阻产热机制将电池包物理分割为两组(A/B),通过高频充放电(频率达数百Hz)使电流流经高内阻电芯产生焦耳热。在-30℃环境下,电池内阻可升高至常温的3-4倍,此时焦耳热功率密度可达:P=I2⋅Rint(其中I为脉冲电流,Rint为低温内阻)P=I^2\cdotR_{in

- 技术类岗位面试中经典问题总结分享

1.谈淡你的最成功/失败的经历,你现在回去(时光倒流)怎么做2.你做过的一个项目/事例,说说过程(观是否谈结果)过程中,怎么进行信息检索的3.请你对我进行一个评价(观察是否谈到缺点)4.请用一句话介绍自己(总结十逻辑思维)5.你所学的课程中最喜欢/了解哪一个,请淡谈课程内容6.请描述一下用单片机点亮一个流水灯的全过程/请描述AD绘制PCB板的全过程/请详细描述用C语编辑环境输出一个Hellow,w

- 电子电气架构 --- 车载芯片SOC简介

汽车电子实验室

车辆信息安全思考架构职场和发展网络协议电子电气架构实时系统评价的概述车载芯片SOC简介

我是穿拖鞋的汉子,魔都中坚持长期主义的汽车电子工程师。老规矩,分享一段喜欢的文字,避免自己成为高知识低文化的工程师:做到欲望极简,了解自己的真实欲望,不受外在潮流的影响,不盲从,不跟风。把自己的精力全部用在自己。一是去掉多余,凡事找规律,基础是诚信;二是系统思考、大胆设计、小心求证;三是“一张纸制度”,也就是无论多么复杂的工作内容,要在一张纸上描述清楚;四是要坚决反对虎头蛇尾,反对繁文缛节,反对老

- YOLOv5基础 | 万字长文带你深度解析yolov5s.yaml配置文件

小哥谈

YOLO算法:基础+进阶+改进YOLO人工智能目标检测机器学习计算机视觉深度学习

前言:Hello大家好,我是小哥谈。配置文件yolov5s.yaml在YOLOv5模型训练过程中发挥着至关重要的作用,属于初学者必知必会的文件!在YOLOv5-6.0版本源码中,配置了5种不同大小的网络模型,分别是YOLOv5n、YOLOv5s、YOLOv5m、YOLOv5l、YOLOv5x,其中YOLOv5n是网络深度和宽度最小但检测速度最快的模型,其他4种模型都是在YOLOv5n的基础上不断加

- 百万级智能电动车“方案”揭秘:域控制器硬件全方位拆解与选型宝典

空间机器人

人工智能

百万级智能电动车“方案”揭秘:域控制器硬件全方位拆解与选型宝典大家好!今天带你深入了解百万级智能电动车的“大脑”——智能域控制器。这玩意可不是简单的电子盒子,而是融合了计算、控制、通信、电源多项硬核技术的超级中枢。要打造一个靠谱的智能车,域控制器的设计和选型就是核心中的核心!我将结合实际项目经验,帮你用最通俗的语言,剖析每个模块的作用和选型关键。来,跟我一起细品1️⃣计算核心:算力为王,双芯合璧才

- HT-LINK ICE:海速芯32Gbps信号调理芯片,40dB补偿+国产自主,打破高速互联瓶颈!

深圳市尚想信息技术有限公司

海速芯TENX仿真器数据中心烧录芯片AI服务器

HT-LINKICE(TENX海速芯)产品解析与推广文案一、产品定位HT-LINKICE是TENX海速芯推出的高速信号调理芯片,专为PCIe5.0/6.0、USB4、Thunderbolt等超高速接口设计,提供信号完整性增强和时钟恢复功能,适用于数据中心、AI服务器和高性能计算设备。二、核心功能与参数特性参数/性能协议支持PCIe5.0(32GT/s)、USB4(40Gbps)、Thunderbo

- 芯谷科技--双运算放大器D4558

Silicore_Emma

科技运算放大器音频放大音频设备医疗仪器

在现代电子系统中,运算放大器作为信号处理的核心元件,其性能直接影响到整个系统的稳定性和精度。D4558双运算放大器,凭借其卓越的性能和广泛的应用适配性,为工程师提供了可靠的信号处理解决方案。产品简介D4558是一款由两个高性能运算放大器组成的集成电路,具有高增益、低噪声、高输入阻抗、优秀的通道分离度、宽工作电压范围和内部频率补偿等特点。它支持双电源或单电源工作模式,主要应用于音频信号放大、有源滤波

- 计算机网络8832号答案,2013年4月份自考试计算机网络原理04741答案.doc

2013年4月份自考试计算机网络原理04741答案全国2013年4月高等教育自学考试计算机网络原理试题课程代码:04741请考生按规定用笔将所有试题的答案涂、写在答题纸上。选择题部分1.无线应用协议WAP的特点是A.支持手机上网B.不需要基站C.基于分组交换D.无固定路由器2.智能大厦及计算机网络的信息基础设施是A.通信自动化B.楼宇自动化C.结构化综合布线D.现代通信网络3.因特网工程特别任务组

- ERP项目与ERP软件的关系

ERP软件是ERP项目的组成部分,是ERP项目的工具,在整个ERP项目通常占总成本的30%左右,其余全部是ERP咨询顾问的服务费用。ERP项目的核心是组织变革,是为了将“游击队”改造成为“正规军”以适应“集团化作战”的需要。谈ERP之谈ERP软件,不谈组织变革,不谈咨询顾问服务,这是缘木求鱼、本末倒置。为什么组织变革是关键?我们用“将‘游击队’改造成为‘正规军’以适应‘集团化作战’的需要”来形容E

- Python量化策略与回测框架实战:从“纸上谈兵”到“真金白银”的第一步(系列第2篇)

Natsume1710

python开发语言github

作者:GitHub项目地址Awesome-QuantDev-Learn本文为量化开发学习路线系列第2篇,欢迎收藏与关注。引言:为什么选择Python作为量化入门的起点?在上一篇文章中,我们详细讲解了量化开发的基本框架与开发者思维的转变路径。那么,具体要如何开始第一步实践呢?答案是:从Python入门。Python以其快速原型开发能力、丰富的数据分析工具包,以及良好的社区生态,已经成为全球范围内量化

- 2022项目实训“异步分布式联邦学习”第五周报告

一、本周工作进度我在本周的工作进度主要集中于两个技术要点——即Axios和WebSocket。这两种技术方法有着本质上的不同,因而具体实现出来之后的效果也有所不同,下面将会分别说明。1.Axios(Ajax封装)首先要谈的内容是Axios,Axios是一个基于promise的HTTP库,是目前前端最流行的ajax请求库。Axios的优势在于,相比传统的Ajax本身是针对MVC的编程,Axios更加

- 诊断工程师进阶篇 --- 车载诊断怎么与时俱进?

汽车电子实验室

漫谈UDS诊断协议系列车载电子电气架构诊断工程师进阶篇车载诊断怎么与时俱进?汽车中央控制单元HPC软件架构人工智能

我是穿拖鞋的汉子,魔都中坚持长期主义的汽车电子工程师。老规矩,分享一段喜欢的文字,避免自己成为高知识低文化的工程师:做到欲望极简,了解自己的真实欲望,不受外在潮流的影响,不盲从,不跟风。把自己的精力全部用在自己。一是去掉多余,凡事找规律,基础是诚信;二是系统思考、大胆设计、小心求证;三是“一张纸制度”,也就是无论多么复杂的工作内容,要在一张纸上描述清楚;四是要坚决反对虎头蛇尾,反对繁文缛节,反对老

- 替代进口SCA7606【智芯微】国产高精度电流传感器 工业新能源电网专用

深圳市尚想信息技术有限公司

智芯微传感器电流传感器新能源智能电网工业控制代替进口

SCA7606(智芯微)产品解析与推广文案一、产品概述SCA7606是智芯微电子(ZXMICRO)推出的一款高精度数字隔离式电流传感器芯片,采用霍尔效应+数字输出技术,专为工业控制、新能源、智能电网等领域的电流检测需求设计。二、核心功能与参数特性参数/功能检测类型隔离式电流检测(非接触式)量程±5A/±20A/±50A(多量程可选)输出方式数字输出(I²C/SPI),支持实时数据传输精度±1%FS

- 也谈一下 30+ 程序员的出路

写编程的木木

langchain产品经理python开发语言大模型

前言前两天和一个前端同学聊天,他说不准备再做前端了,准备去考公。不过难度也很大。从20152016年那会儿开始互联网行业爆发,到现在有7、8年了,当年20多岁的小伙子们,现在也都30+了大量的人面临这个问题:大龄程序员就业竞争力差,未来该如何安身立命?先说我个人的看法:除非你有其他更好的资源,否则没有更好的出路认真搞技术,保持技术能力,你大概率不会失业(至少外包还在招人,外包也不少挣…)考公之我见

- 模块化汽车基础设施的正面交锋---区域架构与域架构

汽车电子实验室

车载电子与软件框架汽车架构OEM怎么掌握软件开发能力ZEVonUDS-J1979车载通信网络槪述HPC软件架构

我是穿拖鞋的汉子,魔都中坚持长期主义的汽车电子工程师。老规矩,分享一段喜欢的文字,避免自己成为高知识低文化的工程师:做到欲望极简,了解自己的真实欲望,不受外在潮流的影响,不盲从,不跟风。把自己的精力全部用在自己。一是去掉多余,凡事找规律,基础是诚信;二是系统思考、大胆设计、小心求证;三是“一张纸制度”,也就是无论多么复杂的工作内容,要在一张纸上描述清楚;四是要坚决反对虎头蛇尾,反对繁文缛节,反对老

- 车载软件架构 --- OEM企业文化与软件的冲突

汽车电子实验室

电子电器架构开发流程OEM怎么掌握软件开发能力ZEVonUDS-J1979车载通信网络槪述汽车HPC软件架构

我是穿拖鞋的汉子,魔都中坚持长期主义的汽车电子工程师。老规矩,分享一段喜欢的文字,避免自己成为高知识低文化的工程师:做到欲望极简,了解自己的真实欲望,不受外在潮流的影响,不盲从,不跟风。把自己的精力全部用在自己。一是去掉多余,凡事找规律,基础是诚信;二是系统思考、大胆设计、小心求证;三是“一张纸制度”,也就是无论多么复杂的工作内容,要在一张纸上描述清楚;四是要坚决反对虎头蛇尾,反对繁文缛节,反对老

- Linux第五节:基础IO

零、引言0.1重谈文件空文件,也要在磁盘中占据空间文件=文件类容+文件属性文件操作=对内容+对属性or对内容和属性标定一个文件,必须使用:文件路径+文件名「唯一性」如果没有指明对应的文件路径,默认就是在当前路径进行文件访问当我们把fopen/fclose/fread/fwrite等接口写完,代码编译之后,形成的二进制可执行程序,但是没有运行,文件对应的操作有没有执行呢?----没有----对文件操

- 电子电气诊断架构 --- HPC车载诊断

汽车电子实验室

车载电子电气架构漫谈UDS诊断协议系列架构

我是穿拖鞋的汉子,魔都中坚持长期主义的汽车电子工程师。老规矩,分享一段喜欢的文字,避免自己成为高知识低文化的工程师:做到欲望极简,了解自己的真实欲望,不受外在潮流的影响,不盲从,不跟风。把自己的精力全部用在自己。一是去掉多余,凡事找规律,基础是诚信;二是系统思考、大胆设计、小心求证;三是“一张纸制度”,也就是无论多么复杂的工作内容,要在一张纸上描述清楚;四是要坚决反对虎头蛇尾,反对繁文缛节,反对老

- 电子电气架构 --- 涵盖“诊断与 ECU 平台”领域特有项目要求(上)

汽车电子实验室

车载电子电气架构车载电子与软件框架电子电器架构开发流程架构HPC软件架构ZEVonUDS-J1979车载通信网络槪述汽车

我是穿拖鞋的汉子,魔都中坚持长期主义的汽车电子工程师。老规矩,分享一段喜欢的文字,避免自己成为高知识低文化的工程师:做到欲望极简,了解自己的真实欲望,不受外在潮流的影响,不盲从,不跟风。把自己的精力全部用在自己。一是去掉多余,凡事找规律,基础是诚信;二是系统思考、大胆设计、小心求证;三是“一张纸制度”,也就是无论多么复杂的工作内容,要在一张纸上描述清楚;四是要坚决反对虎头蛇尾,反对繁文缛节,反对老

- 车载电子电气架构 --- 从车窗演进看车联网的需求、发展与选择

汽车电子实验室

思考车载总线类型架构分布式电子电气架构网络协议实时系统评价的概述职场和发展

我是穿拖鞋的汉子,魔都中坚持长期主义的汽车电子工程师。老规矩,分享一段喜欢的文字,避免自己成为高知识低文化的工程师:做到欲望极简,了解自己的真实欲望,不受外在潮流的影响,不盲从,不跟风。把自己的精力全部用在自己。一是去掉多余,凡事找规律,基础是诚信;二是系统思考、大胆设计、小心求证;三是“一张纸制度”,也就是无论多么复杂的工作内容,要在一张纸上描述清楚;四是要坚决反对虎头蛇尾,反对繁文缛节,反对老

- 车载诊断架构 --- 经典ECU的基石与未来系统的挑战

我是穿拖鞋的汉子,魔都中坚持长期主义的汽车电子工程师。老规矩,分享一段喜欢的文字,避免自己成为高知识低文化的工程师:做到欲望极简,了解自己的真实欲望,不受外在潮流的影响,不盲从,不跟风。把自己的精力全部用在自己。一是去掉多余,凡事找规律,基础是诚信;二是系统思考、大胆设计、小心求证;三是“一张纸制度”,也就是无论多么复杂的工作内容,要在一张纸上描述清楚;四是要坚决反对虎头蛇尾,反对繁文缛节,反对老

- 数据治理 × 知识库 × 大模型:解开企业智能化转型的 “不可能三角”

“数据是新时代的石油,但未经治理的石油会堵塞管道;知识是企业的黄金矿脉,但缺乏提炼的矿石无法兑换价值;大模型是超级引擎,但燃料不足的引擎终将熄火。”——唯有四者协同,才能让企业的智能化转型从“纸上蓝图”走向“落地生根”。一、数据治理:AI时代的“地基工程”(1)数据治理的三大核心模块•标准化体系:◦数据字典与元数据管理:某跨国零售企业通过建立统一的数据字典(例如“销售额”统一定义为“含税交易金额”

- 一线双芯240W快充数据线USB TYPE-C接口eMarker芯片支持SOP通讯

2501_92672693

c语言开发语言

产品概述:PC102H是一款USBType-C接口的eMarker它符合USBPD3.2协议。PC102H可以直接由VBUS串接1K电阻供电,支持60VVBUS,应用于5芯方案。PC1O2H可以由VCONN供电,应用于双芯方案。使用SOT23,小23极简封装。PC102H适用于功率为240W48V/5A的线材。产品特征:#符合PD3.2:支持SOP的通讯、集成收发器(BMCPHY)、同时支持结构化

- 车载Tier1 supplier梳理

汽车电子实验室

车载总线类型思考汽车中央控制单元HPC软件架构人工智能汽车架构网络

我是穿拖鞋的汉子,魔都中坚持长期主义的汽车电子工程师。老规矩,分享一段喜欢的文字,避免自己成为高知识低文化的工程师:做到欲望极简,了解自己的真实欲望,不受外在潮流的影响,不盲从,不跟风。把自己的精力全部用在自己。一是去掉多余,凡事找规律,基础是诚信;二是系统思考、大胆设计、小心求证;三是“一张纸制度”,也就是无论多么复杂的工作内容,要在一张纸上描述清楚;四是要坚决反对虎头蛇尾,反对繁文缛节,反对老

- 车载软件架构 -- SOA服务分层设计原则

汽车电子实验室

电子电器架构开发流程车载电子电气架构架构电气电子架构开发的应对策略电子电气架构ECU刷写与busoff原则SOA服务分层设计原则

我是穿拖鞋的汉子,魔都中坚持长期主义的汽车电子工程师。老规矩,分享一段喜欢的文字,避免自己成为高知识低文化的工程师:做到欲望极简,了解自己的真实欲望,不受外在潮流的影响,不盲从,不跟风。把自己的精力全部用在自己。一是去掉多余,凡事找规律,基础是诚信;二是系统思考、大胆设计、小心求证;三是“一张纸制度”,也就是无论多么复杂的工作内容,要在一张纸上描述清楚;四是要坚决反对虎头蛇尾,反对繁文缛节,反对老

- 比斯特自动点焊机批发厂商概览

自动点焊机批发厂商主要集中于珠三角、长三角等制造业发达地区,如广东东莞、深圳及江苏无锡等地。这些厂商通过直销或供应链合作模式,为电子、汽车、电池等行业提供高性价比的自动化焊接设备,满足大规模生产需求。产品与技术特点批发厂商的产品涵盖多类点焊设备:精密电子点焊机:适用于微电子元件、漆包线、线路板焊接,强调高精度与无损伤加工。动力电池专用设备:如锂电池双面点焊机,支持18650/21700等电芯的高速

- 信创产品合规认证的一般流程,标准化产品、项目型产品

极创信息

健康医疗深度学习opencvsqliteeclipsegithubgit

信创产品合规认证流程分为标准化产品(通用产品)和项目型产品(特定项目交付)。核心流程概述基础适配与互认选择适配环境:确定目标适配的国产CPU架构(鲲鹏、飞腾、龙芯、兆芯、海光、申威等)、操作系统(麒麟、统信UOS、中科方德等)、数据库、中间件等。产品适配:在选定的信创环境下进行安装、部署、功能测试、性能调优等。获取证书:1.信创产品兼容性互认证证书:这是第一步也是最关键的证书。通常由产品厂商与基础

- GC3910S:一款高性能双通道直流电机驱动芯片

青牛科技-Allen

GLOBALCHIP单片机stm32嵌入式硬件机器人水泵医疗器械

在电子设备的广泛应用中,电机驱动芯片是实现运动控制的关键部件。浙江芯麦科技有限公司推出的GC3910S芯片,以其出色的性能和广泛的适用性,成为众多应用的理想选择。芯片概述GC3910S是一款双通道12V直流电机驱动芯片,适用于摄像机、玩具、机器人技术等多种低电压或电池供电的运动控制应用。该芯片能够驱动两个直流电机或一个步进电机,工作电压范围为4~15V,每通道可提供高达1.0A的持续输出电流和2.

- 安装数据库首次应用

Array_06

javaoraclesql

可是为什么再一次失败之后就变成直接跳过那个要求

enter full pathname of java.exe的界面

这个java.exe是你的Oracle 11g安装目录中例如:【F:\app\chen\product\11.2.0\dbhome_1\jdk\jre\bin】下的java.exe 。不是你的电脑安装的java jdk下的java.exe!

注意第一次,使用SQL D

- Weblogic Server Console密码修改和遗忘解决方法

bijian1013

Welogic

在工作中一同事将Weblogic的console的密码忘记了,通过网上查询资料解决,实践整理了一下。

一.修改Console密码

打开weblogic控制台,安全领域 --> myrealm -->&n

- IllegalStateException: Cannot forward a response that is already committed

Cwind

javaServlets

对于初学者来说,一个常见的误解是:当调用 forward() 或者 sendRedirect() 时控制流将会自动跳出原函数。标题所示错误通常是基于此误解而引起的。 示例代码:

protected void doPost() {

if (someCondition) {

sendRedirect();

}

forward(); // Thi

- 基于流的装饰设计模式

木zi_鸣

设计模式

当想要对已有类的对象进行功能增强时,可以定义一个类,将已有对象传入,基于已有的功能,并提供加强功能。

自定义的类成为装饰类

模仿BufferedReader,对Reader进行包装,体现装饰设计模式

装饰类通常会通过构造方法接受被装饰的对象,并基于被装饰的对象功能,提供更强的功能。

装饰模式比继承灵活,避免继承臃肿,降低了类与类之间的关系

装饰类因为增强已有对象,具备的功能该

- Linux中的uniq命令

被触发

linux

Linux命令uniq的作用是过滤重复部分显示文件内容,这个命令读取输入文件,并比较相邻的行。在正常情 况下,第二个及以后更多个重复行将被删去,行比较是根据所用字符集的排序序列进行的。该命令加工后的结果写到输出文件中。输入文件和输出文件必须不同。如 果输入文件用“- ”表示,则从标准输入读取。

AD:

uniq [选项] 文件

说明:这个命令读取输入文件,并比较相邻的行。在正常情况下,第二个

- 正则表达式Pattern

肆无忌惮_

Pattern

正则表达式是符合一定规则的表达式,用来专门操作字符串,对字符创进行匹配,切割,替换,获取。

例如,我们需要对QQ号码格式进行检验

规则是长度6~12位 不能0开头 只能是数字,我们可以一位一位进行比较,利用parseLong进行判断,或者是用正则表达式来匹配[1-9][0-9]{4,14} 或者 [1-9]\d{4,14}

&nbs

- Oracle高级查询之OVER (PARTITION BY ..)

知了ing

oraclesql

一、rank()/dense_rank() over(partition by ...order by ...)

现在客户有这样一个需求,查询每个部门工资最高的雇员的信息,相信有一定oracle应用知识的同学都能写出下面的SQL语句:

select e.ename, e.job, e.sal, e.deptno

from scott.emp e,

(se

- Python调试

矮蛋蛋

pythonpdb

原文地址:

http://blog.csdn.net/xuyuefei1988/article/details/19399137

1、下面网上收罗的资料初学者应该够用了,但对比IBM的Python 代码调试技巧:

IBM:包括 pdb 模块、利用 PyDev 和 Eclipse 集成进行调试、PyCharm 以及 Debug 日志进行调试:

http://www.ibm.com/d

- webservice传递自定义对象时函数为空,以及boolean不对应的问题

alleni123

webservice

今天在客户端调用方法

NodeStatus status=iservice.getNodeStatus().

结果NodeStatus的属性都是null。

进行debug之后,发现服务器端返回的确实是有值的对象。

后来发现原来是因为在客户端,NodeStatus的setter全部被我删除了。

本来是因为逻辑上不需要在客户端使用setter, 结果改了之后竟然不能获取带属性值的

- java如何干掉指针,又如何巧妙的通过引用来操作指针————>说的就是java指针

百合不是茶

C语言的强大在于可以直接操作指针的地址,通过改变指针的地址指向来达到更改地址的目的,又是由于c语言的指针过于强大,初学者很难掌握, java的出现解决了c,c++中指针的问题 java将指针封装在底层,开发人员是不能够去操作指针的地址,但是可以通过引用来间接的操作:

定义一个指针p来指向a的地址(&是地址符号):

- Eclipse打不开,提示“An error has occurred.See the log file ***/.log”

bijian1013

eclipse

打开eclipse工作目录的\.metadata\.log文件,发现如下错误:

!ENTRY org.eclipse.osgi 4 0 2012-09-10 09:28:57.139

!MESSAGE Application error

!STACK 1

java.lang.NoClassDefFoundError: org/eclipse/core/resources/IContai

- spring aop实例annotation方法实现

bijian1013

javaspringAOPannotation

在spring aop实例中我们通过配置xml文件来实现AOP,这里学习使用annotation来实现,使用annotation其实就是指明具体的aspect,pointcut和advice。1.申明一个切面(用一个类来实现)在这个切面里,包括了advice和pointcut

AdviceMethods.jav

- [Velocity一]Velocity语法基础入门

bit1129

velocity

用户和开发人员参考文档

http://velocity.apache.org/engine/releases/velocity-1.7/developer-guide.html

注释

1.行级注释##

2.多行注释#* *#

变量定义

使用$开头的字符串是变量定义,例如$var1, $var2,

赋值

使用#set为变量赋值,例

- 【Kafka十一】关于Kafka的副本管理

bit1129

kafka

1. 关于request.required.acks

request.required.acks控制者Producer写请求的什么时候可以确认写成功,默认是0,

0表示即不进行确认即返回。

1表示Leader写成功即返回,此时还没有进行写数据同步到其它Follower Partition中

-1表示根据指定的最少Partition确认后才返回,这个在

Th

- lua统计nginx内部变量数据

ronin47

lua nginx 统计

server {

listen 80;

server_name photo.domain.com;

location /{set $str $uri;

content_by_lua '

local url = ngx.var.uri

local res = ngx.location.capture(

- java-11.二叉树中节点的最大距离

bylijinnan

java

import java.util.ArrayList;

import java.util.List;

public class MaxLenInBinTree {

/*

a. 1

/ \

2 3

/ \ / \

4 5 6 7

max=4 pass "root"

- Netty源码学习-ReadTimeoutHandler

bylijinnan

javanetty

ReadTimeoutHandler的实现思路:

开启一个定时任务,如果在指定时间内没有接收到消息,则抛出ReadTimeoutException

这个异常的捕获,在开发中,交给跟在ReadTimeoutHandler后面的ChannelHandler,例如

private final ChannelHandler timeoutHandler =

new ReadTim

- jquery验证上传文件样式及大小(好用)

cngolon

文件上传jquery验证

<!DOCTYPE html>

<html>

<head>

<meta http-equiv="Content-Type" content="text/html; charset=utf-8" />

<script src="jquery1.8/jquery-1.8.0.

- 浏览器兼容【转】

cuishikuan

css浏览器IE

浏览器兼容问题一:不同浏览器的标签默认的外补丁和内补丁不同

问题症状:随便写几个标签,不加样式控制的情况下,各自的margin 和padding差异较大。

碰到频率:100%

解决方案:CSS里 *{margin:0;padding:0;}

备注:这个是最常见的也是最易解决的一个浏览器兼容性问题,几乎所有的CSS文件开头都会用通配符*来设

- Shell特殊变量:Shell $0, $#, $*, $@, $?, $$和命令行参数

daizj

shell$#$?特殊变量

前面已经讲到,变量名只能包含数字、字母和下划线,因为某些包含其他字符的变量有特殊含义,这样的变量被称为特殊变量。例如,$ 表示当前Shell进程的ID,即pid,看下面的代码:

$echo $$

运行结果

29949

特殊变量列表 变量 含义 $0 当前脚本的文件名 $n 传递给脚本或函数的参数。n 是一个数字,表示第几个参数。例如,第一个

- 程序设计KISS 原则-------KEEP IT SIMPLE, STUPID!

dcj3sjt126com

unix

翻到一本书,讲到编程一般原则是kiss:Keep It Simple, Stupid.对这个原则深有体会,其实不仅编程如此,而且系统架构也是如此。

KEEP IT SIMPLE, STUPID! 编写只做一件事情,并且要做好的程序;编写可以在一起工作的程序,编写处理文本流的程序,因为这是通用的接口。这就是UNIX哲学.所有的哲学真 正的浓缩为一个铁一样的定律,高明的工程师的神圣的“KISS 原

- android Activity间List传值

dcj3sjt126com

Activity

第一个Activity:

import java.util.ArrayList;import java.util.HashMap;import java.util.List;import java.util.Map;import android.app.Activity;import android.content.Intent;import android.os.Bundle;import a

- tomcat 设置java虚拟机内存

eksliang

tomcat 内存设置

转载请出自出处:http://eksliang.iteye.com/blog/2117772

http://eksliang.iteye.com/

常见的内存溢出有以下两种:

java.lang.OutOfMemoryError: PermGen space

java.lang.OutOfMemoryError: Java heap space

------------

- Android 数据库事务处理

gqdy365

android

使用SQLiteDatabase的beginTransaction()方法可以开启一个事务,程序执行到endTransaction() 方法时会检查事务的标志是否为成功,如果程序执行到endTransaction()之前调用了setTransactionSuccessful() 方法设置事务的标志为成功则提交事务,如果没有调用setTransactionSuccessful() 方法则回滚事务。事

- Java 打开浏览器

hw1287789687

打开网址open浏览器open browser打开url打开浏览器

使用java 语言如何打开浏览器呢?

我们先研究下在cmd窗口中,如何打开网址

使用IE 打开

D:\software\bin>cmd /c start iexplore http://hw1287789687.iteye.com/blog/2153709

使用火狐打开

D:\software\bin>cmd /c start firefox http://hw1287789

- ReplaceGoogleCDN:将 Google CDN 替换为国内的 Chrome 插件

justjavac

chromeGooglegoogle apichrome插件

Chrome Web Store 安装地址: https://chrome.google.com/webstore/detail/replace-google-cdn/kpampjmfiopfpkkepbllemkibefkiice

由于众所周知的原因,只需替换一个域名就可以继续使用Google提供的前端公共库了。 同样,通过script标记引用这些资源,让网站访问速度瞬间提速吧

- 进程VS.线程

m635674608

线程

资料来源:

http://www.liaoxuefeng.com/wiki/001374738125095c955c1e6d8bb493182103fac9270762a000/001397567993007df355a3394da48f0bf14960f0c78753f000 1、Apache最早就是采用多进程模式 2、IIS服务器默认采用多线程模式 3、多进程优缺点 优点:

多进程模式最大

- Linux下安装MemCached

字符串

memcached

前提准备:1. MemCached目前最新版本为:1.4.22,可以从官网下载到。2. MemCached依赖libevent,因此在安装MemCached之前需要先安装libevent。2.1 运行下面命令,查看系统是否已安装libevent。[root@SecurityCheck ~]# rpm -qa|grep libevent libevent-headers-1.4.13-4.el6.n

- java设计模式之--jdk动态代理(实现aop编程)

Supanccy2013

javaDAO设计模式AOP

与静态代理类对照的是动态代理类,动态代理类的字节码在程序运行时由Java反射机制动态生成,无需程序员手工编写它的源代码。动态代理类不仅简化了编程工作,而且提高了软件系统的可扩展性,因为Java 反射机制可以生成任意类型的动态代理类。java.lang.reflect 包中的Proxy类和InvocationHandler 接口提供了生成动态代理类的能力。

&

- Spring 4.2新特性-对java8默认方法(default method)定义Bean的支持

wiselyman

spring 4

2.1 默认方法(default method)

java8引入了一个default medthod;

用来扩展已有的接口,在对已有接口的使用不产生任何影响的情况下,添加扩展

使用default关键字

Spring 4.2支持加载在默认方法里声明的bean

2.2

将要被声明成bean的类

public class DemoService {