ARM Cortex A8之S5PV210

1. ARM Cortex A8寄存器组介绍

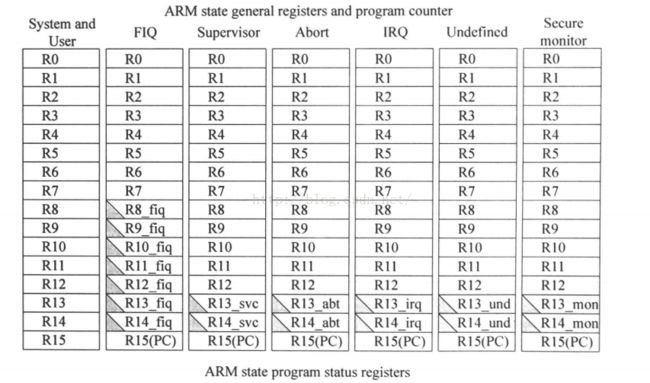

1.1 A8共有40个32位的寄存器

1>.32个通用的寄存器

2>.7个状态寄存器,1个CPSR,6个SPSR;

3>.1个PC(程序计数器)

ARM Cortex A8处理器一共有8种工作模式,每一种工作模式对应于不同的寄存器组。

图1 S5PV210寄存器

用户模式User:正常程序模式,大部分任务执行在 此模式下。

快速中断模式FIQ:用于高速数据传输和处理通道,高优先级中断产生时进入这种模式。

中断模式IRQ:通用中断处理,低优先级中断产生时进入这种模式。

管理模式SVC:操作系统使用的保护模式,复位或者软软中断时进入这一模式。

数据访问终止模式ABT:数据或者指令预取时进入此模式,用于虚拟存储和存储保护。

系统模式SYS:运行具有特权的操作系统任务。

未定义指令中止模式UND:当未定义指令执行时进入该模式,用于支持硬件协处理的软件仿真。

监控模式MON:用于安全模式和非安全模式之间进行切换。

对于S5PV210来说,有几个特殊的寄存器需要说明一下:

R13是堆栈指针寄存器,每种模式下都有自己的堆栈指针寄存器,也就是说每个模式下都有一个物理的寄存器R13,在系统启动时,需要初始化对应模式下的R13寄存器,即赋予对应的值。

R14是链接寄存器,存放子程序的返回地址。当执行BL或者BLX时,处理器自动地将返回地址保存在切换模式下的R14中,每个模式都有自己的R14.

R15称为程序计数器,记为PC,由于采用了流水线机制,PC的值不是指向当前正在执行的指令,而是指向当前指令的下两条指令的地址。

除第一个用户模式之外,其余模式都是特权模式。在特权模式下,程序可以访问所有的系统资源,包括被保护的资源,也可以任意地进行处理器模式的切换,处理器模式可以通过软件控制进行,也可以通过外部中断或者异常处理过程进行切换。

异常模式:包括快速中断模式FIQ,中断模式IRQ,系统模式SYS,数据访问中止模式ABT和未定义指令中止模式UND、监控模式共六种。当应用程序发生异常中断时,处理器进入异常模式。当异常发生时处理器进入相应的异常模式,处理完异常后会回到发生异常的地方继续执行。但是,如何计算从异常返回的地址呢??

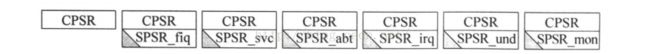

1.2 细说程序状态寄存器PSR

PSR包括了CPSR和SPSR,那什么是CPSR和SPSR?顾词思意,饮水思源,年轻人要有一颗探索世界的好奇心,我们很快就可以知道CPSR和SPSR分别是指当前程序状态寄存器和备份状态寄存器,SPSR为当前CPSR的一个备份,根据图1可知,SPSR寄存器有6个,常用来恢复异常处理完后的CPSR的值。这样就揭开了如何从异常处理返回地址的神秘面纱了。

图2 程序状态寄存器(PSR)格式

N、Z、C、V位是条件标志位,用来支持ARM指令集的条件执行功能。

J、T共同控制处理器的工作状态。S5PV210处理器有三种状态,三种状态分别是ARM状态, Thumb状态,ThumbEE状态;

T=J=0时,处于ARM状态,执行32位,字对齐的ARM指令集。

T=1,J=0时,处于Thumb状态,执行16位/32位,半字对齐的Thumb-2指令集。

T=J=1时,执行16、32位半字对齐的ThumbEE指令集,该指令集时Thumb-2的变种。

附:ARMv7架构处理器的数据类型

字节byte8位

半字halfword16位

字word32位

双字doubleWord64位

DNM,不可修改段。

Q,A,GE[3:0]、IT[7:2]大胆忽略。

E为大小端指示位,看后面介绍。

I、F分别是IRQ,FIQ禁止位,用于禁止或者使能IRQ,FIQ的中断功能。置1表示被禁止。

M[4:0]位处理器工作模式段

PSR的后八位[7:0]是控制位,他们的状态在异常出现时改变,当处理器工作于特权模式时,可通过改变此字段来改变处理器的状态。

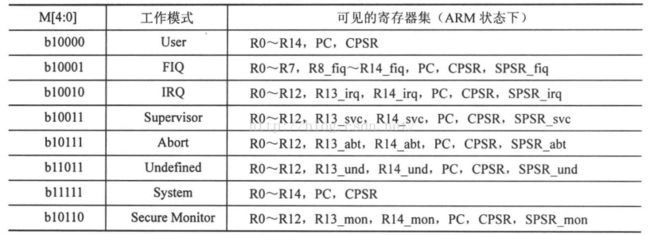

表1 模式控制位及可见寄存器集

注:只有在安全模式下才能直接对CPSR模式控制位进行修改以进入Monitor模式。

2.处理器状态与存储系统

存储系统可以使用地址映射,也可以使用高速缓存,写缓存以及虚拟内存以及I/O地址映射技术。其中一个很重要的时虚拟内存到物理空间的映射技术,当有了虚拟内存以后,每个进程运行在独立的虚拟内存中,老死不相往来,就好像Java的虚拟机一样。ARMv7架构采用了虚拟存储器系统结构(VMSA),具体来说就是采用了一个存储器管理单元(MMU)和系统控制协处理器CP15来支持对内存的访问和控制。MMU部件控制着地址转换,访问权限、存储属性以及校验等事务。它由系统控制协处理器控制。ARMv7—R则采用保护存储系统结构(PMSA),即基于称为存储保护单元MPU的部件来简化存储器的管理。

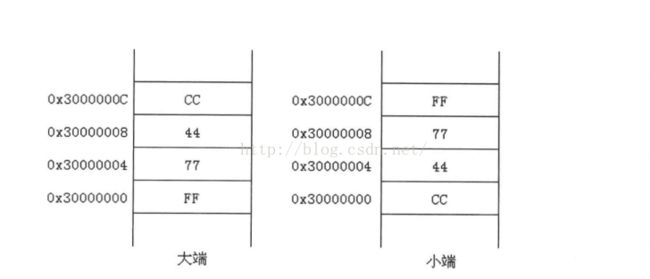

2.1 数据存储格式

大端格式:数据的高位存放在存储器的地位,数据的地位存在存储器的高位。

小端格式:跟大端格式相反,高-->高,低-->低。

讲那么多屁话还不如上图来的好。假如数据A=0xFF7744CC,内存中的起始地址是0x30000000

图3 数据存储格式

应该都明白了吧。

2.2 地址映射

S5PV210为32位系统,地址存储空间为0x00000000~0xFFFFFFFF,因此其寻址空间是4GB

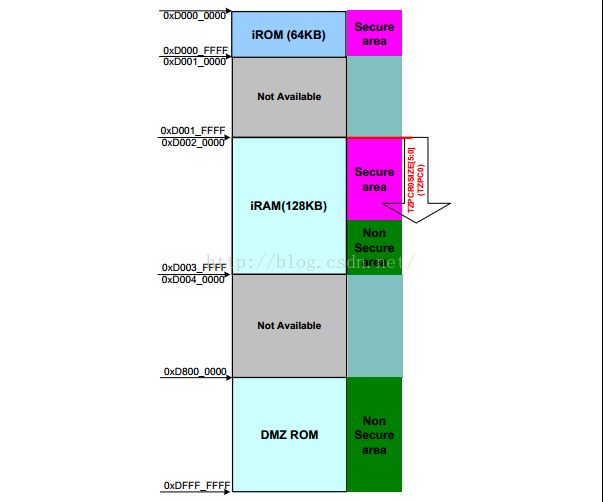

图4 存储器地址映射

图5 内部存储映射

如图可知,存储器地址空间包括特殊功能寄存器区,片内ROM/RAM、SROM、DROM以及系统启动区域。

表2 处理器功能部件地址空间

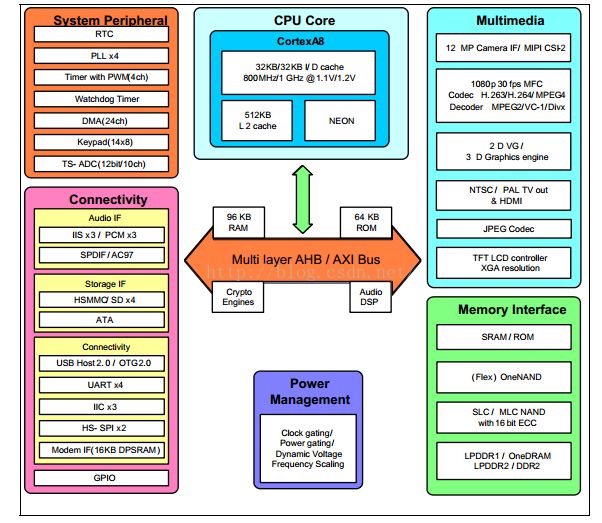

快退开,我要装逼了。听说上个彩图的人都很帅。。。。。。

图6 S5PV210整体框架图