- I.MX6ULL ARM裸机开发---C语言LED实验

一盆电子

ARM裸机开发armc语言驱动开发

一、引言 考虑到工作效率,嵌入式驱动开发很少用汇编,大部分是用C语言进行开发。 嵌入式驱动开发开始部分就可以用C语言吗? 当然不是!在开始部分用汇编来初始化一下C语言环境,比如初始化DDR、设置堆栈指针SP等等,当这些工作都做完以后就可以进入C语言环境,也就是运行C语言代码,一般都是进入main函数。有两部分文件需要完成: 1、汇编文件 汇编文件用来完成C语言环境搭建。 2、C语言文件

- Linux驱动开发 (IIC子系统)

嵌入式_笔记

Linux驱动linux驱动开发运维

1.IIC协议简介在之前的ARM裸机里面有介绍:ARM裸机-I2C通信协议是最常用的协议_一对多i2c-CSDN博客2.Linux的IIC子系统框架I2C主机驱动:I2C主机控制器的驱动,一般由SoC芯片厂商负责设计实现,用于控制II2C主机控制器发出时序信号。I2CCore:为上层提供统一的API接口和对其他模块进行注册和注销等管理等。I2C驱动和我们之前接触到的平台总线设备驱动非常类似,都有总

- ARM裸机-1.ARM体系结构和简单的汇编指令

poi_carefree

嵌入式嵌入式技术物联网arm汇编

一、一些专业术语ROM:readonlymemory只读存储器RAM:ramdomaccessmemory随机访问存储器IROM:internalrom内部ROM,指的是集成到SoC内部的ROMIRAM:internalram内部RAM,指的是集成到SoC内部的RAMDRAM:dynamicram动态RAMSRAM:staticram静态RAM二、ARM的编程模式和7种模式1、ARM有7个基本工作

- ARM裸机 - ARM体系架构

嵌入式_笔记

Linux驱动arm开发

一.常见处理器架构处理器架构指的是处理器的内部结构和功能,也就是处理器如何执行指令和数据的方式。不同的处理器架构有不同的指令集,也就是处理器能够理解和执行的基本操作。处理器架构对于处理器的性能、功耗、兼容性等方面有重要的影响。常见的架构有x86、ARM、RISC-V和MIPS。X86:这是英特尔和AMD的“专属”架构,主要用于PC、服务器和云计算领域,拥有高性能、高速度和高兼容性的优势。在PC市场

- 21. Ubuntu 交叉编译工具链安装

lljss2020

Linux

交叉编译器安装ARM裸机、Uboot移植、Linux移植这些都需要在Ubuntu下进行编译,编译就需要编译器,我们在第三章“LinuxC编程入门”里面已经讲解了如何在Liux进行C语言开发,里面使用GCC编译器进行代码编译,但是Ubuntu自带的gcc编译器是针对X86架构的!而我们现在要编译的是ARM架构的代码,所以我们需要一个在X86架构的PC上运行,可以编译ARM架构代码的GCC编译器,这个

- Linux-ARM裸机(十二)-DDR3-外接RAM内存芯片

xiaoliu_henniu

linuxarm开发ubuntu单片机

I.MX6U-ALPHA开发板上带有一个256MB/512MB的DDR3内存芯片,一般Cortex-A芯片自带RAM很小,比如I.MX6U只有128KB的OCRAM。若要运行Linux的话完全不够用,所以必须外扩一片RAM芯片,I.MX6U支持LPDDR2、LPDDR3/DDR3,I.MX6U-ALPHA开发板上使用的是DDR3,本篇记录学习如何驱动I.MX6U-ALPHA开发板上的这片DDR3。

- Linux-ARM裸机(八)-中断(下半)

xiaoliu_henniu

linuxarm开发运维

通用中断驱动编写做Linux开发时候要把Ubuntu的ip地址设置为静态,防止发生变化。移植SDK包中断相关文件将SDK包中的文件core_ca7.h拷贝到工程中的“imx6ul”文件夹中。裁剪修改的内容参考试验“9_int”中core_ca7.h进行修改(直接使用正点提供的修改好的即可,copy过来直接用)。主要留下和GIC相关的内容,重点需要core_ca7.h中的10个API函数,这10个函

- Linux-ARM裸机(九)-EPIT定时器

xiaoliu_henniu

arm开发单片机ubuntulinux

定时器是最常用的外设,常要用定时器完成精准的定时,I.MX6U提供了多种硬件定时器。本篇记录了学习如何配置EPIT定时器,使其按照给定的时间,周期性的产生定时器中断,在定时器中断里面可以进行其他操作,比如:点灯,开关蜂鸣器等等。EPITEPIT全称:EnhancedPeriodicInterruptTimer,增强型周期中断定时器,它主要用来完成周期性中断定时。在STM32里定时器还有其它功能,比

- Linux-ARM裸机(十)-GPT定时器

xiaoliu_henniu

gptarm开发单片机ubuntulinux

前面的实验中我们使用循环来实现延时函数,但使用循环实现的延时函数不准确,误差会很大。某些对时序要求严格的场合要使用硬件定时器,延时函数越精确越好。本篇学习如何使用硬件定时器实现高精度延时。GPT定时器GPT定时器简介我们在使用STM32时可使用SYSTICK(系统滴答定时器)来实现高精度延时。本章我们使用I.MX6U的GPT定时器来实现高精度延时,GPT定时器全称为GeneralPurposeTi

- 【嵌入式Linux_ARM裸机】---串口通信的实现

Mr_WangAndy

嵌入式Linux_ARM裸机串口通信概念串口通信原理同步异步起始位停止位数据位校验位通信电平信号

1.通信的三个概念通信的过程可以分为三个步骤:首先,发送方按照固定编码格式进行编码;其次,将编码后的信息发送到传输介质上;最后,接收方收到后进行解码得到有效信息。同步和异步:发送方和接收方的时钟节拍一致叫同步,否则叫异步。如下雨所示,最上边的一根线就是同步信号线,发送端和接收端在相同的节拍下工作。同步使用场景:当发送端和接收端频率固定时,使用同步信号。可以想象接收端一直在接收发送端的消息。异步场景

- Linux-ARM裸机(十一)-UART串口通信

xiaoliu_henniu

linuxarm开发运维

无论单片机开发还是嵌入式Linux开发,串口都是最常用到的外设。可通过串口将开发板与电脑相连,然后在电脑上通过串口调试助手来调试程序。还有很多的模块,比如蓝牙、GPS、GPRS等都使用的串口来与主控进行通信的,在嵌入式Linux中一般使用串口作为控制台。本篇记录了如何驱动I.MX6U的串口,并使用串口和电脑进行通信。UART简介1、UART通信格式串口全称叫做串行接口,通常也叫COM接口,串行接口

- Linux内核中断

满山的猴子我的腚最红

ARM开发linux单片机运维驱动开发嵌入式硬件

Linux内核中断ARM里当按下按键的时候,他首先会执行汇编文件start.s里面的异常向量表里面的irq,在irq里面进行一些操作。再跳转到C的do_irq();进行操作:1)判断中断的序号;2)处理中断;3)清除中断;Linux内核实现和ARM裸机实现中断的原理是一样的。内核:当按键按下后依然到异常向量表,再到handler_irq函数(写死的),在handler_irq里面定义了一个数组,数

- ubuntu linux开发环境搭建

try_HH

LINUXlinuxubuntu运维单片机mcu服务器fpga开发

Ubuntulinux开发环境搭建一、概述此篇记录ubuntu系统下开发环境搭建,包含ARM交叉编译工具链安装、TFTP环境搭建、NFS环境搭建,以及VSCODE安装,ubuntu版本为16.04.二、安装交叉编译工具链2.1交叉编译工具链说明ARM裸机、Uboot移植、Linux移植都需要在ubuntu下进行编译,编译需要编译器,ubuntu自带的gcc编译器是针对X86架构的,而我们需要编译的

- 驱动开发-1

满山的猴子我的腚最红

ARM开发驱动开发arm开发

一、驱动课程大纲内核模块字符设备驱动中断二、ARM裸机代码和驱动有什么区别?1、共同点:都能够操作硬件2、不同点:1)裸机就是用C语言给对应的寄存器里面写值,驱动是按照一定的套路往寄存器里面写值2)arm裸机单独编译单独执行,驱动依赖内核编译,依赖内核执行(根据内核指定好的架构和配置去实现)3)arm裸机同时只能执行一份代码,驱动可以同时执行多分代码(且当要操作串口的时候,内核写的一部分代码咱们程

- ARM裸机-20(I2C通信)

ant-small

ARMarm开发

1、什么是I2C通信1.1、物理接口:SCL+SDA(1)、SCL(serialclock):时钟线,传输CLK信号,一般是I2C主设备向从设备提供时钟的通道。(2)、SDA(serialdata):数据线,通信数据都通过SDA线传输。1.2、通信特征:串行、同步、非差分、低速率(1)、I2C属于串行通信,所有的数据以位为单位在SDA线上串行传输。(2)、同步通信就是通信双方工作在同一个时钟下,一

- ARM裸机-21(ADC)

ant-small

ARMarm开发

1、ADC的引入1.1、什么是ADC(1)、ADC:analogdigitalconverter,AD转换,模数转换(也就是模拟转数字)。(2)、CPU本身是数字的,而外部世界变量(如电压、温度、高度、压力···)都是模拟的,所以需要用CPU来处理这些外部的模拟变量的时候就需要做AD转换。1.2、为什么需要ADC(1)、为了用数字技术来处理外部的模拟物理量。1.3、关于模拟量和数字量(1)、模拟的

- MX6ULL学习笔记 (一)交叉工具链的安装

ODF..

mx6ull学习笔记

前言:ARM裸机、Uboot移植、Linux移植这些都需要在Ubuntu下进行编译,编译就需要编译器,Ubuntu自带的gcc编译器是针对X86架构的!而我们现在要编译的是ARM架构的代码,因为我们编译的代码是需要烧写到ARM板子上的,所以我们需要一个在X86架构的PC上运行,可以编译ARM架构代码的GCC编译器,这个编译器就叫做交叉编译器。一、编译器的获取:交叉编译器有很多种,我们使用Linar

- ARM开发环境搭建

IsQiya

安装教程armstm32pytorch

1.下载E:\ARM开发\工具软件\ARM裸机开发工具\Yagarto工具包路径下两个程序2.下载E:\ARM开发\工具软件\USB转串口驱动\CH3403.下载E:\ARM开发\工具软件\ARM裸机开发工具\JRE4.打开设备管理器->右键->更新5.6.选择E:\ARM开发\工具软件\ARM裸机开发工具\DRIVER目录下的(注意:此操作win7环境下,win7以上还要有点其他步骤)选择好就点

- ARM裸机-17(定时器、看门狗)

ant-small

ARMarm开发

1、什么是定时器(Timer)1.1、定时器是SoC中常见外设(1)、定时器与计数器。计数器是用来计数的(每隔一个固定时间会计一个数):因为计数器的计数时间周期是固定的,因此到了一定时间只要用计数值x计数时间周期,就能得到一个时间段,这个时间段就是我们定的时间(这就是定时器了)。(2)、定时器/计数器作为SoC的外设,主要用来实现定时执行代码的功能。定时器相对于SoC来说,就好象闹钟相对于人来说意

- ARM裸机-18(SD卡启动)

ant-small

ARMarm开发

1、主流的外存设备介绍内存和外存的区别:一般是把这种RAM(randomaccessmemory,随机访问存储器,特点是任意字节读写,掉电丢失)叫内存,把ROM(readonlymemory,只读存储器,类似于Flash、SD卡之类的,用来存储东西,掉电不丢失,不能随机地址访问,只能以块为单位来访问)叫外存。1.1、软盘、硬盘、光盘、CD、磁带(1)、存储原理大部分为磁存储,缺点是读写速度、可靠性

- ARM裸机-16(按键和中断)

ant-small

ARMarm开发

1、什么是按键1.1、按键的物理特性(1)、平时没人按的时候,弹簧把按键按钮弹开。此时内部断开的。(2)、有人按下的时候,手的力量克服弹簧的弹力,将按钮按下,此时内部保持接通(闭合)状态,如果手拿开,则弹簧作用下按钮又弹开,同时内部又断开。(3)、一般的按键都有4个引脚,这4个引脚成2对:其中一对是常开触点(像上面描述的不按则断开,按下则闭合);一对是常闭触点(平时不按时是闭合的,按下后是断开的)

- ARM裸机-19(NandFlash和iNand)

ant-small

ARMarm开发

1、NandFlash的接口1.1、Nand的型号与命名(1)、Nand的型号命名都有含义,就拿K9F2G08来示例分析一下:K9F表示是三星公司的NandFlash系列。2G表示Nand的大小是2Gbit(256MB)。08表示Nand是8位的(8位就是数据线有8根)。(2)、Nand命名中可以看出:厂家、系列型号、容量大小、数据位数。1.2、Nand的数据位(1)、Nand有8位数据位的,有1

- ARM裸机-9.SD卡启动详解

poi_carefree

嵌入式

1.主流的外存设备介绍内存和外存的区别:一般是把这种RAM(randomaccessmemory,随机访问存储器,特点是任意字节读写,掉电丢失)叫内存,把ROM(readonlymemory,只读存储器,类似于FlashSD卡之类的,用来存储东西,掉电不丢失,不能随机地址访问,只能以块为单位来访问)叫外存1.1、软盘、硬盘、光盘、CD、磁带(1)存储原理大部分为磁存储,缺点是读写速度、可靠性等。优

- Linux_VMware 软件安装与虚拟机

light_2025

Linuxlinux单片机嵌入式硬件stm32

从这里开始,我们就踏上了学习Linux的路程。长路漫漫亦灿灿,祝我也祝所有看到这篇文章的朋友!!!参考书目:【正点原子】I.MX6U嵌入式Linux驱动开发指南V1.81/ARM裸机与嵌入式Linux驱动开发1.为什么需要虚拟机?之前学习过的不管是51单片机还是STM32单片机都是在Windows系统下进行的,使用MDK这样的集成IDE,但是嵌入式Linux驱动开发需要的主机是Linux平台的,所

- arm裸机测试led灯亮灭、风扇、马达等

路过的坏人

arm开发

汇编代码:.text.global_start_start:@RCC使能GPIOERCC_MP_AHB4ENSETR[4]->1LDRR0,=0X50000A28LDRR1,[R0]ORRR1,R1,#(0X301LDRR0,=0X50006000LDRR1,[R0]@10BICR1,R1,#(0X301LDRR0,=0X50007000LDRR1,[R0]@10BICR1,R1,#(0X30LD

- linux驱动开发篇(一)—— Linux 内核模块介绍

Aladdin_KK

linuxlinux驱动开发arm开发

linux系列目录:linux基础篇(一)——GCC和Makefile编译过程linux基础篇(二)——静态和动态链接ARM裸机篇(一)——i.MX6ULL介绍ARM裸机篇(二)——i.MX6ULL启动过程ARM裸机篇(三)——i.MX6ULL第一个裸机程序ARM裸机篇(四)——重定位和地址无关码ARM裸机篇(五)——异常和中断linux系统移植篇(一)——linux系统组成linux系统移植篇(

- Linux-ARM裸机(一)-搭建开发环境

xiaoliu_henniu

arm开发linux

开发环境搭建由于本人前期课程看的正点原子的视频,因此,开发环境是用的正点的那一套。在Ubuntu下进行Cortex-A(I.MX6U)开发,安装一些软件就是开发环境搭建。前期尽量跟随自己看的课程配置对应开发环境,学习起来比较舒服,但用的软件的功能呢大体上都是类似的,后期可以根据自己喜好尝试不同的软件。Ubuntu和Windows文件互传在开发的过程中会频繁的在Windows和Ubuntu下进行文件

- linux 手记

冉若愚

linuxmakefile嵌入式多线程buildstruct

酝酿许久的手记终于面世了,希望高手多多指点。从7月到现在,我参与的产品的研发,也算告一段落,明天就是成都的医博会了,这几个月慢慢啃出来的东西,要好好的总结一下,大学的时候,玩的是单片机,arm裸机,对于系统有所了解,做过一些小实验,但是没有系统的学习,如今做的事情,让我对嵌入式linux的认识也更正了许多。在此做个手记。以前一直认为,要做linux,就得安装真机的linux系统,就像“不下水的人,

- linux驱动开发篇(二)—— 字符设备驱动框架

Aladdin_KK

linuxlinux驱动开发arm开发

linux系列目录:linux基础篇(一)——GCC和Makefile编译过程linux基础篇(二)——静态和动态链接ARM裸机篇(一)——i.MX6ULL介绍ARM裸机篇(二)——i.MX6ULL启动过程ARM裸机篇(三)——i.MX6ULL第一个裸机程序ARM裸机篇(四)——重定位和地址无关码ARM裸机篇(五)——异常和中断linux系统移植篇(一)——linux系统组成linux系统移植篇(

- 【ARM裸机】ARM入门

m0_63077733

ARM裸机arm开发

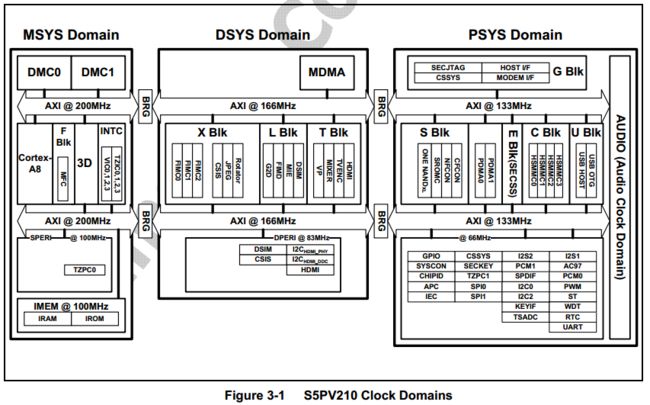

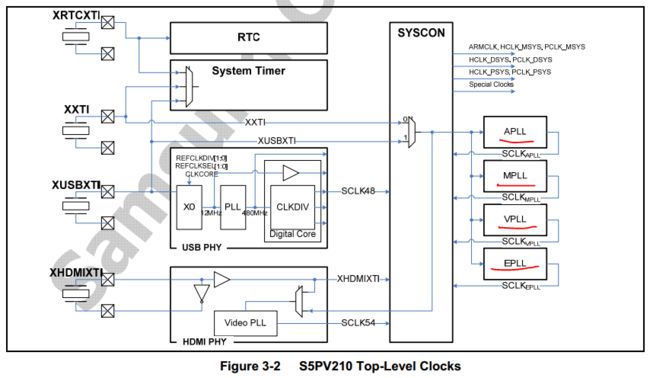

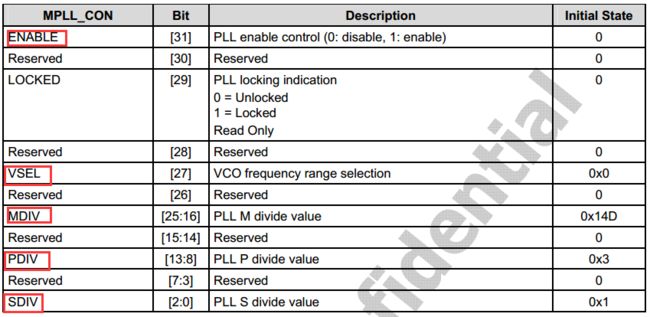

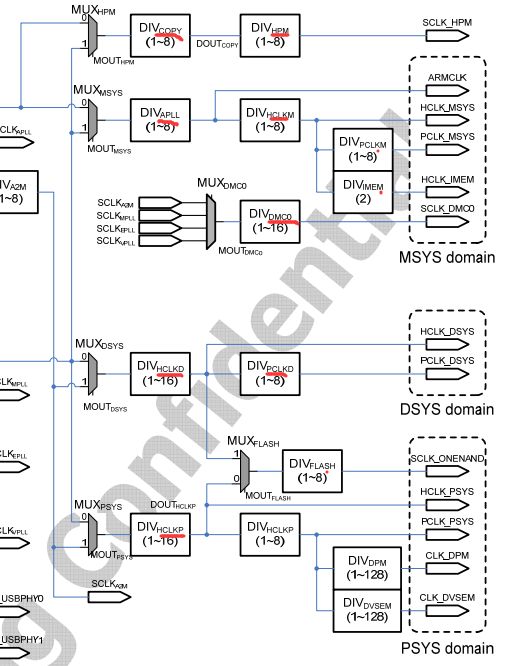

1.ARM成长史2.ARM的商业模式和生态系统ARM只设计CPU,但是不生产CPU3.为什么使用三星:S5PV2104.各种版本号0.ARM和CortexCortex就是ARM公司一个系列处理器的名称。比如英特尔旗下处理器有酷睿,奔腾,赛扬。ARM在最初的处理器型号都用数字命名,最后一个是ARM11系列,在应用ARMv7架构后,推出了Cortex这一系列,老式的则命名为Classic系列。内核co

- java解析APK

3213213333332132

javaapklinux解析APK

解析apk有两种方法

1、结合安卓提供apktool工具,用java执行cmd解析命令获取apk信息

2、利用相关jar包里的集成方法解析apk

这里只给出第二种方法,因为第一种方法在linux服务器下会出现不在控制范围之内的结果。

public class ApkUtil

{

/**

* 日志对象

*/

private static Logger

- nginx自定义ip访问N种方法

ronin47

nginx 禁止ip访问

因业务需要,禁止一部分内网访问接口, 由于前端架了F5,直接用deny或allow是不行的,这是因为直接获取的前端F5的地址。

所以开始思考有哪些主案可以实现这样的需求,目前可实施的是三种:

一:把ip段放在redis里,写一段lua

二:利用geo传递变量,写一段

- mysql timestamp类型字段的CURRENT_TIMESTAMP与ON UPDATE CURRENT_TIMESTAMP属性

dcj3sjt126com

mysql

timestamp有两个属性,分别是CURRENT_TIMESTAMP 和ON UPDATE CURRENT_TIMESTAMP两种,使用情况分别如下:

1.

CURRENT_TIMESTAMP

当要向数据库执行insert操作时,如果有个timestamp字段属性设为

CURRENT_TIMESTAMP,则无论这

- struts2+spring+hibernate分页显示

171815164

Hibernate

分页显示一直是web开发中一大烦琐的难题,传统的网页设计只在一个JSP或者ASP页面中书写所有关于数据库操作的代码,那样做分页可能简单一点,但当把网站分层开发后,分页就比较困难了,下面是我做Spring+Hibernate+Struts2项目时设计的分页代码,与大家分享交流。

1、DAO层接口的设计,在MemberDao接口中定义了如下两个方法:

public in

- 构建自己的Wrapper应用

g21121

rap

我们已经了解Wrapper的目录结构,下面可是正式利用Wrapper来包装我们自己的应用,这里假设Wrapper的安装目录为:/usr/local/wrapper。

首先,创建项目应用

&nb

- [简单]工作记录_多线程相关

53873039oycg

多线程

最近遇到多线程的问题,原来使用异步请求多个接口(n*3次请求) 方案一 使用多线程一次返回数据,最开始是使用5个线程,一个线程顺序请求3个接口,超时终止返回 缺点 测试发现必须3个接

- 调试jdk中的源码,查看jdk局部变量

程序员是怎么炼成的

jdk 源码

转自:http://www.douban.com/note/211369821/

学习jdk源码时使用--

学习java最好的办法就是看jdk源代码,面对浩瀚的jdk(光源码就有40M多,比一个大型网站的源码都多)从何入手呢,要是能单步调试跟进到jdk源码里并且能查看其中的局部变量最好了。

可惜的是sun提供的jdk并不能查看运行中的局部变量

- Oracle RAC Failover 详解

aijuans

oracle

Oracle RAC 同时具备HA(High Availiablity) 和LB(LoadBalance). 而其高可用性的基础就是Failover(故障转移). 它指集群中任何一个节点的故障都不会影响用户的使用,连接到故障节点的用户会被自动转移到健康节点,从用户感受而言, 是感觉不到这种切换。

Oracle 10g RAC 的Failover 可以分为3种:

1. Client-Si

- form表单提交数据编码方式及tomcat的接受编码方式

antonyup_2006

JavaScripttomcat浏览器互联网servlet

原帖地址:http://www.iteye.com/topic/266705

form有2中方法把数据提交给服务器,get和post,分别说下吧。

(一)get提交

1.首先说下客户端(浏览器)的form表单用get方法是如何将数据编码后提交给服务器端的吧。

对于get方法来说,都是把数据串联在请求的url后面作为参数,如:http://localhost:

- JS初学者必知的基础

百合不是茶

js函数js入门基础

JavaScript是网页的交互语言,实现网页的各种效果,

JavaScript 是世界上最流行的脚本语言。

JavaScript 是属于 web 的语言,它适用于 PC、笔记本电脑、平板电脑和移动电话。

JavaScript 被设计为向 HTML 页面增加交互性。

许多 HTML 开发者都不是程序员,但是 JavaScript 却拥有非常简单的语法。几乎每个人都有能力将小的

- iBatis的分页分析与详解

bijian1013

javaibatis

分页是操作数据库型系统常遇到的问题。分页实现方法很多,但效率的差异就很大了。iBatis是通过什么方式来实现这个分页的了。查看它的实现部分,发现返回的PaginatedList实际上是个接口,实现这个接口的是PaginatedDataList类的对象,查看PaginatedDataList类发现,每次翻页的时候最

- 精通Oracle10编程SQL(15)使用对象类型

bijian1013

oracle数据库plsql

/*

*使用对象类型

*/

--建立和使用简单对象类型

--对象类型包括对象类型规范和对象类型体两部分。

--建立和使用不包含任何方法的对象类型

CREATE OR REPLACE TYPE person_typ1 as OBJECT(

name varchar2(10),gender varchar2(4),birthdate date

);

drop type p

- 【Linux命令二】文本处理命令awk

bit1129

linux命令

awk是Linux用来进行文本处理的命令,在日常工作中,广泛应用于日志分析。awk是一门解释型编程语言,包含变量,数组,循环控制结构,条件控制结构等。它的语法采用类C语言的语法。

awk命令用来做什么?

1.awk适用于具有一定结构的文本行,对其中的列进行提取信息

2.awk可以把当前正在处理的文本行提交给Linux的其它命令处理,然后把直接结构返回给awk

3.awk实际工

- JAVA(ssh2框架)+Flex实现权限控制方案分析

白糖_

java

目前项目使用的是Struts2+Hibernate+Spring的架构模式,目前已经有一套针对SSH2的权限系统,运行良好。但是项目有了新需求:在目前系统的基础上使用Flex逐步取代JSP,在取代JSP过程中可能存在Flex与JSP并存的情况,所以权限系统需要进行修改。

【SSH2权限系统的实现机制】

权限控制分为页面和后台两块:不同类型用户的帐号分配的访问权限是不同的,用户使

- angular.forEach

boyitech

AngularJSAngularJS APIangular.forEach

angular.forEach 描述: 循环对obj对象的每个元素调用iterator, obj对象可以是一个Object或一个Array. Iterator函数调用方法: iterator(value, key, obj), 其中obj是被迭代对象,key是obj的property key或者是数组的index,value就是相应的值啦. (此函数不能够迭代继承的属性.)

- java-谷歌面试题-给定一个排序数组,如何构造一个二叉排序树

bylijinnan

二叉排序树

import java.util.LinkedList;

public class CreateBSTfromSortedArray {

/**

* 题目:给定一个排序数组,如何构造一个二叉排序树

* 递归

*/

public static void main(String[] args) {

int[] data = { 1, 2, 3, 4,

- action执行2次

Chen.H

JavaScriptjspXHTMLcssWebwork

xwork 写道 <action name="userTypeAction"

class="com.ekangcount.website.system.view.action.UserTypeAction">

<result name="ssss" type="dispatcher">

- [时空与能量]逆转时空需要消耗大量能源

comsci

能源

无论如何,人类始终都想摆脱时间和空间的限制....但是受到质量与能量关系的限制,我们人类在目前和今后很长一段时间内,都无法获得大量廉价的能源来进行时空跨越.....

在进行时空穿梭的实验中,消耗超大规模的能源是必然

- oracle的正则表达式(regular expression)详细介绍

daizj

oracle正则表达式

正则表达式是很多编程语言中都有的。可惜oracle8i、oracle9i中一直迟迟不肯加入,好在oracle10g中终于增加了期盼已久的正则表达式功能。你可以在oracle10g中使用正则表达式肆意地匹配你想匹配的任何字符串了。

正则表达式中常用到的元数据(metacharacter)如下:

^ 匹配字符串的开头位置。

$ 匹配支付传的结尾位置。

*

- 报表工具与报表性能的关系

datamachine

报表工具birt报表性能润乾报表

在选择报表工具时,性能一直是用户关心的指标,但是,报表工具的性能和整个报表系统的性能有多大关系呢?

要回答这个问题,首先要分析一下报表的处理过程包含哪些环节,哪些环节容易出现性能瓶颈,如何优化这些环节。

一、报表处理的一般过程分析

1、用户选择报表输入参数后,报表引擎会根据报表模板和输入参数来解析报表,并将数据计算和读取请求以SQL的方式发送给数据库。

2、

- 初一上学期难记忆单词背诵第一课

dcj3sjt126com

wordenglish

what 什么

your 你

name 名字

my 我的

am 是

one 一

two 二

three 三

four 四

five 五

class 班级,课

six 六

seven 七

eight 八

nince 九

ten 十

zero 零

how 怎样

old 老的

eleven 十一

twelve 十二

thirteen

- 我学过和准备学的各种技术

dcj3sjt126com

技术

语言VB https://msdn.microsoft.com/zh-cn/library/2x7h1hfk.aspxJava http://docs.oracle.com/javase/8/C# https://msdn.microsoft.com/library/vstudioPHP http://php.net/manual/en/Html

- struts2中token防止重复提交表单

蕃薯耀

重复提交表单struts2中token

struts2中token防止重复提交表单

>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>

蕃薯耀 2015年7月12日 11:52:32 星期日

ht

- 线性查找二维数组

hao3100590

二维数组

1.算法描述

有序(行有序,列有序,且每行从左至右递增,列从上至下递增)二维数组查找,要求复杂度O(n)

2.使用到的相关知识:

结构体定义和使用,二维数组传递(http://blog.csdn.net/yzhhmhm/article/details/2045816)

3.使用数组名传递

这个的不便之处很明显,一旦确定就是不能设置列值

//使

- spring security 3中推荐使用BCrypt算法加密密码

jackyrong

Spring Security

spring security 3中推荐使用BCrypt算法加密密码了,以前使用的是md5,

Md5PasswordEncoder 和 ShaPasswordEncoder,现在不推荐了,推荐用bcrpt

Bcrpt中的salt可以是随机的,比如:

int i = 0;

while (i < 10) {

String password = "1234

- 学习编程并不难,做到以下几点即可!

lampcy

javahtml编程语言

不论你是想自己设计游戏,还是开发iPhone或安卓手机上的应用,还是仅仅为了娱乐,学习编程语言都是一条必经之路。编程语言种类繁多,用途各 异,然而一旦掌握其中之一,其他的也就迎刃而解。作为初学者,你可能要先从Java或HTML开始学,一旦掌握了一门编程语言,你就发挥无穷的想象,开发 各种神奇的软件啦。

1、确定目标

学习编程语言既充满乐趣,又充满挑战。有些花费多年时间学习一门编程语言的大学生到

- 架构师之mysql----------------用group+inner join,left join ,right join 查重复数据(替代in)

nannan408

right join

1.前言。

如题。

2.代码

(1)单表查重复数据,根据a分组

SELECT m.a,m.b, INNER JOIN (select a,b,COUNT(*) AS rank FROM test.`A` A GROUP BY a HAVING rank>1 )k ON m.a=k.a

(2)多表查询 ,

使用改为le

- jQuery选择器小结 VS 节点查找(附css的一些东西)

Everyday都不同

jquerycssname选择器追加元素查找节点

最近做前端页面,频繁用到一些jQuery的选择器,所以特意来总结一下:

测试页面:

<html>

<head>

<script src="jquery-1.7.2.min.js"></script>

<script>

/*$(function() {

$(documen

- 关于EXT

tntxia

ext

ExtJS是一个很不错的Ajax框架,可以用来开发带有华丽外观的富客户端应用,使得我们的b/s应用更加具有活力及生命力。ExtJS是一个用 javascript编写,与后台技术无关的前端ajax框架。因此,可以把ExtJS用在.Net、Java、Php等各种开发语言开发的应用中。

ExtJs最开始基于YUI技术,由开发人员Jack

- 一个MIT计算机博士对数学的思考

xjnine

Math

在过去的一年中,我一直在数学的海洋中游荡,research进展不多,对于数学世界的阅历算是有了一些长进。为什么要深入数学的世界?作为计算机的学生,我没有任何企图要成为一个数学家。我学习数学的目的,是要想爬上巨人的肩膀,希望站在更高的高度,能把我自己研究的东西看得更深广一些。说起来,我在刚来这个学校的时候,并没有预料到我将会有一个深入数学的旅程。我的导师最初希望我去做的题目,是对appe