Verilog专题(一)Vectors

对于verilog的学习,大概分两步,第一步先看书了解基本语法,语法书基本上大同小异,看一本就好了;第二步就是编程实现了,这里推荐一个比较好的实践网站HDLBits:https://hdlbits.01xz.net/wiki/Main_Page

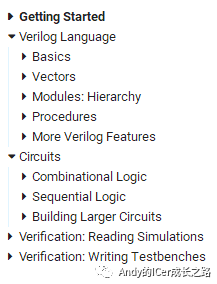

上面题型非常丰富,基本涵盖了verilog语法基础以及基本电路,下图是HDLBits的目录。

后面会针对这个网站上面的题目做一个专题,记录一些我觉得有价值的题目,希望通过题目可以对verilog更加熟练。

第一个专题介绍Vectors,关于对向量进行操作最精髓的应该就是拼接符{}了,下面主要介绍几道拼接符的题目。

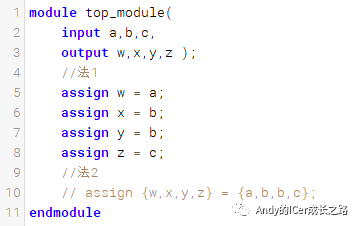

题目1

1、根据top_module,我们要将output和input连接起来,有两种办法,直接assign连线为法1,用拼接符{}为法2,代码如下。

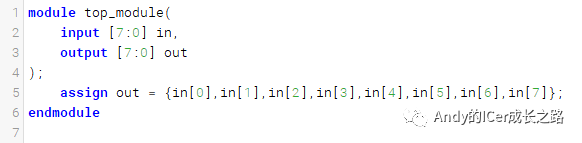

题目二

2、第二题与第一题的法二相似,有代码就不解释了。

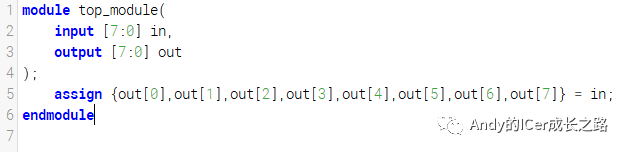

题目三

3、第三题的题目是将一个8位的输入倒过来输出(即in[0]等于out[7],in[1]等于out[6],如此类推),下面介绍三种方法。

法1:用拼接符的方法进行倒转

法2:用for循环(注意:在always块中赋值号左边的信号要为reg型,但是这里的编译器能编译通过,可能与编译器的版本有关,一般always@(*)综合为组合逻辑电路,加clk的话always@(posedge clk)为时序电路)

法3:Generate块循环用于实例化“某些东西”(与过程循环不同,它不描述动作)。这些“东西”可以是assign语句、模块实例化、网络/变量声明和过程块。可以将生成块视为一种预处理形式,以生成更多代码,然后通过逻辑合成器运行该代码。在这个示例中,generate-for循环首先在编译时创建8个assign语句,然后将其合成。

题目四

4、第四题是一个关于sign-extending(符号位扩展)的问题。低位宽转化为高位宽的时候分正数扩展和负数扩展两种情况。例如正数4'b0101 (5) 扩展为8位,就是变成 8'b00000101 (5);负数4'b1101 (-3) 扩展为8位,变成 8'b11111101 (-3)。简单来说,即复制符号位作为扩展位,如要将8位扩展为32位,代码如下。

题目五

5、第五题题目和解决方法如图所示。

总结

综上所述,什么情况下可以使用拼接符来让vectors更加丝滑柔顺地结合呢?

1、输入输出可以组合之后直接连线的情况,如题目1、题目2和题目5,都是将输入组合成输出。

2、输入的顺序进行变换之后再输出的情况,如题目3。eg:

// Swap two bytes

assign {out[7:0], out[15:8]} = in;

assign out[15:0] = {in[7:0], in[15:8]};

3、符号位扩展问题,如题目4。

eg:

{5{1'b1}} // 5'b11111 (or 5'd31 or 5'h1f)

{2{a,b,c}} // {a,b,c,a,b,c}

{3'd5, {2{3'd6}}} // 9'b101_110_110.

微信公众号

建立了一个微信公众号“Andy的ICer之路”,此公众号主要分享数字IC相关的学习经验(后期打算与csdn同步更新),做公众号的目的就是记录自己的学习过程,很多东西回过头来可能就忘记了,为了记住知识和分享知识,希望自己可以保持更新,有兴趣的朋友可以关注一下!

![]()