移植Uboot2017到TINY4412

梦想还是要有的,万一实现了

移植相关

硬件:

-核心板:Tiny4412 - 1412

-底板: Tiny4412/Super4412SDK 1506

软件:

-移植uboot版本: u-boot-2017.05.tar.bz2

-工具链:arm-Linux-gcc 4.5.1 工具链就不介绍如何安装了。

接着上一节内容,前一节中已经实现了调试LED的点亮,接下来对开发板做一些初始化。

Exynos 4412时钟体系

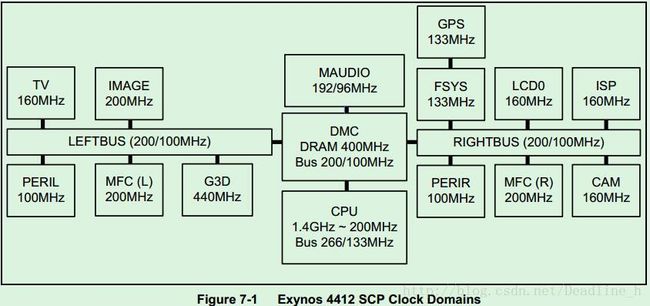

不同外设的工作频率不一样,所以需要为不同的外设设置不同的工作频率。

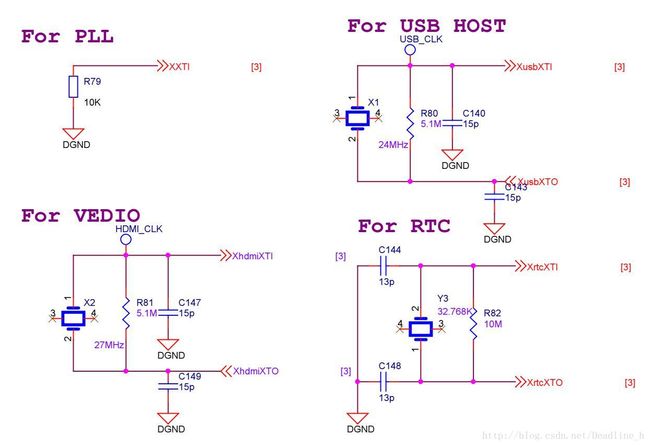

信号源

根据芯片手册文档描述以及Exynos4412时钟产生框图可知,Exynos4412的外部时钟源主要为:

-XRTC:实时时钟源

-XXTI:用于向系统提供时钟

-XusbXTI:用于向系统提供时钟

-XXTI27:用于给Video提供时钟。

根据时钟产生框图可知,系统时钟源选择根据XOM【0】的电平决定。TINY4412该引脚接高电平,所以选择了XusbXTI引脚作为系统时钟时钟输入源。然后通过PLL(phase lock loop锁相环,用于倍频)将外部时钟时钟频率进行倍频,然后通过MUX(multiplexer多路复用器)对时钟来源进行选择,然后通过DIV(divider分频器)对频率进行分频,为不同的系统提供时钟。

由TINY4412原理图可知,芯片外部系统时钟源接了24MHZ的晶振。

exynos 4412 PLL介绍

Exynos4412 有 4 个 PLL: APLL、 MPLL、 EPLL 和 VPLL;

① APLL: 用于 CPU_BLK,也可以给 DMC_BLK、LEFTBUS_BLK、RIGHTBUS_BLK

和 CMU_TOP 提供时钟。

② MPLL: 用于 DMC_BLK、 LEFTBUS_BLK、 RIGHTBUS_BLK 和 CMU_TOP

③ EPLL: 主要给音频模块提供时钟

④ VPLL: 主要给视频系统提供 54MHz 时钟, 给 G3D(3D 图形加速器)提供时钟。

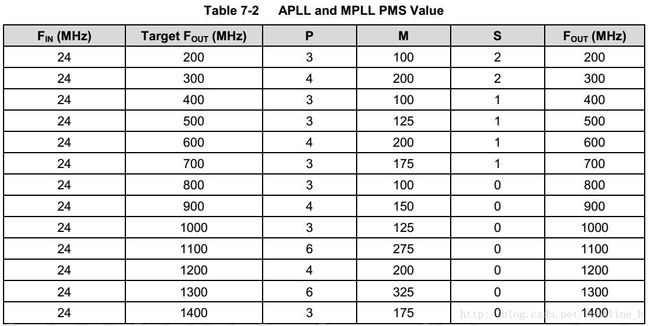

PLL配置

APPL主要给系统时钟提供时钟,根据公式以及P、M、S参数限制,可以计算出合适的值。当然芯片手册有提供推荐值。我们依据芯片手册进行设置即可。

TINY4412的输入频率为24MHZ,我们要是系统跑到1.4GHZ,则设置p=3,M=175,S=0即可。

1400 = 175 * 24 / (3 * 2^0)

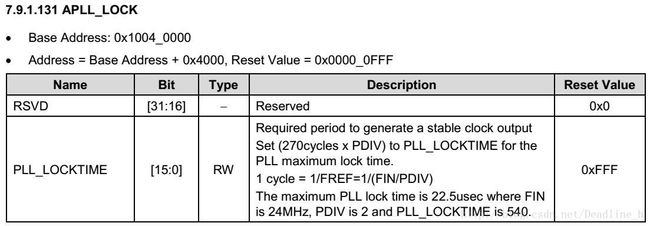

PLL锁定定时间

锁相环设置之后,并不能马上输出正确时钟,需要一点时间。所以还需要设置锁定时间。

根据芯片手册,如果设置系统时钟频率为1400MHZ,P= 3,APLL的锁定时间值设为810(270*3)。

MUX时钟选择器设置

根据时钟产生框图,找到相应的寄存器,然后根据需求配置。

DIV分频器设置

由上图可知各个模块需要的工作频率,根据自己设置的PLL输出频率,便可求得分频器的值。

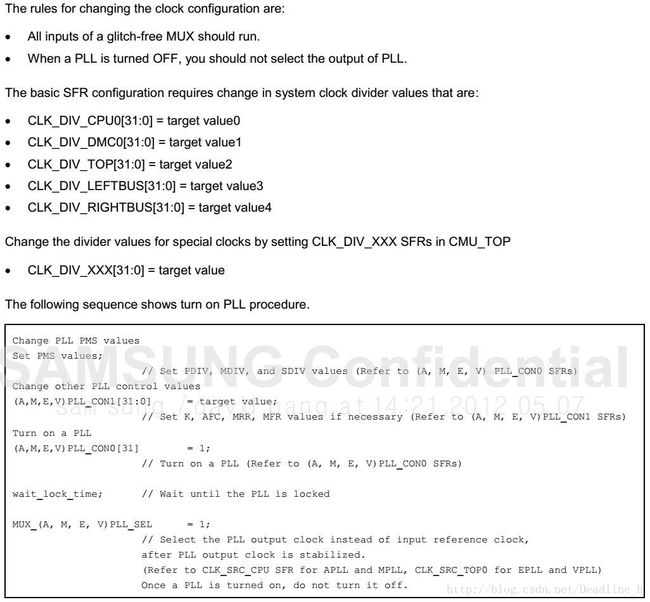

时钟配置流程

1

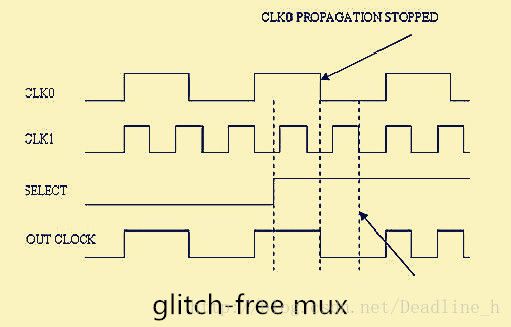

*所有无干扰时钟选择器(glitch-free MUX)的输入都应该运行。

*PLL如果关闭,输出应该选择非PLL输出。

插讲一下:

glitch-free MUX:无干扰多路选择器,也就是在改变时钟选区时不受干扰。

normal MUX:常规时钟复用器表示有干扰的时钟复用器,也就是说在改变时钟源时,要遭受脉冲信号。

对于无干扰性的选择器,你需要在改变时钟选区时确保每一个时钟源都在工作。如果不能保证,这就表明了选择时钟的过程并没有完成,会导致未知的时钟输出状态。时钟复用器的状态计算器被认定为CLK_MUX_STAT开始。

对于有干扰或无干扰,切换都是需要时间的,所以也需要延时等待。

对于有干扰性时钟复用器,在改变时钟选区的时候可能有脉冲信号的产生。为了避免有脉冲信号的影响,我们建议在时钟选区改好之前,先关闭这种复用器的输出功能。在完成选区的更换后,你可以重新使能复用的输出功能。有干扰型的时钟复用器的输出功能”MUXES”在时钟源屏蔽控制寄存器中可被屏蔽。时钟源屏蔽控制寄存器以“CLK_SRC_MASK”关键字开头标识。

2

基本的特殊功能寄存器配置需要改变系统时钟的分压器值为:

CLK_DIV_CPU0[31:0]

CLK_DIV_DMC0[31:0]

CLK_DIV_TOP[31:0]

CLK_DIV_LEFTBUS[31:0]

CLK_DIV_RIGHTBUS[31:0]

3

设置 PLL 的流程如下:

① 设置 PLL 的 P、 M、 S 值

② 设置 PLL 的其他控制参数

③ 使能 PLL

④ PLL 会等待一段时间使得时钟稳定

⑤ 设置 MUX,选择 PLL 所输出的时钟

也就是说,在我们设置PLL的时候,时钟源选择器要设置为非PLL输出,等待PLL频率锁定之后再切换回来PLL输出。

时钟初始化#

uboot2017对时钟初始化代码入口是在arch/arm/mach-exynos/clock_init_exynos4.c的system_clock_init()。我们在该函数里面对我们时钟进行配置,添加我们的代码。