基于 FPGA 的便携式 DDS 信号发生器与示波器

项目来源:2019年第三届全国大学生FPGA创新设计竞赛

一.设计概述

1.1 设计目的

利用赛灵思公司 A7 系列板卡 EG01、AD9226 模块和 DAC904 模块, 制作一个便携式、宽频带的示波器和 DDS 信号源,两者二合一,既能产生信号波形又可以实现示波器的基本功能。

1.2 应用领域

DDS 信号源可以产生生活中用到的一些基本波形,输出的信号具 有频谱纯度高、频率分辨率高和频率转换速度快等优点,该系统可以 广泛应用于通信、雷达等领域。示波器主要功能即“示波”,把肉眼 看不到的信号显示在屏幕上,并测量出信号的各种参数,如频率,幅 值,占空比,频谱等。本次设计把 DDS 信号源以及示波器结合起来, 既可以实现它们的基本功能,也具有便携式等特点。

1.3 适用范围

(1)DDS 信号源可以产生任意频率的方波、正弦波、三角波等基 本波形。

(2)示波器具有改变时基设置采样频率的功能。

(3)可以实现实时显示波形的功能。

(4)具有对波形频率、占空比、幅值分析的功能。

(5)具有 FFT 频谱分析的功能。

(6)显示波形可以左右上下移动。

1.4 设计实物

二.示波器与 DDS 信号源设计

2.1 系统介绍

DDS 系统其主要元件有相位累加器、波形存储器、数模转换器、 低通滤波器。其中 DDS 关键部分就是相位累加器,外部时钟控制相位 累加器读取数据的地址值,通过查表,把地址直接转换成为所需信号 波形的幅度数字,再经由数模转换器把信号波形幅度的数字序列进一 步转化为模拟电压,最后传送到低通滤波器。经过滤波器处理,将数 模转换器中不理想的阶梯状波形转化为平滑的所需波形。合成信号的 正弦波、方波、三角波等波形通过特殊算法处理实现。

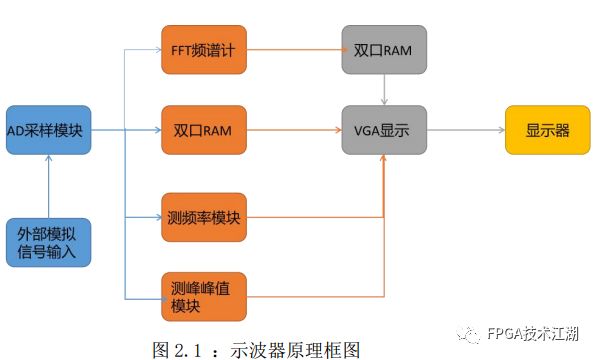

示波器系统由 ADC 采样信号处理模块、FFT 频谱计算模块、测频 模块、测峰峰值模块、VGA 显示模块组成。外部模拟信号输入 ADC 采 样模块,转化为数字信号进入 FPGA 系统。数字信号引出三路分别给 FFT 模块、测频模块、测峰峰值模块进行参数测量。引出一路写进一 片双口 RAM 中,暂存波形数据,VGA 模块从双口 RAM 中读出波形数据。FFT 模块计算出频谱,频谱数据写 入一片双口 RAM 中,VGA 模块读出 频谱数据。频率和峰峰值参数传给 VGA 显示模块。最后 VGA 显示模块 把数据传给显示器显示。

2.2 各模块介绍

2.2.1.AD 采样模块

我们采用 AD9226,AD9226 是一款 12 位,最高采样率为 65MHz 的 高速 ADC。在本设计中,我们从 FPGA 开放板引出一路 50MHz 的时钟 驱动 AD9226,作为 AD9226 的采样时钟,即采样率为 50MHz。

2.2.2.FFT 频谱计算模块

FFT(快速傅里叶变换)其本质就是 DFT,只不过可以快速的计 算出 DFT 结果,要弄懂 FFT,必须先弄懂 DFT,DFT(Discrete Fourier Transform)即离散傅里叶变换。

DFT 的公式:

对应于本设计,x(n)为经 ADC 转换后得到的序列, X(k)为对应的频谱 序列,若 ADC 采样率为![]() ,序列 x(n)长度为N ,即采集了 N 个数据点, 则 X(k)对应的频率为k *

,序列 x(n)长度为N ,即采集了 N 个数据点, 则 X(k)对应的频率为k *![]() / N , X (0)对应频率为 0,即直流分量,频率 分辨率为f =

/ N , X (0)对应频率为 0,即直流分量,频率 分辨率为f =![]() / N 。公式中的x(n)可以为复信号,实际当中x(n)都是 实信号,即虚部为 0,此时公式可以展开为:

/ N 。公式中的x(n)可以为复信号,实际当中x(n)都是 实信号,即虚部为 0,此时公式可以展开为:

在计算机中可以这样展开:

Magnitude 即 X(k)的幅值,Amplitude 为对频率点的幅值大小, 这样便得到了各个频率点的幅度,即幅度谱。

本设计我们在 Vivado 开发环境下使用 Xilinx 提供的 FFT IP 核 进行 FFT 运算。下面简单介绍一下这个 IP 核。这个IP核有两个输入接口:S_AXIS_DATA和S_AXIS_CONFIG,一个 输出接口 M_AXIS_DATA,一个时钟 aclk 和一些相关标志信号。S_AXIS_DATA 为输入数据接口,控制数据输入的状态,S_AXIS_CONFIG 为配置接口,M_AXIS_DATA 数据输出接口。控制好接口和相关标志信 号,写 IP 的驱动程序,IP 便可以开始工作,计算出 FFT 频谱。驱动 程序见附录。

要用好 FFT IP 核还必须了解它的时序图,如下:

图 2.2 :FFT 时序图

如图所示,输入和输出数据都在 AXI 总线上以流水线的的形式一 帧一帧地输入输出。本设计我们设计输入序列的长度为 2048,即输 入一帧数据为 2048 个,2048 个数依次输入,每过一个时钟周期更新 一次总线上的数据。输出数据一帧也为 2048 个,每个数据依次输出, 每过一个时钟周期更新一次总线上的数据。对应于 FFT,输入序列为 x(n),输出序列为 X(k),长度均为 2048。IP核一帧一帧地运算,当 m_axis_data_tvalid 为 1 期间,输出数据有效,每隔一定时间输出 一帧有效数据。

2.2.3.测频模块

本设计采用等精度测量法测量输入信号频率。等精度测量法,主 导思想是利用一个阀门信号保证测量时间是被测频率的整数倍,对被 测频率和基准频率进行计数,利用计数值求出被测频率,由于测量误 差只和基准频率和闸门时间有关,与被测频率无关,故称为等精度测 频。时序图如下。

预置闸门到实际闸门由一个 D 触发器实现。设标准时钟频率为![]() ,被 测频率为

,被 测频率为![]() ,如时序图所示,之间关系为

,如时序图所示,之间关系为![]()

2.2.4.测峰峰值模块

我们通过检测输入 ADC 数据的最大值和最小值,测峰峰值,每隔一段时间测一次, 输出一次。代码截图:

2.2.5.VGA 显示模块

VGA 显示原理:

首先 VGA 就是如今很多显示器上连接主机的信号传输接口。有三 排每排 5 个共 15 个引脚。如下图所示:

VGA 颜色显示是 RGB 来控制的,最高 24 位(即 RGB 各 8 位)、16 位、12 位等,本次实验采用的是 12 位的 RGB。

显示器的扫描方式是逐行扫描,即扫描像素点从屏幕最左上角开 始,从左向右,从上到下,每行结束时,用行同步信号进行同步;当 扫描完屏幕上所有的点,形成一帧,用场同步信号进行场同步,并使 扫描点重新回到屏幕的左上方,同时进行场消隐,开始下一帧。具体 的行同步时序与场同步时序如下图所示:

分辨率不同其同步、显示前沿、显示后沿、有效数据、场扫描周 期、行扫描周期等都有不同,本次实验采用的是 1024*800 的分辨率, 各个分辨率以上参数具体如下:

波形显示模块核心代码:

边框、坐标轴、方块的显示实现,核心代码如下图:

字符显示实现:

每一个字符都为 8*16,在给定区域进行显示,具体代码如下:

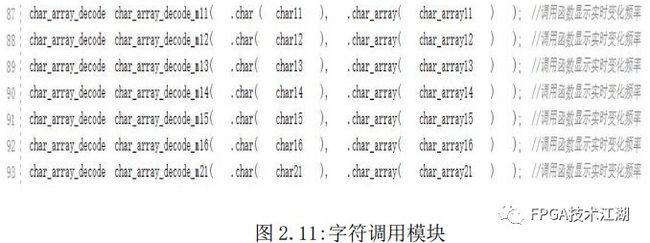

对需要显示的频率数字进行调用,代码如下:

2.2.6 相位累加器模块

相位累加器可以外部时钟信号的控制下产生读取数据的地址值, 然后通过查表法,把地址直接转化为所需信号波形的数字幅度序列。

2.2.7 波形存储器模块

波形存储器也被称之为正弦查询表,它的主要功能是在任何一个 参考时钟周期内,都可以把从上一级传输过来的相位二进制码信息作 为地址,读取查询表中的相应地址对应的幅值二进制码信息。

当收到上一级相位累加器传输过来的相位二进制码信息时,将其 作为地址来读取内部对应的预先存好的存储内容即标准信号的幅值 二进制码信息,并将这个幅值信息的 D 位二进制码传送给下一级。

2.2.8 低通滤波器模块

低通滤波器(Low Pass Filter,LPF)主要是将上级(D/A 转换 器)输出的阶梯形的正弦信号进行平滑处理,去除混叠的、无用的杂 散分量,使输出信号更为纯净,波形变得更为平滑。

完成情况及性能参数

3.1.DDS 信号源测试

此次设计的 DDS 信号源系统可以无失真稳定产生波形频率范围为 1HZ 至 2MHZ。(频率分辨率为 1HZ),1HZ、2KHZ、1MHZ 的正弦、方波、三角波如下图 所示:

3.2.示波器部分

示波器的时基变换,波形的上下左右移动因不方便截图,在视频中均有演示。

四、总结

4.1 主要创新点

本次设计完成了一个基于 FPGA 的 DDS 信号源与示波器的混合系统,其主要创新点如下:

1.该系统为便携式 DDS 信号源与示波器的混合系统,将 DDS 信号源与示波器整合在一起,更高效率的利用了 FPGA 片上资源。

2.采用等精度测量法对频率进行测量,其频率测量误差小于0.01 %。

3.自主设计 FPGA 拓展板,使系统的体积更小,整个系统更加稳定,便携性大大提高。

4.可以实时显示波形与频谱。

4.2 可扩展之处

由于开发时间有限,因此目前的系统还有许多可改进和扩展之处:

1.此次设计的示波器功能可以增加一路或多路数据通道,可以实现多个波 形的显示。

2.优化波形显示系统,可以对滤波算法进行进一步改进,从而提高波形平 滑率。

3.优化 FPGA 算法,提升片上资源利用率,比如在字符显示模块,占用了较多的寄存器资源,因而后期会针对性的完善这个模块,提高资源利用率。

4. DDS 信号源暂时只能产生频率、幅值可调的正弦、方波、三角波等,后期会完善其功能,增加产生调频、调幅波功能。

后续会持续更新,带来Vivado、 ISE、Quartus II 、candence等安装相关设计教程,学习资源、项目资源、好文推荐等,希望大侠持续关注。

大侠们,江湖偌大,继续闯荡,愿一切安好,有缘再见!