Vivado HLS 接口综合

Vivado HLS中常见的接口类型有:

1. ap_none

默认类型,该类型不适用任何I/O转换协议,它用于表示只读的输入信号,对应于HDL中的wire类型。

2. ap_stable

只用于输入信号,其具体实现方式仍为ap_none。它用于向Vivado HLS的综合器表明该信号在两次复位之间值是不变的。

3. ap_vld

在数据端口port_name的基础上创建一个额外的数据有效信号指示< port_name >_vld。

4. ap_ack

在数据端口port_name的基础上创建一个额外的应答信号指示< port_name >_ack。

5. ap_hs

使用该类型,则会同时创建额外的数据有效信号和应答信号,其效果相当于ap_vld与ap_ack之和。

6. ap_ovld

对于输入信号,其效果与ap_none是一样的。

对于输出信号,其效果与ap_vld是一样的。

对于双向(inout)类型的信号,输入使用ap_none,输出使用ap_vld进行处理。

7. ap_memory

把对数组的读写等效为对外部RAM的引用。

8. ap_fifo

把对数组、指针和参数引用的读写用FIFO的方式来实现。

9. ap_bus

把对指针和参数引用的读写用总线接口的方式来实现。

在TCL脚本中,我们也可以对接口类型进行更改。在图形化的开发界面中,可以直接在directives.tcl中进行规则的编辑,如图1所示。

![]()

图1 通过TCL配置改变端口类型

此外,我们还可以通过在Vivado HLS中的Directive视图中选择INTERFACE来进行更改,如图2所示。

![]()

图2 接口的类型选择

例如:

void adders_io(int in1, int in2, int *in_out1)

{

*in_out1 = in1 + in2 + *in_out1;

}

这里我们使用了指针。从其本质上来说,指针是一个“双向”的类型,即它即可以做为输入,同时也可以用来输出。在默认的情况下,端口的综合结果如图3所示。

![]()

图3 默认情况下的端口综合结果

如果按照图1中的示例对端口类型进行指定,则C综合之后的结果如图4所示。

![]()

图4 自定义端口类型之后的端口综合结果

在图1的示例中,我们指定了端口的类型,所以对比图3与图4,可以看出,端口in1和in2的类型从默认的ap_none变为自定义的ap_vld,并且分别具有了对应的数据有效指示位in1_ap_vld和in2ap_vld。

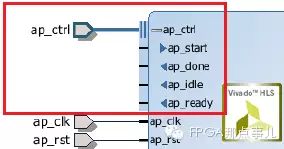

一、Block-level接口协议(块级接口协议,与函数本身相关联,不与任何数据端口相关联)

Block-Level Interface端口:

顾名思义,Block端口的作用就是用来控制Block的操作。它在c参数中没有直接的对应,但是它对应了c函数的调用/返回过程。默认Block端口都会加上,如果不需要,可以对函数顶层设置ap_none。

ap_ctrl_none: 没有块级I/O控制协议

ap_ctrl_chain: 它同ap_ctrl_hs几乎一样,除了多出一个输入信号ap_continue,它可以使得下游模块控制上游模块的运行/终止。不过这种模式比较不常用,所以有兴趣的读者,可以自己去研究相关的文档。

ap_ctrl_hs: 块级I/O控制握手协议,我们已经采用的(ap_start,ap_ready,ap_idle,ap_done)

ap_ctrl_hs是默认的端口类型,它综合出来的端口会有额外的4个系统控制信号,如下所示:

其端口行为时序如下:

在ap_rst释放后,ap_start高电平启动模块的运行,然后ap_idle立即拉低表明模块不再空闲。

ap_ready拉高表明本模块已经准备好接收新的输入,不过它的行为会稍微有些复杂,在non-pipelined实现中,ap_ready和ap_done会同时拉高;在pipelined实现中,它可能会随时拉高。

| 应用 |

描述 |

| ap_start |

该信号控制模块执行,逻辑为1时设计开始运行。 它应保持逻辑1直到相应的输出握手ap_ready被置位。当ap_ready变高时,决定了是否继续保持ap_start置位并执行其他事物或设置ap_start为逻辑0,当前事务的结束时允许设计暂停,。 如果在ap_ready为逻辑1 之前ap_start被置为低,设计有可能没有把所有输入端口读完,并可能拖延下一个输入读取操作。 |

| ap_ready |

这个输出信号表明设计已经准备好接受新数据 当准备好接受新的输入时,ap_ready 信号设置为逻辑1。表明所有为这次事物的输入读已经完成。 如果设计不是流水线操作,直到下一次事物才开始执行新的读。 这个信号是用来决定何时在端口上用新的值,决定是否用一个ap_start输入信号来启动一个新的事务。 如果ap_start信号没有被设置为高,当设计在当前事务完成中所有的操作,这个信号变为低电平。 |

| ap_done |

这个信号表明设计在当前的事务中完成所有的操作。输出逻辑1表明设计已经完成了这个事务的所有操作。因为在事务结束时,该信号为逻辑1还表示ap_return端口上的数据是有效的。 不是所有的函数都有函数返回值,因此并非所有的RTL设计都有一个ap_return端口 |

| ap_idle |

这个信号表示设计正在操作或闲置状态(无操作)。 输出端口上用逻辑1表明是空闲状态。一旦设计开始运行,该信号为低电平。 该信号为高电平时,设计完成操作,未进行任何进一步的操作。 |

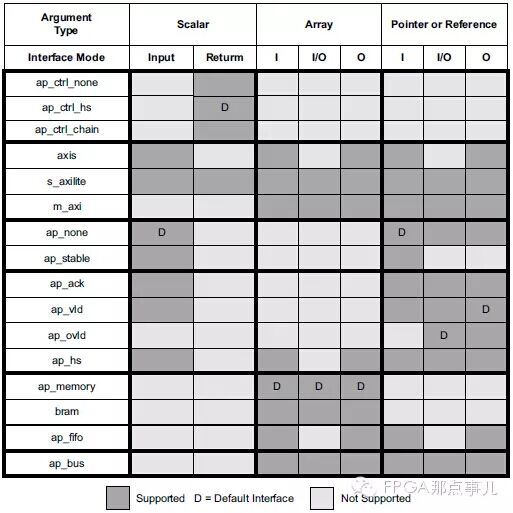

二、Port-level接口协议

Port端口会跟c的参数有直接的对应关系。按照c参数的不同,标量,数组,指针,HLS综合后的rtl端口也有很多中不同的类型可供选

a) ap_ovid :一般用于in-out 指针

b) ap_none

c) ap_hs:包括ap_vld(使能)ap_sck(应答)

其中Port level是我们需要重点关注的,它又可以细分为4中类型:(出处:http://xilinx.eetrend.com/blog/9935)

A. AXI4-Interface:支持Stream,Lite,Full共3中类型

B. NO I/O协议:无端口协议

C. Wire Handshakes:握手协议

D. Memory Interface:内存访问型的端口协议

各种rtl端口协议和c参数类型的对应关系如下:

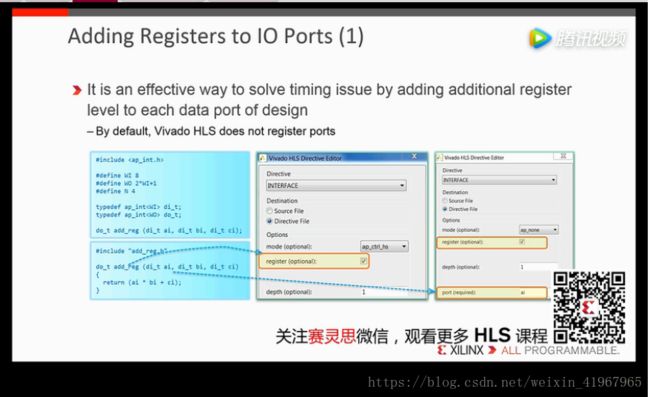

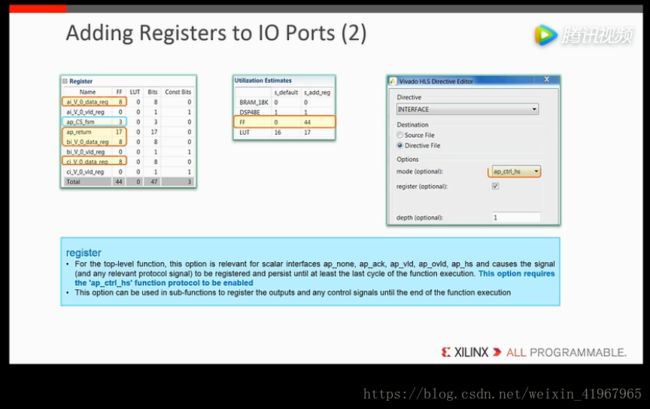

三、其他

1.可以IO口添加寄存器,目的是可以控制输入输出波形。(添加寄存器条件是要配置成:ap_hs)

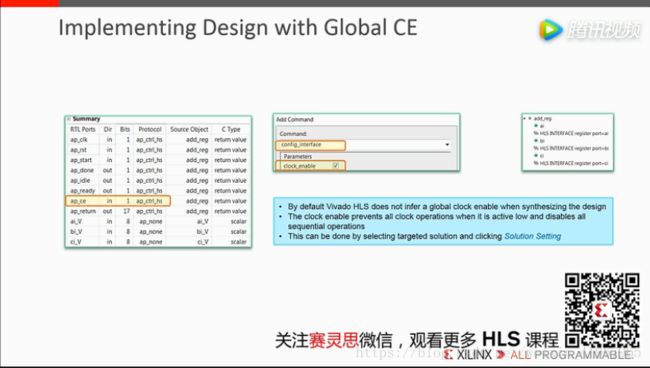

2.可以对设计添加全局使能端口。