计数器,ROM和DDS

一.新代码:

1.带计数增量输入的计数器:

module cnt_incr(

CLK , // clock

INCR , // counterincrease value

CNTVAL); //counter value

input CLK;

input [7-1:0] INCR;(增量由拨码开关决定,emmmmmm… …有点儿像循环步长)

output [7-1:0] CNTVAL;

reg [7-1:0] CNTVAL;

always @ (posedge CLK) begin

CNTVAL <= INCR + CNTVAL;

end

endmodule //module cnt_incr

2. 正弦波表数据ROM

该ROM中数据为一个整周期正弦波128点采样,每个样点采用8比特量化,数据范围(-1,1),二进制补码格式。

module sine_rom(

CLK , // clock

RA , // read address

RD ); // read data

input CLK;

input [6 :0]RA;

output [7 :0] RD;

reg [7 :0] RD;

always @ (posedge CLK)

case(RA)

7 'd 0 :RD = #1 8 'b 00000000; // 0 0x0

7 'd 1 :RD = #1 8 'b 00000110;// 6 0x6

7 'd 2 :RD = #1 8 'b 00001100; // 12 0xC

7 'd 3 :RD = #1 8 'b 00010010;// 18 0x12

7 'd 4 :RD = #1 8 'b 00011000; // 24 0x18

7 'd 5 :RD = #1 8 'b 00011110; // 30 0x1E

7 'd 6 :RD = #1 8 'b 00100100;// 36 0x24

7 'd 7 :RD = #1 8 'b 00101010; // 420x2A

7 'd 8 :RD = #1 8 'b 00110000; // 480x30

7 'd 9 :RD = #1 8 'b 00110110; // 540x36

7 'd 10 :RD = #1 8 'b 00111011; // 590x3B

7 'd 11 :RD = #1 8 'b 01000001; // 650x41

7 'd 12 :RD = #1 8 'b 01000110; // 700x46

7 'd 13 :RD = #1 8 'b 01001011; // 750x4B

7 'd 14 :RD = #1 8 'b 01010000; // 800x50

7 'd 15 :RD = #1 8 'b 01010101; // 850x55

7 'd 16 :RD = #1 8 'b 01011001; // 890x59

7 'd 17 :RD = #1 8 'b 01011110; // 940x5E

7 'd 18 :RD = #1 8 'b 01100010; // 980x62

7 'd 19 :RD = #1 8 'b 01100110; // 1020x66

7 'd 20 :RD = #1 8 'b 01101001; // 1050x69

7 'd 21 :RD = #1 8 'b 01101100; // 1080x6C

7 'd 22 :RD = #1 8 'b 01110000; // 1120x70

7 'd 23 :RD = #1 8 'b 01110010; // 1140x72

7 'd 24 :RD = #1 8 'b 01110101; // 1170x75

7 'd 25 :RD = #1 8 'b 01110111; // 1190x77

7 'd 26 :RD = #1 8 'b 01111001; // 1210x79

7 'd 27 :RD = #1 8 'b 01111011; // 1230x7B

7 'd 28 :RD = #1 8 'b 01111100; // 1240x7C

7 'd 29 :RD = #1 8 'b 01111101; // 1250x7D

7 'd 30 :RD = #1 8 'b 01111110; // 1260x7E

7 'd 31 :RD = #1 8 'b 01111110; // 1260x7E

7 'd 32 :RD = #1 8 'b 01111111; // 1270x7F

7 'd 33 :RD = #1 8 'b 01111110; // 1260x7E

7 'd 34 :RD = #1 8 'b 01111110; // 1260x7E

7 'd 35 :RD = #1 8 'b 01111101; // 1250x7D

7 'd 36 :RD = #1 8 'b 01111100; // 1240x7C

7 'd 37 :RD = #1 8 'b 01111011; // 1230x7B

7 'd 38 :RD = #1 8 'b 01111001; // 1210x79

7 'd 39 :RD = #1 8 'b 01110111; // 1190x77

7 'd 40 :RD = #1 8 'b 01110101; // 1170x75

7 'd 41 :RD = #1 8 'b 01110010; // 1140x72

7 'd 42 :RD = #1 8 'b 01110000; // 1120x70

7 'd 43 :RD = #1 8 'b 01101100; // 1080x6C

7 'd 44 :RD = #1 8 'b 01101001; // 1050x69

7 'd 45 :RD = #1 8 'b 01100110; // 1020x66

7 'd 46 :RD = #1 8 'b 01100010; // 980x62

7 'd 47 :RD = #1 8 'b 01011110; // 940x5E

7 'd 48 :RD = #1 8 'b 01011001; // 890x59

7 'd 49 :RD = #1 8 'b 01010101; // 850x55

7 'd 50 :RD = #1 8 'b 01010000; // 800x50

7 'd 51 :RD = #1 8 'b 01001011; // 750x4B

7 'd52 :RD = #1 8 'b 01000110; // 70 0x46

7 'd 53 :RD = #1 8 'b 01000001; // 650x41

7 'd 54 :RD = #1 8 'b 00111011; // 590x3B

7 'd 55 :RD = #1 8 'b 00110110; // 540x36

7 'd 56 :RD = #1 8 'b 00110000; // 480x30

7 'd 57 :RD = #1 8 'b 00101010; // 420x2A

7 'd 58 :RD = #1 8 'b 00100100; // 360x24

7 'd 59 :RD = #1 8 'b 00011110; // 300x1E

7 'd 60 :RD = #1 8 'b 00011000; // 240x18

7 'd 61 :RD = #1 8 'b 00010010; // 180x12

7 'd 62 :RD = #1 8 'b 00001100; // 120xC

7 'd 63 :RD = #1 8 'b 00000110; // 60x6

7 'd 64 :RD = #1 8 'b 00000000; // 00x0

7 'd 65 :RD = #1 8 'b 11111010; // -6 0xFA

7 'd 66 :RD = #1 8 'b 11110100; // -120xF4

7 'd 67 :RD = #1 8 'b 11101110; // -180xEE

7 'd 68 :RD = #1 8 'b 11101000; // -240xE8

7 'd 69 :RD = #1 8 'b 11100010; // -300xE2

7 'd 70 :RD = #1 8 'b 11011100; // -360xDC

7 'd 71 :RD = #1 8 'b 11010110; // -420xD6

7 'd 72 :RD = #1 8 'b 11010000; // -480xD0

7 'd 73 :RD = #1 8 'b 11001010; // -540xCA

7 'd 74 :RD = #1 8 'b 11000101; // -590xC5

7 'd 75 :RD = #1 8 'b 10111111; // -650xBF

7 'd 76 :RD = #1 8 'b 10111010; // -700xBA

7 'd 77 :RD = #1 8 'b 10110101; // -750xB5

7 'd 78 :RD = #1 8 'b 10110000; // -800xB0

7 'd 79 :RD = #1 8 'b 10101011; // -850xAB

7 'd 80 :RD = #1 8 'b 10100111; // -890xA7

7 'd 81 :RD = #1 8 'b 10100010; // -940xA2

7 'd 82 :RD = #1 8 'b 10011110; // -980x9E

7 'd 83 :RD = #1 8 'b 10011010; // -1020x9A

7 'd84 :RD = #1 8 'b 10010111; // -105 0x97

7 'd 85 :RD = #1 8 'b 10010100; // -1080x94

7 'd 86 :RD = #1 8 'b 10010000; // -1120x90

7 'd 87 :RD = #1 8 'b 10001110; // -1140x8E

7 'd 88 :RD = #1 8 'b 10001011; // -1170x8B

7 'd 89 :RD = #1 8 'b 10001001; // -1190x89

7 'd 90 :RD = #1 8 'b 10000111; // -1210x87

7 'd 91 :RD = #1 8 'b 10000101; // -1230x85

7 'd 92 :RD = #1 8 'b 10000100; // -1240x84

7 'd 93 :RD = #1 8 'b 10000011; // -1250x83

7 'd 94 :RD = #1 8 'b 10000010; // -1260x82

7 'd 95 :RD = #1 8 'b 10000010; // -1260x82

7 'd 96 :RD = #1 8 'b 10000001; // -1270x81

7 'd 97 :RD = #1 8 'b 10000010; // -1260x82

7 'd 98 :RD = #1 8 'b 10000010; // -1260x82

7 'd 99 :RD = #1 8 'b 10000011; // -1250x83

7 'd 100 :RD = #1 8 'b 10000100; // -1240x84

7 'd 101 :RD = #1 8 'b 10000101; // -1230x85

7 'd 102 :RD = #1 8 'b 10000111;// -121 0x87

7 'd 103 :RD = #1 8 'b 10001001;// -119 0x89

7 'd 104 :RD = #1 8 'b 10001011;// -117 0x8B

7 'd 105 :RD = #1 8 'b 10001110; // -114 0x8E

7 'd 106 :RD = #1 8 'b 10010000;// -112 0x90

7 'd 107 :RD = #1 8 'b 10010100; // -108 0x94

7 'd 108 :RD = #1 8 'b 10010111; // -105 0x97

7 'd 109 :RD = #1 8 'b 10011010; // -102 0x9A

7 'd 110 :RD = #1 8 'b 10011110; // -98 0x9E

7 'd111 :RD = #1 8 'b 10100010; // -94 0xA2

7 'd 112 :RD = #1 8 'b 10100111;// -89 0xA7

7 'd 113 :RD = #1 8 'b 10101011; // -85 0xAB

7 'd 114 :RD = #1 8 'b 10110000; // -80 0xB0

7 'd 115 :RD = #1 8 'b 10110101; // -75 0xB5

7 'd 116 :RD = #1 8 'b 10111010;// -70 0xBA

7 'd 117 :RD = #1 8 'b 10111111;// -65 0xBF

7 'd 118 :RD = #1 8 'b 11000101; // -59 0xC5

7 'd 119 :RD = #1 8 'b 11001010; // -54 0xCA

7 'd 120 :RD = #1 8 'b 11010000; // -48 0xD0

7 'd 121 :RD = #1 8 'b 11010110;// -42 0xD6

7 'd 122 :RD = #1 8 'b 11011100; // -36 0xDC

7 'd 123 :RD = #1 8 'b 11100010;// -30 0xE2

7 'd 124 :RD = #1 8 'b 11101000; // -24 0xE8

7 'd 125 :RD = #1 8 'b 11101110; // -18 0xEE

7 'd 126 :RD = #1 8 'b 11110100;// -12 0xF4

7 'd 127 :RD = #1 8 'b 11111010;// -6 0xFA

default : RD = #1 0;

endcase

endmodule

并未全部注释都变绿… …意思一下… …

二.创建符号,连接BDF图,指派管脚,在RTL视图下分析功能(上述步骤自己去前几篇翻一翻… …)

结论:RAM输出是不带D触发器的,反而是输入地址上带有D触发器。注意理解“时序等效”的电路结构,这一要点。

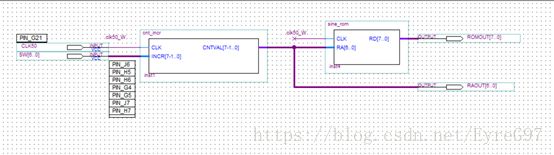

BDF图如下:

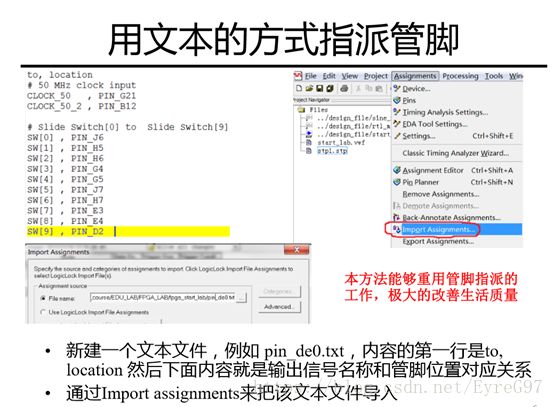

关于annoying的管脚安排tips:

三.添加Signal tap 观察点

添加节点之前先synthesis一下:![]()

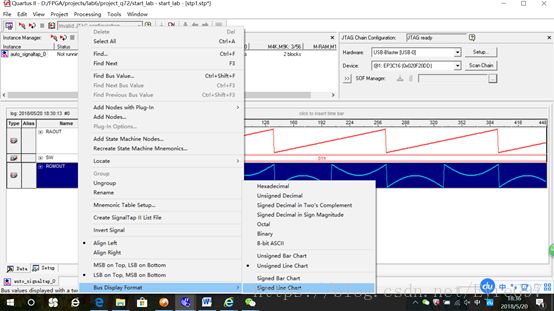

拨动SW6到SW0 开关,观察 Signal TAP的信号。在ROMOUT栏右键单击,选择使用Signed Line Chart格式观察 ROM的输出数据和使用Unsigned Line Chart格式观察ROM的地址。

使用unsigned模式便于观察周期关系,使用signed便于观察正弦波形。

重点总结:

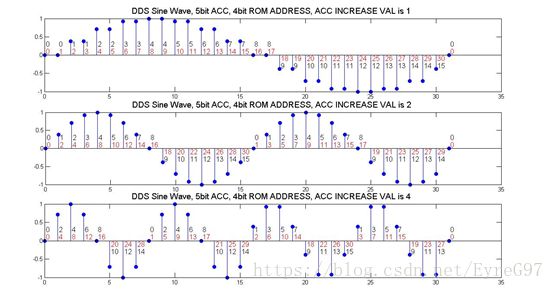

拨动开关,观察不同频率的正弦波– 电路的工作时钟是50MHz

–请回答,你能得到的正弦波频率和计数器增量值的对应关系是什么?

–请回答,你能得到的最低频率的正弦波是多少?设该频率为f1

–请思考,能否有什么方法能够得到比f1频率还低的正弦波

【答】:

(1) 正弦波频率和计数器增量值成正比例线性关系。

解释:拨码开关控制增量0~127,举个栗子来说,当增量为1时,产生一个正弦信号周期需采样128次,则频率为(50MHz / 128 =0.39MHz);当增量为127时,则每周期采样1次,则频率为50MHz。

(2)f1约0.39 MHZ。(见上分析)

(3)增加计数器增量或减小计数器数据位宽。

推导过程如下[smile with tears]:

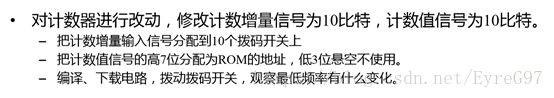

新任务:

改后代码:

module cnt_incr(

CLK , // clock

INCR , // counterincrease value

CNTVAL); //counter value

input CLK;

input [10-1:0] INCR;

output [10-1:0] CNTVAL;

reg [10-1:0] CNTVAL;

always @ (posedge CLK) begin

CNTVAL <= INCR + CNTVAL;

end

endmodule //module cnt_incr

完成后的BDF图

重要结论:

与原来相比,最低频率扩大23 (8)倍!

In the end——这种电路有个好听的名字,叫做:直接数字频率合成(DDS)。

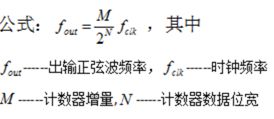

请给出:输出信号频率和电路工作时钟频率,计数器增量值,以及计数器数据位宽之间的表达式关系:

(帮助理解,图源http://ecdav.cuc.edu.cn/web_root/ShiYanJiaoXue/DDS_FPGA_REF_DISIGN/content.htm

)