Nand Flash之并行与串行

串行Flash与并行Flash

之前我们有讲到NAND Flash与NOR Flash的封装、读取速率、写速率和电路设计等方面的差异,现在我们将会讲到并行与串行Flash,主要是串行吧,并行需要讲的很少。

因为串行与并行主要区别在于IO口的数量上,因为有些场景上我不会用到那么大的容量,E而且也不会有那么多的IO引脚,所以串行NOR与NAND Flash应运而生。

并行与串行NAND Flash

SERIAL NOR FLASH

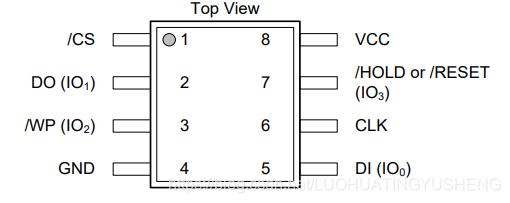

串行NOR Flash支持标准串行外设接口(SPI),双/四路I / O SPI:串行时钟,片选,串行数据I / O0(DI),I / O1(DO),I / O2和I / O3。

也就是说对于串行NOR Flash而言,支持下面的几种模式。

Standard SPI

Standard SPI: CLK, /CS, DI, DO

Dual SPI

Dual SPI: CLK, /CS, IO0, IO1

Quad SPI

Quad SPI: CLK, /CS, IO0, IO1, IO2, IO3

传输时钟速率

- 串行NOR Flash 在Standard SPI模式下支持高达133MHz 时钟频率(标准模式);

- 串行NOR Flash 在Dual SPI模式下支持高达133MHz *2 时钟频率(Dual);

- 串行NOR Flash 在Quad SPI模式下支持高达133MHz *4 时钟频率(Quad);

这些传输速率可以胜过标准的异步8和16位并行闪存。

串行NOR Flash常见封装

- IO0 and IO1 are used for Standard and Dual SPI instructions;

- IO0 – IO3 are used for Quad SPI instructions, /HOLD (or /RESET) function is only available for Standard/Dual SPI.

以上引脚如何配置

1)标准 SPI模式

连接CS、CLK、DO和DI就可以,WP引脚和HOLD引脚视情况而定,看是要硬件上拉到Vcc还是电阻下拉到地。

2)Dual SPI模式

连接CS、CLK、DO(IO1)、DI(IO0),此时注意不是按照DO和DI工作,而是括号内的IO1和IO2。

3)Quad SPI模式

CS、CLK、DO(IO1)、DI(IO0)、WP(IO2)、HOLD/Reset/IO3,此时WP与Hold功能全都不能使用。

标准SPI,双SPI和四线SPI操作

标准SPI指令使用单向DI(输入)引脚在串行时钟(CLK)输入引脚的上升沿串行写入指令,地址或数据。

标准SPI还使用单向DO(输出)在CLK下降沿读取器件的数据或状态。

双SPI和四SPI指令使用双向IO引脚串行写入指令,在CLK的上升沿向器件发送地址或数据,并在CLK的下降沿从器件读取数据或状态。

电路设计

片选(/ CS)

SPI片选(/ CS)引脚用于使能和禁止器件操作。 当/ CS为高电平时,器件被取消选择,串行数据输出(DO或IO0,IO1,IO2,IO3)引脚处于高阻态。取消选择后,器件功耗将处于待机电平,除非内部擦除,编程或写状态寄存器周期正在进行中。当/ CS变为低电平时,将选择器件,功耗将增加到有效电平,并且可以写入指令并从器件读取数据。

上电后,/ CS必须在接受新指令之前从高电平转换为低电平。/ CS输入必须在上电和断电时跟踪VCC电源电平。如果需要,可以使用/ CS引脚上的上拉电阻来实现此目的。

写保护(/ WP)

写保护(/ WP)引脚可用于防止写入状态寄存器。扇区的部分或整个存储器阵列可以受硬件保护,需要与寄存器相互配置。 WP引脚为低电平有效。

HOLD(/ HOLD)

/ HOLD引脚允许器件在主动选择时暂停。当/ HOLD变为低电平时,/ CS为低电平时,DO引脚将处于高阻态,DI和CLK引脚上的信号将被忽略)。当/ HOLD变为高电平时,器件操作可以恢复。

当多个设备共享相同的SPI信号时,/ HOLD功能非常有用。 / HOLD引脚为低电平有效。

Serial Clock (CLK)

SPI串行时钟输入(CLK)引脚提供串行输入和输出操作的时序。

复位(/ RESET)

当它被驱动为低电平至少1μS的时间时,该器件将终止任何外部或内部操作并返回其上电状态。

电源

串行Flash的电压也有多种规格,具体的看数据书册就行。

电路设计

如上图为串行 Nor Flash电路,

WP引脚连接电阻至Vcc;为了不进行写保护,所以做上拉,但是不悬空是为了在上电时有一个确定的电平状态。

Hold引脚连接上拉电阻至Vcc;为了不实现数据保持,所以做上拉,但是不悬空是为了在上电时有一个确定的电平状态。

CS引脚也是上拉至Vcc。上电不选中该器件,只有后续CPU低电平才会选中该器件。

以下请参考:

[1].华邦

[2].复旦微电子

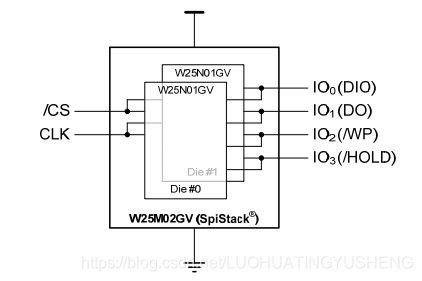

SERIAL NAND FLASH

注:因为串行NOR Flash与串行NAND Flash所要实现的功能一致,为了减少/简化并行Nand Flash的接口,所以两者的封装等都是一样的,差异只是在于存储器单位存储的结构不同,其余都是一样的,所以大家知道了串行NOR Flash的介绍后,同样就理解串行NAND Flash了。

20194.14

于深圳