华中科技大学组原实验记录 运算器ALU实验

本实验是华科大三的核心课计算机组成原理的配套实验,设计非常良心,而且理论课和实验课都在mooc上有全套视频,地址为计算机组成原理_中国大学MOOC,实验所用的软件资源/测试电路也全部开放,地址为:计算机硬件系统设计_中国大学MOOC

运算器实验

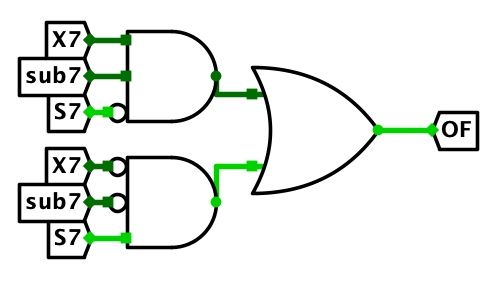

8位可控加减法器

-

sub=0时表示加法,否则减法

-

我们可以用8个一位全加器串行进位实现8位加法

-

如果要做减法就加上减数的补码,这里的补码可以按位取反(即异或1),再最低位加1(即最低位给一个进位信号)

4位先行进位74182

所以有如下的规则:

C 1 = G 1 + P 1 C 0 C_1 = G_1 + P_1C_0 C1=G1+P1C0

C 2 = G 2 + P 2 G 1 + P 2 P 1 C 0 C_2 = G_2 + P_2G1 + P_2P_1C_0 C2=G2+P2G1+P2P1C0

C 3 = G 3 + P 3 G 2 + P 3 P 2 G 1 + P 3 P 2 P 1 C 0 C_3 = G_3 + P_3G_2 + P_3P_2G_1 + P_3P_2P_1C_0 C3=G3+P3G2+P3P2G1+P3P2P1C0

C 4 = G 4 + P 4 G 3 + P 4 P 3 G 2 + P 4 P 3 P 2 G 1 + P 4 P 3 P 2 P 1 C 0 C_4 = G_4 + P_4G_3 + P_4P_3G_2 + P_4P_3P_2G_1 + P_4P_3P_2P_1C_0 C4=G4+P4G3+P4P3G2+P4P3P2G1+P4P3P2P1C0

- 成组进位的生成函数:

于是我们可以按照上面的公式连线:

这样就做好了并行进位,连线非常复杂。

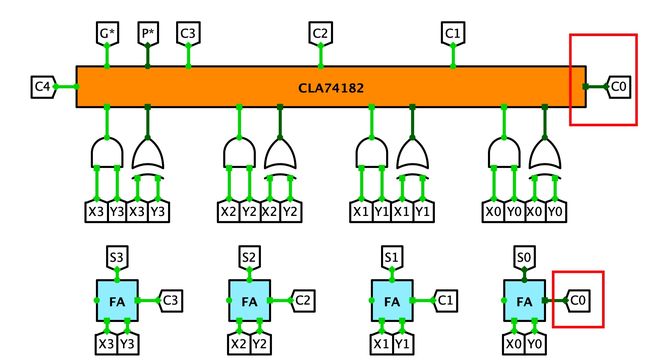

4位快速加法器

- 要求我们用先行进位信号电路74182来构造一个四位的加法器

- 因为74182已经能够产生各级进位信号,所以只需要把各级的PG连到74182的输入端,再计算各位数的值

这里有一点要注意,就是74182是 C 0 C_0 C0的函数,一定要连上 C 0 C_0 C0

16位快速加法器

- 在74182和做好了的四位快速加法器的基础上构建一个16位快速加法器。组间进位复用74182,类似的连好线。这里可以把四位快速加法器也看作一个一位的运算单元,产生相应的PG信号,连到输入端。输出的进位连到四位快速加法器最低位的进位端。

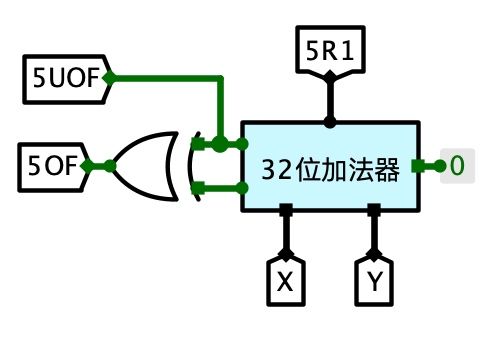

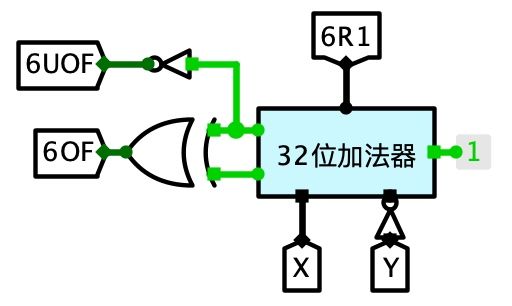

32位快速加法器

-

用4位快速加法器和74182电路构建一个最快的快速加法器。对性能有要求,所以仍然要用到组间并行进位。

-

如果需要64位的怎么办?应该就跟从4位到16位一样,输入相应的PG信号,得到相应的进位信号。所以说74182电路像一个递归电路一样,输入4个PG值,得到4个进位值和更高阶的 P ∗ G ∗ P^* G^* P∗G∗值

-

这里需要32位,那么可以用两个16位的串联:

5位阵列乘法器

如图,需要 5 ∗ 4 5*4 5∗4个全加器。由于采用了斜向进位,时延缩小至 3 ∗ 8 + 1 = 25 T 3*8+1=25T 3∗8+1=25T

6位补码阵列乘法器

-

利用5位阵列乘法器实现6*6位的补码乘法器

-

因为5位阵列乘法器默认是没有符号的,所以这里要实现有符号的运算,符号位得单独运算

-

先求得X和Y的绝对值,正数的话直接取低5位,是负数的话先取负再取低5位:

-

- 32 32 32二进制是 1000 0 ( 2 ) 10000_{(2)} 10000(2),而 + 32 +32 +32是无法在5位内表示的,5位有符号数的表示范围是 [ − 32 , 31 ] [-32,31] [−32,31],因此我们在这儿取负数之后的值仍然不对,会有一个截断误差,所以参加运算的乘数不能小于 − 31 -31 −31。

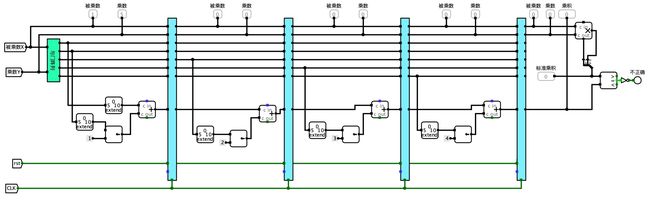

5位无符号乘法流水线

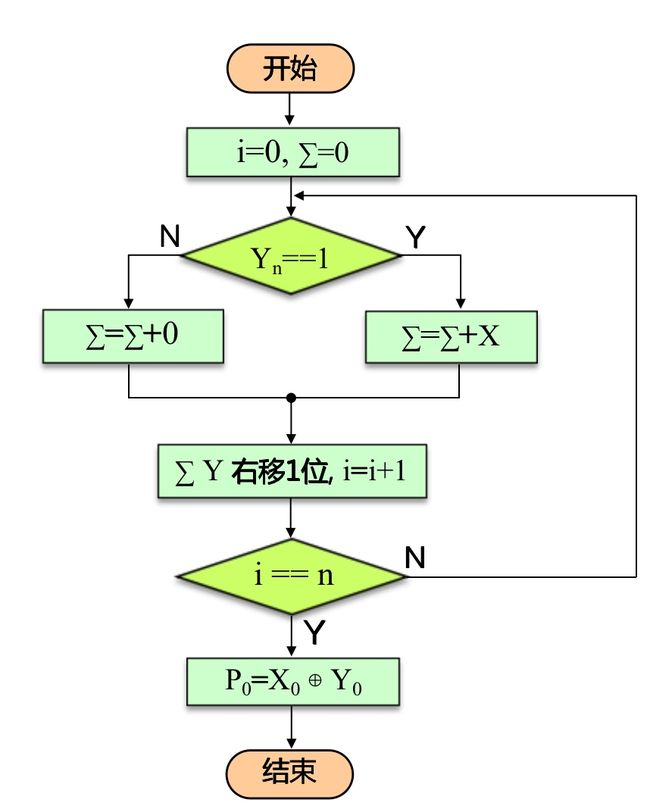

原码一位乘法器

需要声明几个比较重要的概念:

- 部分积:就是用 Y i Y_i Yi乘以 X X X所得到的积

- 累加和:把当前求过的所有部分积(作适当的右移)加起来所得到的和

- 移位:这里的思路是先算 Y 0 Y_0 Y0和 X X X的乘积,加到累加和中,然后Cout,和数,Y全部右移,这样就比较节省空间,处理到Y的高位的时候,低位反正没有用,可以移出去,这时高位空出的空间就可以放累加和移出来的部分了

所以我们先把加法逻辑的部分画好,用Y当前的最低位判断本轮 ∑ \sum ∑是不变还是加X:

然后是移位逻辑,两个8bit的寄存器,每个时钟都一起右移1位,用分线器来实现:

这里有一个很坑的地方,就是ADD的进位输出端,必须要连到 s u m ′ sum' sum′的最高位。如果不连上,最高位取0的话,255x3 的计算答案就是错的。为什么呢?考虑一下手工计算的过程:

这里产生了一个进位信号,也是包含在答案里面的,但是由于寄存器的位数有限,在移位之前并不能保存,所以移位的时候不能忘了它也要右移一位放到最高位~

最后需要连的就是控制逻辑。第一个周期,我们要把Y的值送到寄存器里,再经过8个周期,数据累加和右移完成之后要控制停机,这里需要控制各个寄存器的enable端是否有效。于是需要另加一个counter记录时钟周期数,并生成时序信号LOAD和STOP:

大于8个周期时就发出STOP,让系统暂停。

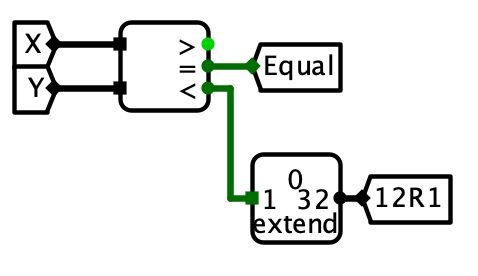

32位ALU

我们先构造出每一种功能的输出,再根据OP的值来选择输出