DSM调制器原理及simulink仿真分析

DSM调制器原理及simulink仿真分析

- 一.背景介绍

- 1.1整数分频

- 1.1.1双模分频器和计数器实现多模分频器

- 1.1.2 2\3分频单元实现多模分频器

- 1.2小数分频原理及缺点

- 1.2.1 小数分频基本原理

- 1.2.2小数杂散

- 二.Sigma-Delta调制器基本原理

- 2.1背景介绍

- 2.2 过采样技术(参考时钟)

- 2.3 噪声整型()

- 三. Δ Σ \Delta\Sigma ΔΣ调制器设计及仿真

- 3.1一阶调制器设计及仿真

- 3.1.1 一阶调制器原理

- 3.1.2 一阶调制器仿真

- 3.2MASH1-1-1设计及仿真

- 3.2.1 MASH1-1-1 原理

- 3.2.2 MASH1-1-1 仿真

一.背景介绍

在射频电路中常常用到分频器,其中可编程分频器应用广泛,可以产生多种分频比。

本文用到的参考文献及simulink工程文件,点击此处下载

1.1整数分频

1.1.1双模分频器和计数器实现多模分频器

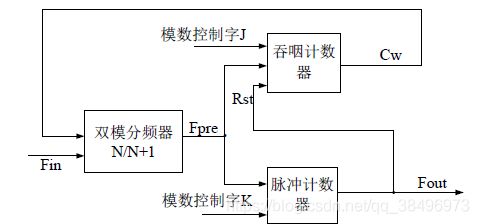

a) 首先进行初始化,两个计数器分别载入初值J 和K,设定N/N+1双模分频器的模数控制字Cw 为低电平0,控制双模分频器实现N+1分频,否则双模分频器实现N分频。计数器开始倒计数。

b) 计数器采用减法计数方式,每个时钟上升沿到来,两个计数器自减一,因为吞咽计数器初值K小于脉冲计数器初值J,所以吞咽计数器首先减为0 值。

c) 吞咽计数器到达0 值以后,控制模数控制信号Cw 跳变为1,N/N+1双模分频器开始进行N 分频,在此期间脉冲计数器一直进行减一计数,直到变为0 值。

d) 在脉冲计数器减到0 值后,产生一个复位信号Rst,模数控制字Cw再次跳变为低电平0。这样便完成了一个周期的工作过程,重新置入初值。

e) 重复上述步骤。

综上所述:总的分频比为 D R = K ( N + 1 ) + ( J − K ) N = K + J N DR=K(N+1)+(J-K)N=K+JN DR=K(N+1)+(J−K)N=K+JN

一帮情况下,N是定值,通过修改K和J的值实现不同的分频比。

缺点

1.分频比最小值为1,即频率最小步进值为参考频率Fclk。在某些应用中,较低的参考时钟频率会限制系统性能。

2.针对与不同的系统要求,需要重新设计双模分频器以及计数器,而且多位的计数器硬件消耗较大。

1.1.2 2\3分频单元实现多模分频器

另外一种 采用2/3单元组合构成多模分频器。

该结构的不足就是分频范围受限,最小分频值是 2 n 2^n 2n,最大分频比为 2 n + 1 − 1 2^{n+1}-1 2n+1−1。

缺点

1.最小分频比受限,有相关论文解决此问题。

2.随着2/3分频单元的增加,功耗增大。

优点

1.相比于双模分频器构成的多模分频器,其结构简单,容易扩展,每个分频单元的结构完全相同,方便后端设计。

1.2小数分频原理及缺点

1.2.1 小数分频基本原理

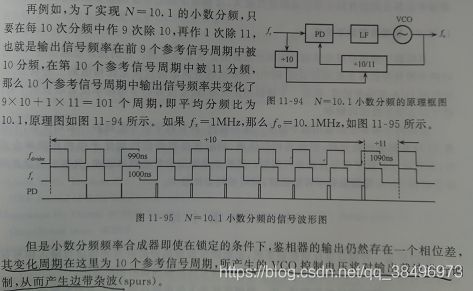

小数分频主要思想是一段时间范围内的平均分频比,仍然通过基本的整数分频实现,通过控制**双模或多模分频器(注意可以是多模分频器)**不断改变分频比。比如:

电路中需要实现一个100.1的小数分频,便可以控制一个100 /101双模分频器进行9次100分频,再进行1 次101分频,这样得到的平均分频值就是: N F = ( 9 ∗ 100 + 101 ∗ 1 ) / 10 = 100.1 NF=(9*100+101*1)/10=100.1 NF=(9∗100+101∗1)/10=100.1

上式中N:分频比的整数部分,F:分频比的小数部分#

1.2.2小数杂散

小数杂散的本质:** 双模或多模分频器**的分频比不是完全的随机,存在有一定的周期性,因此经过鉴频鉴相器(PFD)和低通滤波器(LPF)之后会产生一定周期性的脉冲信号对电荷泵充放电。在频域上会体现在固定频偏处的噪声信号较大。

根据小数杂散的原理一直小数杂散的方法可以通过将分频比更加随机化将噪声信号随机化,使得噪声信号没有固定的频率,相当于白噪声。

二.Sigma-Delta调制器基本原理

本文用到的参考文献及simulink工程文件,点击此处下载

2.1背景介绍

整个 Δ Σ \Delta\Sigma ΔΣ调制器基于过采样和噪声整型技术,过采样使得噪声总功率虽然不变但是分布在信号频带中的噪声明显减少,信噪比得以提高。噪声整型技术进一步压缩带内噪声,将噪声推向高频,通过低通滤波器滤除带外噪声。

2.2 过采样技术(参考时钟)

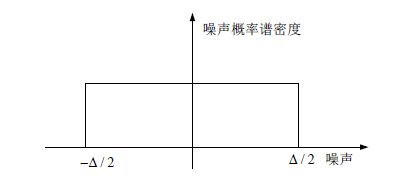

过采样技术的前提假设:

1.量化量化噪声的概率密度为匀概率密度

2.量化噪声的功率谱密度为白噪声

以上两个假设的成立的前提是分频比随机化,分频比不能有固定的频率,只有当分频比随机化之后,小数杂散不会固定频率点,量化噪声的概率密度和功率谱密度才能如图所示,为一个常数。

学习i到此处产生了几个疑问。

问题一: 什么是量化噪声?此处的量化噪声与ADC中的量化噪声有何区别

1.ADC中的量化噪声:

模数转化的过程涉及到采样、量化和编码,这不可避免的就会引入量化误差,量化过程需要根据量化单位(表示为 Δ \Delta Δ )的大小对每个模拟信号的采样值进行分级,每一级的大小只能是量化单位的整数倍,而模拟信号一定存在不能被整除的,所以产生了量化误差。

2. Δ Σ \Delta\Sigma ΔΣ调制器中的量化噪声:

假设小数分频比为N.F,将调制器看作一个黑匣子,输入N.F,经过调制器后输出控制信号为Control信号(control不一定只有0,1)。进而控制双模/多模分频器分频。由1.2.1节分析可知,输入分频比N.F和实际瞬时分频比存在误差,这也是量化误差一种。

量化误差并不是ADC中特有的概念,在数字量——>数字量,模拟量——>模拟量,数字量——>模拟量,模拟量——>数字量中,凡是存在数据的转换过程,都可以称之为量化。量化过程的本质是A——>B的一种转换。

问题二: DSM调制器中哪里应用了过采样的原理?

过采样的本质是用远高于奈奎斯特采样速率采样速率去实现A-B的转换过程。DSM调制器一般用高速时钟如F=26MHz。DSM中用到了累加器,移位器等等( 先当作已知信息,后面章节会详细分析 ),都是时钟驱动电路。而调制器的输出(分频比控制信号)相比于时钟信号,其变化速度较慢。此时就产生了高速时钟Fclk对分频比控制信号过采样。

实际上,过采样的原理隐含在了广义的量化过程中,没有向下面2.3节中噪声整型体现的明显。DSM调制器的设计分析过程主要体现噪声整型,过采样隐含其中。

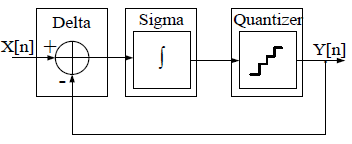

2.3 噪声整型()

噪声整形的原理就是运用反馈把位于信号带宽内的噪声不断的压缩,目的就是把它被推到信号频带以外,因为信号频带外的噪声便能够通过环路中的低通滤波器滤除掉。首先对电路构造一个噪声传递函数NTF,使量化噪声通过电路的处理之后,其频谱形状发生改变,即实现了噪声整形。

三. Δ Σ \Delta\Sigma ΔΣ调制器设计及仿真

3.1一阶调制器设计及仿真

3.1.1 一阶调制器原理

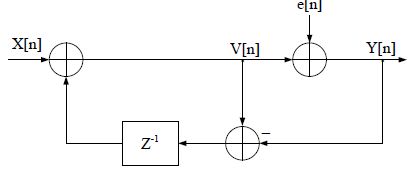

如图 所示为一阶SDM 的结构框图,可以看到它由一个Delta 调制器,一个积分器以及一个量化器组成,积分器在离散系统用延迟求和表示,所以该种结构的调制器便被称作Sigma-Delta 调制器。下图它的Z域的结构框图。

Y [ z ] = X [ z ] + ( 1 − z − 1 ) E [ z ] (3.1) Y[z]=X[z]+(1-z^-1)E[z] \tag{3.1} Y[z]=X[z]+(1−z−1)E[z](3.1)

由上式可以看出,图3.2的调制器线性模型满足2.3节噪声整型的分析,对于信号X[z]是全通,对于量化噪声是高通滤波。

针对图3.2重新写写传递函数

V [ z ] = X [ z ] + ( V [ z ] − Y [ z ] ) − 1 (3.2) V[z]=X[z]+(V[z]-Y[z])^-1 \tag{3.2} V[z]=X[z]+(V[z]−Y[z])−1(3.2)

图3.3也对应于累加器的z域模型,下面分析累加器z域模型域DSM 调制器的关系

e [ n ] = C [ n ] − S [ n ] e[n]=C[n]-S[n] e[n]=C[n]−S[n]。e[n]的负值等于剩余的m位不带进位的和项。误差讲过m位寄存器延时后返回累加器。这里的量化误差相当于将m+1位的求和结果S[n]量化为1位输出C[n]。可以用下图表示

下满用simulink进行建模仿真分析

3.1.2 一阶调制器仿真

假设累加器的位宽为k 位,输入为常数K,则累加器的模数为 2 k 2^k 2k ,每经过一个时钟周期累加器的值增大K,当累加的值超过 2 k 2^k 2k 时,则产生一个进位输出信号C。

搭建累加器模型时,用一个常数设置累加器的最大值,当累加的结果大于等于这个最大值时,产生一个进位输出。同时累加的结果与累加最大值送入取余函数模块进行操作,当累加的结果没有大于设定的累加器最大值时,取余操作后的输出就是本次累加的结果,延时一个单位时间后再输入到加法器进行累加。当累加的结果大于累加器最大值时,取余操作相当于在累计结果中去掉了最大值部分。

其中累加器最大值设为 2 24 2^{24} 224,输入常数为6291456,相当于输入查看仿真结果如下:

本文用到的参考文献及simulink工程文件,点击此处下载

3.2MASH1-1-1设计及仿真

3.2.1 MASH1-1-1 原理

3.2.2 MASH1-1-1 仿真

本文用到的参考文献及simulink工程文件,点击此处下载