时域反射仪(TDR)介绍

TDR-时域反射仪

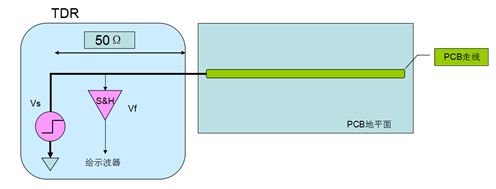

TDR阻抗测试拓扑

拓扑结构如上所示,包含一个阶跃信号源,采样保持器,示波器信号端口和信号输出端口;测试的待测设备是PCB的走线,也就是传输线。

TDR Time-domain reflectometer 时域反射仪

TDR是在时域测量信号的反射电压。依托的原理就是信号在传输线上传输是,如果信号感受到的阻抗不一致,将会导致信号发生反射,反射电压大小取决于阻抗不匹配程度;使用TDR时域反射仪发出阶跃信号,在使用高速示波器测量反射电压值,进而可以得到反射系数,因为源内阻是标准的50R阻抗,所以根据信号速率、时间可以反向计算出在在PCB走线那个位置发生了反射,具体的测试曲线在下面给出:

特性阻抗

特性阻抗是也可以被称之为特征阻抗的;它针对的是高频信号范围而言的(高频信号伴随着电磁场的运动,电场与磁场的切换),它不是我们使用万用表测出来的直流阻抗,属于传输线中的概念。

- 当信号在传输线上传播时,把它走的每一步所受到的阻抗称为瞬时阻抗,瞬时阻抗的值等于线上的电压与电流之比;

- 从电磁场的角度来考虑,它等于该信号在前进时的电场与磁场之比,该值为一定值,且与频率无关。

该值取决于传输线的横截面积与周围材料的特性,比如PCB板的板材以及距离周围地平面间距等;如果一致保持相关参数不变,则瞬时阻抗的值为一恒定值,我们吧时时刻刻相等的瞬时阻抗叫做特性阻抗。

但是实际上因为走线宽度、间距、过孔等导致瞬时阻抗无法时刻相等/处处相等,所以我们采取相关措施来维持瞬时阻抗一致,这个叫做阻抗控制。

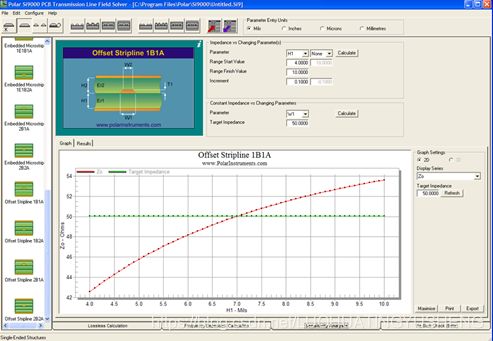

要进行阻抗控制时可以使用SI9000仿真软件,该软件在行业内算是很领先也是比较精确的。

TDR测试曲线

如上图:横轴显示的是时间,纵轴显示的是PCB板不同位置走线的阻抗值;开始时是因为是起始信号的上升沿,后面曲线上升是因为PCB走线已经开路了。

时间如何对应阻抗呢?首先我们测试的是反射电压,反射电压是阻抗不连续的点反射回来的,我们可以记录阶跃信号发出的时间,可以记录反射电压回到示波器的时间,减去测试仪器走线的补偿,此时就可以计算出信号在PCB走线上传输到反射点的时间,基于此可以得到那个位置出现了阻抗不连续点。

上图,如果说我们希望测试的阻抗在50Ω,则不可能达到绝对的50Ω,允许有上下误差,例如上图我们允许50+/-5Ω,即就是45~55Ω,只要在这个范围内我们就认定是合格的。

走线导致多次反射

如果PCB走线存在多次阻抗不一致导致多次反射,要使用专有软件来解决。

当测试者使用高分辨率TDR设备对芯片进行失效分析或者是对高速的PCB背板进行TDR测试时,可能会遇到芯片内部或者是PCB背板的各种复杂的走线情况所带来的多重反射现象,从而给寻找短路/断路点的位置带来了很大的困难。

当被测试的走线上存在多个阻抗不连续点时,例如DUT的走线含有多个转角或者穿层,那么信号在穿越每两个相邻的阻抗不连续点时都会产生反射,所有的反射信号会叠加在一起后反映在仪器上的波形将会是乱的。多重反射的存在导致测试者无法将测试波形结果与DUT走线相对应,带来疑惑。

如果使用专用TDR软件,将原始的TDR测试波形按照反射的情况进行分段,通过解卷积(De-convolution/又称为去卷积)算法可纠正多重反射给测试带来的影响,还原真实的面貌。获得与DUT走线情况相符合的阻抗测试结果。

Reference

IPC ORG制定的PCB、Cable、Connector互联环境特性阻抗测试标准:IPC_2557A。

https://www.ipc.org/TM/2-5-5-7a.pdf

维普百科TDR介绍:

https://en.wikipedia.org/wiki/Time-domain_reflectometer

泰克TDR测试介绍:https://wenku.baidu.com/view/84c5dd0303d8ce2f00662348.html?sxts=1562913766689

https://max.book118.com/html/2018/0215/153341480.shtm

国产TDR阻抗测试应用:

https://max.book118.com/html/2017/0831/130925590.shtm

TDR使用介绍:

https://max.book118.com/html/2017/0908/132744842.shtm

http://www.electrical-integrity.com/Paper_download_files/DC13_Determining_PCB_Trace_Impedance.pdf

2019-07-15一剑转战三千里