TMS320F28335之外部接口

28335的XINTF接口没有中断设置,初始化配置XINTF模块就可直接使用,数据访问地址格式为Data=(^(volatile Uint16^)(0x4000+ 0x0000)),其中0x4000为基地址,0x0000为偏移地址,^为指针符号*。由此总结xintf接口配置步骤为:

1、设置GPIO为xintf模块。

2、开启xintf时钟。

3、设置xintf模块配置

4、访问或写入xintf地址。

- 外部接口头文件DSP2833x_Xintf.h程序如下

// TI File $Revision: /main/4 $

// Checkin $Date: July 27, 2009 13:57:25 $

//###########################################################################

//

// FILE: DSP2833x_Xintf.h

//

// TITLE: DSP2833x Device 外部接口寄存器定义.

//

//###########################################################################

// $TI Release: DSP2833x/DSP2823x C/C++ Header Files V1.31 $

// $Release Date: August 4, 2009 $

//###########################################################################

#ifndef DSP2833x_XINTF_H

#define DSP2833x_XINTF_H

#ifdef __cplusplus

extern "C" {

#endif

// XINTF 时序寄存器位定义:

struct XTIMING_BITS { // bits 描述

Uint16 XWRTRAIL:2; // 1:0 写访问跟踪时间

Uint16 XWRACTIVE:3; // 4:2 写访问有效时间

Uint16 XWRLEAD:2; // 6:5 写访问建立时间

Uint16 XRDTRAIL:2; // 8:7 读访问跟踪时间

Uint16 XRDACTIVE:3; // 11:9 读访问有效时间

Uint16 XRDLEAD:2; // 13:12 读访问建立时间

Uint16 USEREADY:1; // 14 区域XREADY信号采样使能

Uint16 READYMODE:1; // 15 采样方式控制

Uint16 XSIZE:2; // 17:16 数据总线宽度设定

Uint16 rsvd1:4; // 21:18 保留

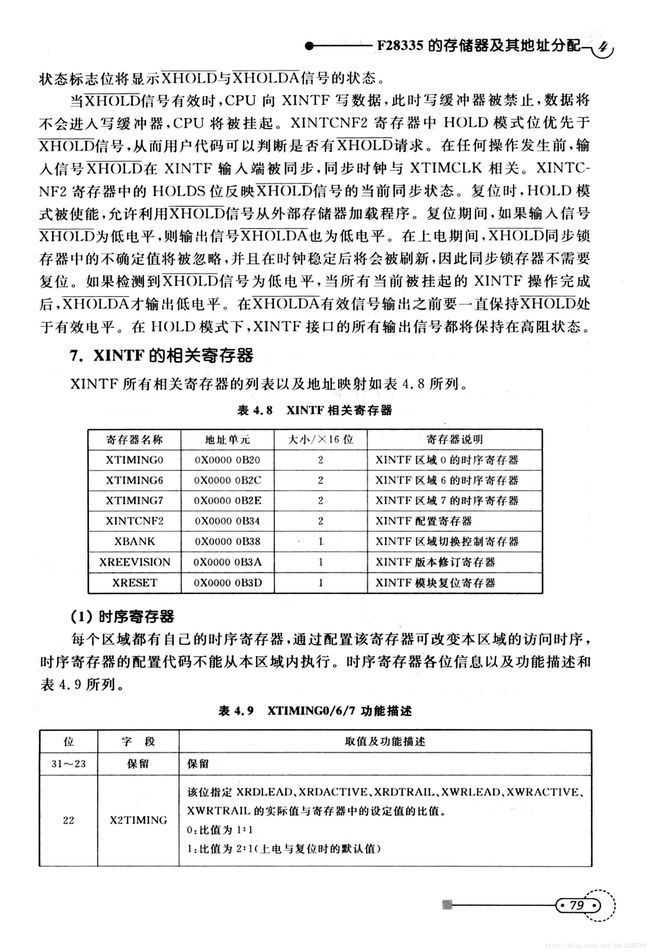

Uint16 X2TIMING:1; // 22 实际值与设定值比值

Uint16 rsvd3:9; // 31:23 保留

};

//时序寄存器

union XTIMING_REG {

Uint32 all;

struct XTIMING_BITS bit; //时序寄存器位定义

};

// XINTF 控制寄存器位定义:

struct XINTCNF2_BITS { // bits 描述

Uint16 WRBUFF:2; // 1:0 写缓冲器深度控制位

Uint16 CLKMODE:1; // 2 XCLKOUT 时钟频率控制位

Uint16 CLKOFF:1; // 3 使能 XCLKOUT

Uint16 rsvd1:2; // 5:4 保留

Uint16 WLEVEL:2; // 7:6 写缓冲寄存器数据个数

Uint16 rsvd2:1; // 8 保留

Uint16 HOLD:1; // 9 自动允许外部设备请求

Uint16 HOLDS:1; // 10 请求对总线访问状态

Uint16 HOLDAS:1; // 11 进行外部设备访问状态

Uint16 rsvd3:4; // 15:12 保留

Uint16 XTIMCLK:3; // 18:16 配置XTIMCLK

Uint16 rsvd4:13; // 31:19 保留

};

//配置寄存器

union XINTCNF2_REG {

Uint32 all;

struct XINTCNF2_BITS bit; //配置寄存器位定义

};

// XINTF 区域切换控制寄存器位定义:

struct XBANK_BITS { // bits 描述

Uint16 BANK:3; // 2:0 切换时的插入时间

Uint16 BCYC:3; // 5:3 指定区域

Uint16 rsvd:10; // 15:6 保留

};

//区域切换控制寄存器

union XBANK_REG {

Uint16 all;

struct XBANK_BITS bit; //区域切换控制寄存器位定义

};

//模块复位寄存器位定义

struct XRESET_BITS {

Uint16 XHARDRESET:1;

Uint16 rsvd1:15;

};

//模块复位寄存器

union XRESET_REG {

Uint16 all;

struct XRESET_BITS bit; //模块复位寄存器位定义

};

//---------------------------------------------------------------------------

// XINTF 寄存器文件:

//

struct XINTF_REGS {

union XTIMING_REG XTIMING0; //区域0时序寄存器

Uint32 rsvd1[5]; //保留

union XTIMING_REG XTIMING6; //区域6时序寄存器

union XTIMING_REG XTIMING7; //区域7时序寄存器

Uint32 rsvd2[2]; //保留

union XINTCNF2_REG XINTCNF2; //配置寄存器

Uint32 rsvd3; //保留

union XBANK_REG XBANK; //区域切换控制寄存器

Uint16 rsvd4; //保留

Uint16 XREVISION; //版本修订寄存器

Uint16 rsvd5[2]; //保留

union XRESET_REG XRESET; //模块复位寄存器

};

//---------------------------------------------------------------------------

// XINTF 外部引用 & 函数声明:

//

extern volatile struct XINTF_REGS XintfRegs;

#ifdef __cplusplus

}

#endif /* extern "C" */

#endif // end of DSP2833x_XINTF_H definition

//===========================================================================

// No more.

//===========================================================================

- XINTF配置文件DSP2833x_Xintf.c程序如下

// TI File $Revision: /main/5 $

// Checkin $Date: August 16, 2007 11:06:26 $

//###########################################################################

//

// FILE: DSP2833x_Xintf.c

//

// TITLE: DSP2833x Device 外部接口初始化 & 支持函数.

//

// DESCRIPTION:

//

// Example initialization function for the external interface (XINTF).

// This example configures the XINTF to its default state. For an

// example of how this function being used refer to the

// examples/run_from_xintf project.

//

//###########################################################################

// $TI Release: DSP2833x/DSP2823x C/C++ Header Files V1.31 $

// $Release Date: August 4, 2009 $

//###########################################################################

#include "DSP2833x_Device.h" // DSP2833x Headerfile Include File

#include "DSP2833x_Examples.h" // DSP2833x Examples Include File

//---------------------------------------------------------------------------

// InitXINTF:

//---------------------------------------------------------------------------

// 改函数将外部接口初始化至默认的复位状态.

//

// Do not modify the timings of the XINTF while running from the XINTF. Doing

// so can yield unpredictable results

void InitXintf(void)

{

// 这显示了如何写XINTF寄存器。

// 这里使用了重置后的默认状态值。

// 不同的硬件需要不同的配置。

// 为INTF配置一个例子,在如下目录

// F28335 eZdsp, refer to the examples/run_from_xintf project.

// 任何更改XINTF配置只能从XINTF扩展之外的区域运行代码。

// 所有区域---------------------------------

// 所有区域的基准时间时钟为 XTIMCLK = 1/2 SYSCLKOUT

EALLOW;

SysCtrlRegs.PCLKCR3.bit.XINTFENCLK = 1; //开启XINTF时钟信号

XintfRegs.XINTCNF2.bit.XTIMCLK = 1; //基准时钟XTIMCLK = 1/2 SYSCLKOUT

XintfRegs.XINTCNF2.bit.WRBUFF = 0; //无写缓冲寄存器

XintfRegs.XINTCNF2.bit.CLKOFF = 1; //禁止XCLKOUT

XintfRegs.XINTCNF2.bit.CLKMODE = 1; //XCLKOUT=XTIMCLK/2

XintfRegs.XTIMING0.bit.XWRLEAD = 2; //区域0写建立时间为11b,周期数为6

XintfRegs.XTIMING0.bit.XWRACTIVE = 5; //有效时间为111b,周期数为14

XintfRegs.XTIMING0.bit.XWRTRAIL = 2; //跟踪时间为11b,周期数为6

// Zone read timing

XintfRegs.XTIMING0.bit.XRDLEAD = 2; //区域0读建立时间为11b,周期数为6

XintfRegs.XTIMING0.bit.XRDACTIVE = 5; //有效时间为111b,周期数为14

XintfRegs.XTIMING0.bit.XRDTRAIL = 2; //跟踪时间为11b,周期数为6

// double all Zone read/write lead/active/trail timing

XintfRegs.XTIMING0.bit.X2TIMING = 1; //比值2:1

// Zone will sample XREADY signal

XintfRegs.XTIMING0.bit.USEREADY = 0; //XREADY信号采样

XintfRegs.XTIMING0.bit.READYMODE = 1; //异步采样

XintfRegs.XTIMING0.bit.XSIZE = 3; //数据总线宽度,16位

//*****************************************************************************//

//片外ram访问

//****************************************************************************//

XintfRegs.XTIMING6.bit.XWRLEAD = 3; //区域6写建立时间为11b,周期数为6

XintfRegs.XTIMING6.bit.XWRACTIVE = 7; //有效时间为111b,周期数为14

XintfRegs.XTIMING6.bit.XWRTRAIL = 3; //跟踪时间为11b,周期数为6

// Zone read timing` `

XintfRegs.XTIMING6.bit.XRDLEAD = 3; //区域6读建立时间为11b,周期数为6

XintfRegs.XTIMING6.bit.XRDACTIVE = 7; //有效时间为111b,周期数为14

XintfRegs.XTIMING6.bit.XRDTRAIL = 3; //跟踪时间为11b,周期数为6

// double all Zone read/write lead/active/trail timing

XintfRegs.XTIMING6.bit.X2TIMING = 1; //比值

// Zone will sample XREADY signal

XintfRegs.XTIMING6.bit.USEREADY = 0; //不对ready信号采样

XintfRegs.XTIMING6.bit.READYMODE = 1; //异步采样

XintfRegs.XTIMING6.bit.XSIZE = 3; //数据总线宽度,16位

// Zone 7------------------------------------

XintfRegs.XTIMING7.bit.XWRLEAD = 3; //区域7写建立时间为11b,周期数为6

XintfRegs.XTIMING7.bit.XWRACTIVE = 7; //有效时间为111b,周期数为14

XintfRegs.XTIMING7.bit.XWRTRAIL = 3; //跟踪时间为11b,周期数为6

// Zone read timing

XintfRegs.XTIMING7.bit.XRDLEAD = 3; //区域7读建立时间为11b,周期数为6

XintfRegs.XTIMING7.bit.XRDACTIVE = 7; //有效时间为111b,周期数为14

XintfRegs.XTIMING7.bit.XRDTRAIL = 3; //跟踪时间为11b,周期数为6

// double all Zone read/write lead/active/trail timing

XintfRegs.XTIMING7.bit.X2TIMING = 1; //比值2:1

// Zone will sample XREADY signal

XintfRegs.XTIMING7.bit.USEREADY = 0; //XREADY信号采样

XintfRegs.XTIMING7.bit.READYMODE = 1; //异步采样

// Size must be either:

XintfRegs.XTIMING7.bit.XSIZE = 3; //数据总线宽度,16位

// Bank switching

XintfRegs.XBANK.bit.BANK = 0; //区域7被指定

XintfRegs.XBANK.bit.BCYC = 7; //区域切换的插入延时时间

EDIS;

//Force a pipeline flush to ensure that the write to

//the last register configured occurs before returning.

// InitXintf32Gpio();

// asm(" RPT #7 || NOP");

}

//===========================================================================

// No more.

//===========================================================================

- 参考资料

《手把手教你学DSP:基于TMS320F28335》

《TMS320F28335DSP原理与开发编程》

《28335接口扩展 (XINTF) 参考指南》