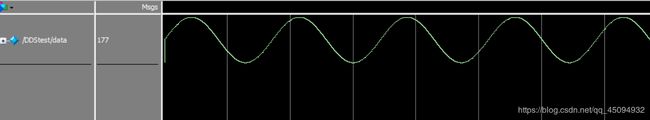

modelsim仿真正弦波时为什么一直显示XXX

利用MiF文件产生正弦波,发现一直输出XXX,困扰了好几个月,也没搜到确切的解答。一直怀疑是mif文件的问题。后来发现寄存器没有初始化。最初只注意初始化赋值参数了,结果把寄存器初始化忘了。切记,要初始化。

下面附上代码:

MATLAB生成mif文件代码

F1=1; %信号的频率

Fs=2^10;%采样频率

P1=0;%信号初始相位

N=2^10;%采样点数为N

t=[0:1/Fs:(N-1)/Fs];%采样时刻

ADC=2^10/2 - 1;%直流分量

A=2^10/2;%信号幅度

s=A*sin(2*pi*F1*t + pi*P1/180)+ADC;%生成信号

plot(s);%绘制图形

fild = fopen('C:\Users\xh941\Desktop\FPGA\rtl\sin.mif','w');%创建mif文件

%写入mif文件文件头

fprintf(fild, '%s\r\n','WIDTH=10;');%位宽

fprintf(fild, '%s\r\n','DEPTH=1024;');%深度

fprintf(fild, '%s\r\n','ADDRESS_RADIX=HEX;');%地址格式

fprintf(fild, '%s\r\n\n','DATA_RADIX=HEX;');%数据格式

fprintf(fild, '%s\t','CONTENT');%地址

fprintf(fild, '%s\r\n','BEGIN');%

for i = 1:N

s2(i) = round(s(i)); %对小数四舍五入以取整

if s2(i) <0 %强制将负1置0,

s2(i) = 0

end

% addr : data;

fprintf(fild, '\t%x',i-1);%地址,从0开始编码

fprintf(fild, '%s\t',':');

fprintf(fild, '%x',s2(i));

fprintf(fild, '%s\r\n',';');

end

fprintf(fild,'%s\r\n','END;')

顶层文件

module DDS(clk, rst_n,sin_data);

input clk;//时钟输入

input rst_n;

output sin_data;

wire [9:0] set_p;

/**************连接线***************/

wire [31:0] f32_bus;//AC频率控制字输入

wire [31:0] reg32_out;//32位寄存器输出

wire [31:0] reg32_in;//32位寄存器输入

wire [9:0] reg10_in;

wire [9:0] reg10_out_address;

/**************缓存寄存器******************/

wire [9:0] sin_data;

/***********************************/

assign f32_bus[31:22]=10'd0;//初始化,高位置低

assign f32_bus[21:0]=22'd10000; //低位可以设置DDS的输出频率

assign set_p=10'd0;

/*********************元件例化************************************/

add32 u1(.data1(f32_bus),.data2(reg32_out),.sum(reg32_in));

reg32 u2(.clk(clk),.rst_n(rst_n),.data_in(reg32_in),.data_out(reg32_out));

adder_10 u3(.data1(set_p),.data2(reg32_out[31:22]),.sum(reg10_in));

reg_10 u4(.clk(clk),.rst_n(rst_n),.data_in(reg10_in),.data_out(reg10_out_address));

sin u5(.address(reg10_out_address),.clock(clk),.q(sin_data));//正弦

endmodule

32位加法器

module add32(data1,data2,sum);

input [31:0] data1;

input [31:0] data2;

output [31:0]sum;

assign sum =data1+data2;

endmodule

32位寄存器

module reg32(clk,rst_n,data_in,data_out);

input clk;

input rst_n;

input [31:0] data_in;

output [31:0]data_out;

reg [31:0] data_out;

always@(posedge clk)

begin

if(!rst_n)

data_out<=32'd0;

else

data_out<=data_in;

end

endmodule

10位加法器

module adder_10(data1,data2,sum);

input [9:0] data1,data2;//输入数1,2

output [9:0] sum;//和输出

wire [9:0] data1,data2;

wire [9:0] sum;

assign sum=data1+data2;

endmodule

10位寄存器

module reg_10(clk,rst_n,data_in,data_out);

input clk;

input rst_n;

input [9:0] data_in;

output [9:0]data_out;

reg [9:0] data_out;

always@(posedge clk)

begin

if(!rst_n)

data_out<=10'd0;

else

data_out<=data_in;

end

endmodule

test文件

`timescale 10ns/1ps

module DDStest();

reg clk;

reg reset;

wire [9:0]data;

DDS u9(.clk(clk),.rst_n(reset),.sin_data(data));

initial

begin

clk=1'b0;

reset=1'b0;

#10 reset=1'b1;

end

always #1 clk<=~clk;

endmodule

module reg32(clk,rst_n,data1,data2,data_out);

input clk;

input rst_n;

input [31:0] data1,data2;

output [31:0]data_out;

reg [31:0] data_out;

always@(posedge clk)

begin

if(!rst_n)

data_out<=32'd0;

else

data_out<=data1+data2;

end

endmodule

module reg10(clk,rst_n,data1,data2,data_out);

input clk;

input rst_n;

input [9:0] data1,data2;

output [9:0]data_out;

reg [9:0] data_out;

always@(posedge clk)

begin

if(!rst_n)

data_out<=10'd0;

else

data_out<=data1+data2;

end

endmodule