Altium Designer之DRC检查学习笔记

Altium Designer(简称AD),是电子设计师设计、绘制PCB的常用的工具之一。

Design Rule Check(DRC),是检查设计是否满足所设置的规则,是PCB完成前最为重要的一步。通过检查来判定是否满足设计的要求,需要检查什么,就打开相关的检查选项,该设置涉及检查PCB板内容,需要每次都重新配置相关内容。具体操作的方法如下:

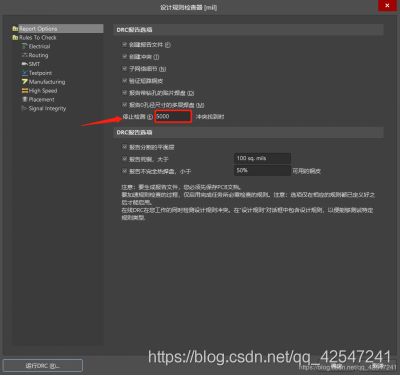

1.执行菜单命令“工具→设计规则检查(快捷键“TD”),Report Options(报告选择)一般按照系统默认的选项即可,如图1-1所示。

详情:①创建报告文件:执行完DRC之后,Altium Designer会创建一个关于DRC的报告,对报错信息会给出详细的描述并会给出报错的位置信息,方便设计者对报错信息进行解读,如图1-2所示。

② 创建冲突检查次数:将创建冲突检查次数设置为5000,表示当系统检测到5000个DRC报错的时候直接停止再次检查,系统默认设置一般是500,但是设置到500时有些DRC会进行显示,有些DRC不会进行显示,只有修正已存在的错误,再次DRC的时候才会显示,这样对于大板设计非常不方便。

③设置DRC检查项目,如图1-3所示,在“Online(在线/自动)”和“Batch(批量/手动)”栏中勾选使能检查。

备注: Online(在线/自动)如果PCB设计当中存在DRC报错时可以实时的显示出来

Batch(批量/手动)只有手工执行DRC检查时,存在问题的报错才会显示出来。

一般来说我们需要检查DRC的时候两者都进行勾选,方便实时检查和手动检查同时进行。DRC检查不是说所有的规则都需要检查,设计者只需要检查自己想需要检查的规则即可,不想检查的规则对应的“Online”和“Batch”勾取消掉就好了。

2.Rule To Check(规则检查):包括Electrial(电气属性)、Routing(走线)、SMT(表贴焊盘规则)、Testpoint(泪点)、Manufacturing(机械装配)、High Speed(高速,多层板)、Placement(元器件的放置)、Siganl Integrity(信号完整性)。 ① Electrial(电气属性):Clearance(间距)、Modified Polygon(差分)、Short-Circuit(短路)、Un-Connected Pin(开路)、Un-Connected Net(网络未连接)。一般情况下,这几个选项保持默认选择即可, 如图2-1所示。

②Routing(走线):Differential Pairs Routing(差分线)、Routing Layers(布线图规则)、Routing Via Style(过孔检查)、Width(线宽)。一般情况下,这几个选项保持默认选择即可, 如图2-2所示。

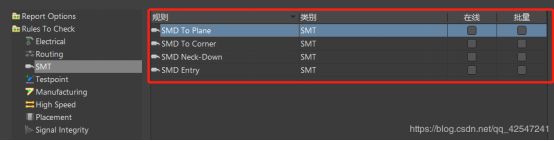

③SMT(表贴焊盘规则):SMD Entry(贴片输入)、SMD Neck-Down(焊盘颈缩率规则)、SMD To Corner(SMD焊盘与导线拐角处最小间距规则 )、SMD To Plane(SMD焊盘与电源层过孔最小间距规则 )。一般情况下,这几个选项全部取消即可, 如图2-3所示。

④ Testpoint(测试点):一般情况下,这几个选项全部取消即可, 如图2-4所示。

⑤Manufacturing(机械装配):一般情况下,这几个选项全部取消即可, 如图2-5所示。

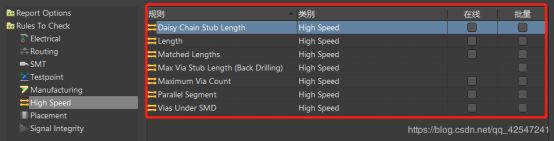

⑥High Speed(高速,多层板):一般情况下,这几个选项全部取消即可,适用于多层板, 如图2-6所示。

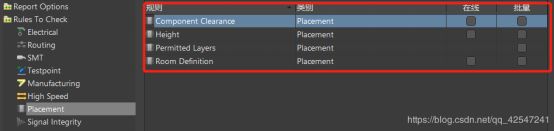

⑦ Placement(元器件的放置):一般情况下,这几个选项全部取消即可, 只要元器件按照我们自己的规则不重叠就行,如图2-7所示。

⑧Siganl Integrity(信号完整性):一般情况下,这几个选项选择默认即可, 如图2-8所示。