第四章 PCIe总线概述

4.1 pcie 总线基础知识

1)PCI是并行连接,一条总线上的多个设备共享总线带宽;

PCIe是差分总线,端到端连接,频率更高;

2)一个数据通路(Lane),有两组差分信号,即4根信号线,TX部件和RX部件相连(这为一组)

一个pcie链路可以有多个lane

2.a) 一个差分信号由D+和D-两根信号组成,接收端通过比较它们的差值来判断是1还是0,与单端信号比,抗干扰能力更强。

2.b)外部噪声加在两根信号上的影响一样,所以可以使用更高的总线频率

3) pcie链路支持1、2、4、8、16、32个lane,即支持这些数据位宽, 常用的是x1

intel的ICH集成了多个x1的pcie链路,MCH集成了x16的pcie链路用于连接显卡控制器

powerPC支持 x1,x2,x4,x8

PCIE不分多少数据位,PCI-E总线更类似串行线,一次通信走1个Bit。比较快主要是频率高,V3.0总线频率达4Ghz,单lane的峰值可达8GT/s=8Gb/s

4) PCIE使用的信号

pcie设备使用2种电源信号供电,Vcc 和 Vaux, 电压为3.3v, Vcc为主电源

PERST#信号, 全局复位,复位设备

REFCLK+ 和 REFCLK-信号,用于与处理器同步

WAKE#, 设备休眠时,主电源停止供电了,可以用该信号通知处理器来唤醒设备

SMCLK, SMDAT, 即SMBus总线,源于I2C,管理处理器系统的外部设备特别是智能电源

JTAG信号,用于芯片内部测试,包括TRST#,TCK,TDI,TDO,TMS信号

PRSNT1#,PRSNT2#, 热插拔相关

5) PCIE总线的层次结构

事务层,接收来自核心层的数据并封装为TLP,还有就是处理pcie中的“序”

数据链路层,继续添加sequence前缀和CRC后缀,有多种DLLP包

物理层,LTSSM状态机管理链路状态,PLP包,系统程序员仍有必要深入理解物理层工作原理

6)pcie链路的扩展

用switch, 1个上游端口连RC,多个下游端口连EP

7)pcie设备的初始化

传统复位convertional reset:包括fundametal 和 non-fundametal, fundametal 又分cold和warm reset; non-fundametal指的是hot reset

FLR复位只复位与PCIE链路相关的部分逻辑

4.2 PCIE体系结构组成部件

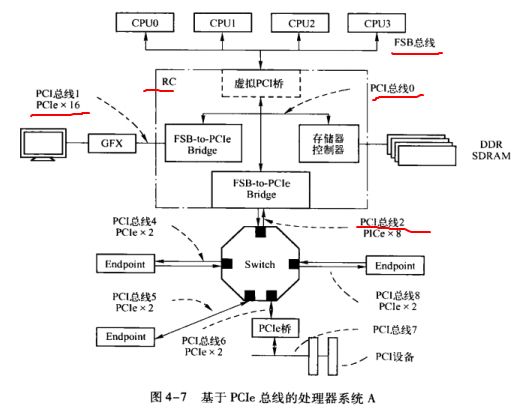

1)大多使用RC、switch、PCIe-to-PCI桥连接设备,而基于pcie总线的设备,称为EP(endpoint)

RC(PCI Express root complex)根联合体, 相当于PCIE主桥,也有称为pcie总线控制器

RC在x86中由MCH和ICH组成, PCIe总线端口存储器控制器等接口集成在一起,统称RC

2)PCIE设备包括 EP(如显卡、网卡等)、switch、PCIE桥

3)RC与HOST主桥不同的是还有RCRB,内置PCI设备,event collector

深入理解RC对理解pcie体系结构非常重要

4)switch有一个上游端口和多个下游端口,上游端口连接RC、其他switch的下游端口,也支持crosslink连接方式(上连上,下连下)

其实是多个PCI桥组成的

PCIE 采用虚拟多通路VC技术,这些报文中设定TC标签,分为8类优先权。每条链路最多支持8个VC,用来收发报文。

软件设置哪类TC由哪个VC传递,许多处理器Switch和RC只支持一个VC,而x86和PLX的switch可以支持两个VC

TC和VC是多对一

5)不同ingress发向同一个egress端口,涉及端口仲裁和路由选径

switch中设有仲裁器,规定报文通过switch的规则。分别基于VC和基于端口的仲裁机制

6)PCIE桥

4.3 pcie设备的扩展配置空间

1)PCIE要求设备必须支持capability结构,重点关注电源管理、MSI中断的capability结构

电源管理capability有PMCR和PMCSR寄存器

2)capability结构:PCIE capability register, device/link/slot 等capability 寄存器

第5章 Montevina 的MCH和ICH

intel的一款笔记本平台

pci 0 上的MCH和ICH,是FSB总线的延伸,虚拟的PCI设备,只是使用PCI的管理方法

1)pci0的device0设备,管理PCI总线地址和存储器地址

device0被认为是HOST主桥

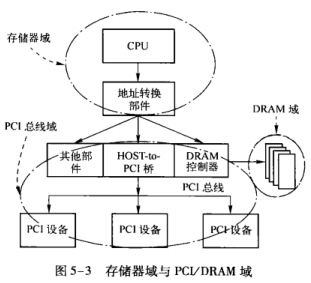

2)存储空间的组成结构

存储器域(CPU可访问)、PCI总线域、DRAM域(主存),有些DRAM只能被显卡控制器访问到,不能被cpu访问

legacy地址空间:x86固有的一段1MB内存空间,DOS内存等

DRAM域:大小保存在MCH的TOM中,即PCI0的配置空间中,legacy地址在它里面

存储器域:

5.3 存储器域的PCI总线地址空间

PCI总线地址空间氛围 最低可用TOLUD~4GB,TOUUD~64GB

1)APIC 是x86使用的中断控制器

2)ECAM方式读写PCIE扩展配置空间,CONFIG_ADDRESS和CONFIG_DATA访问前256B

ECAM是直接映射到内存来访问

第6章 PCIE事务层

第7章 链路层和物理层

第8章 链路训练和电源管理

第9章 流量控制

合理的使用物理链路,避免接收端缓冲区容量不足而丢弃发生端的数据,从而要求重新发送。

第10章 MSI和MSI-X中断机制

PCI:必须支持INTx,MSI可选

PCIe: 必须支持MSI,INTx可选

MSI使用存储器写请求TLP向处理器提交中断请求,即MSI报文。PowerPC使用MPIC中断控制器处理MSI中断请求,X86使用FSB interrupt message方式处理。

绝大多数PCIe设备使用MSI提交中断请求

第11章 PCI/PCIE的序

序是指数据传送的顺序,保证数据完整性的基础

第12章 PCIE总线的应用

12.1 capric卡的工作原理

1) PCIe设备: Vetex-5内嵌的EP模块,该模块也被xilinx称为LogiCORE

先主存到FPGA的片内SRAM(DMA读), 单次DMA最大0X7FF B , 2KB

SRAM到主存 (DMA写)

2)仅使用BAR0,大小256B,里面有DCSR1/2, WR_DMA_ADR/SIZE, INT_REG, ERR

12.3 基于pcie的设备驱动

属于char类型驱动

1)加载与卸载

这段代码主要作用是软件结构pci_driver与硬件结构pci_dev建立联系,pci_register_driver会做这个

2)初始化和关闭

系统在PCI树中发现capric卡后,local_pci_probe调用capric_probe,入口参数pci_dev和ids,进行初始化

初始化调用pci_enable_device使能PCIE设备(会修改command的io space和memory space位看配置空间是否使用它们),调用pcibios_enable_irq分配设备使用的中断向量号

DMA掩码:存储域physical_addr &DMA_MASK = physical_addr表示可以对这段内存DMA操作

a) linux中存储器映射的寄存器和io映射的寄存器都是ioresources管理,pci_request_regions把capric卡的BAR0使用的resource结构其name设置为DEV_NAME, flags设为IORESOURCE_BUSY,

b) pci_resource_start 获得pci_dev资源的BAR0空间的基地址(存储器域物理地址),pci_read_config_word是pci域

c) ioremap将存储器域物理地址映射为linux虚拟地址

d)register_chrdev 注册char设备驱动

e) pci_enable_msi 使能MSI中断请求机制

f) request_irq(capric_interrupt) 使用中断服务例程

3) DMA读写

DMA写: 与capric_read对应

kmalloc,实际驱动中很少在读写服务例程中申请内存,容易产生内存碎片,时间花费也长。

pci_map_single虚拟地址转换为PCI物理地址

DMA读:capric_write

dma_sync_single 存储器与cache同步

interruptible_sleep_on 等待

4)中断处理

系统的do_IRQ调用 capric_interrupt

这里直接设置读写例程里面的等待事件就好

5)存储器地址到PCI地址转换

pci_map_single,

最初x86是直接相等的关系,为了支持虚拟化技术使用了VT-d/IOMMU技术

powerpc是inbound寄存器把PCI转换为存储器地址,inbound可以看做一种IOMMU

6)存储器与cache同步

低端处理器不支持硬件cache共享一致性,需要在DMA操作之前,用软件将操作的数据区域与cache同步

多数PCI设备,cache一致性可以由硬件保证

12.4 带宽和时延

优化:减少对寄存器的读操作,如要读终端控制器状态寄存器可以改为收发等分开的IRQ

流水线ring buffer技术,多路DMA读写并行执行

第13章 PCI与虚拟化技术

多个虚拟处理器系统,多个独立的操作系统,用一套CPU、内存和外部设备