SPI完整讲解(一)

SPI协议是由摩托罗拉公司提出的通讯协议(Serial Peripheral Interface),即串行外围设备接口,是一种高速全双工的通信总线,它被广泛地使用在ADC,LCD等设备与MCU间,要求通讯速率较高的场合。

SPI物理层

上图中下面是作为SPI通信的主机,上面可以挂载不同的从机,同IIC一致,总线上是可以挂载很多设备的

SS线:每个从设备都有独立的这一条SS信号线,本信号线独占主机的一个引脚,即有多少 个从设备,就有多少条片选信号线.I2C 协议中通过设备地址来寻址,选中总线上的某个设备并与其进行通讯;而SPI协议中没有设备地址,它使用SS信号线来寻址,当主机要选择从设备时,把该从设备的SS 信号线设置为低电平,该从设备即被选中,即片选有效,接着主机开始与被选中的从设备进行SPI通讯.所以SPI通讯以SS线 置低电平为开始信号,以SS线被拉高作为结束信号,SS线通常称为片选信号线,也称为NSS,CS

SDA:时钟信号线,用于通讯数据,它由通讯主机产生,决定了通讯的速率,不同的设备支持的最高时钟频率不一样,如STM32的SPI时钟频率最大为fpclk/2,pclk为APB2时钟两个设备之间通讯时,通讯速率受限于低速设备,SPI1在APB2时钟线上,SPI2,SPI3在APB1时钟线上

MOSI (Master Output,Slave Input):主设备输出/从设备输入引脚,主机的数据从这条信号线输出,从机由这条信号线读入主机发送的数据,即这条线上数据的方向为主机到从机。

MISO(Master Input,Slave Output):主设备输入/从设备输出引脚,主机从这条信号线读入数据,从机的数据由这条信号线输出到主机,即在这条线上数据的方向为从机到主机。

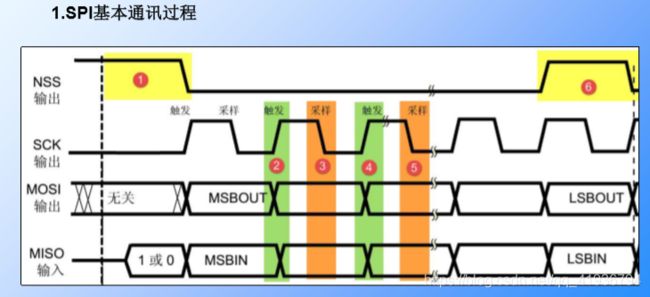

SPI协议层:

首先通讯开始时NSS引脚由高变低选中挂载在总线上的其中一台从机设备,通讯结束时该引脚由低变高作为停止信号,只要不拉低信号线就可以一直传输数据,SCK线的触发代表数据的变化,即在上升沿阶段数据(可以设置什么边沿是触发状态)可以变化,可以看到MOSI和MISO线上的数据发生变化不稳定,而采样阶段发生在下降沿阶段(可以设置什么边沿是采用状态),可以看到MOSI和MISO线上的数据不发生变化而且稳定,所以此时可以传输获得数据,1个数据需要1个时钟周期,1个字节数据就需要8个时钟周期,需要查看从机设备是高位先行还是低位先行的,还有就是时钟极性和位,GPOL/GPHA, 时钟极性CPOL是指SPI通讯设备处于空闲状态时,SCK信号线的电平信号 (即SPI通讯开始前, NSS线为高电平时SCK的状态).CPOL=0时SCK 在空闲状态时为低电平,CPOL=1时,则相反. 时钟相位CPHA是指数据的采样的时刻,当CPHA=0时,MOSI或MISO数 据线上的信号将会在SCK时钟线的“奇数边沿”被采样.当CPHA=1时,数据线在SCK的“偶数边沿”采样。

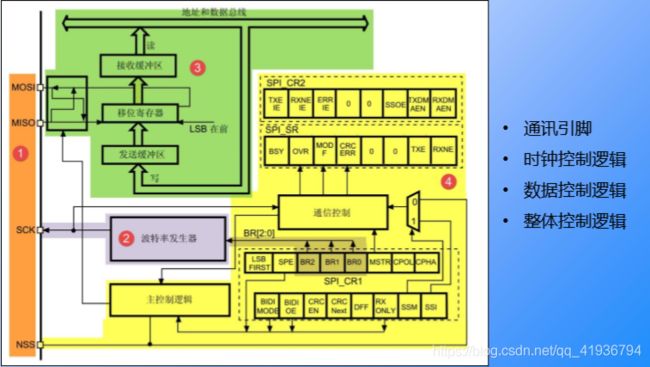

SP1框图讲解

STM32的SPI外设可用作通讯的主机及从机,支持最高的SCK时钟频率为fpclk/2 (STM32F10x型号的芯片默认fpclk1为72MHz,fpclk2为36MHz),完全支持SPI协议的4种模式,数据帧长度可设置为8位或16位,并不是只可以传输8位或16位可设置数据 MSB先行或LSB先行。它还支持双线全双工,双线单向以及单线模式

这里NSS引脚我们可以使用GPIO引脚的推挽模式输出来模拟开始停止,而不使用硬件产生

时钟控制逻辑:

SCK线的时钟信号,由波特率发生器根据“控制寄存器SPI_CR1” 中的BR[0:2]位控制,该位是对fpclk时钟的分频因子,对fpclk的分频结果就是SCK引脚的输出时钟频率,对应框图的2部分

数据控制逻辑:

SPI的MOSI及MISO都连接到数据移位寄存器上,数据移位寄存器的数据来源来源于接收缓冲区及发送缓冲区,通过写SPI的“数据寄存器DR”把数据填充到发送缓冲区中.通过读“数据寄存器SPI_DR”,可以获取接收缓冲区中的内容.其中数据帧长度可以通过“控制寄存器SPI_CR1”的“DFF位”配置成8位及16位 模式;配置“LSBFIRST位”可选择MSB先行还是LSB先行,对应3部分

整体控制逻辑:

整体控制逻辑负责协调整个SPI外设,控制逻辑的工作模式根据“控制寄存器 (SPI_CR1/SPI_CR2)”的参数而改变,基本的控制参数包括前面提到的SPI模式,波特率,LSB先行,主从模式,单双向模式等等,对应4部分

SPI通讯过程

发送过程:

在当前模式下,拉低SCK表示开始传送数据,首先往SPI_DR写入0xF1,此时TXE标志是低电平,TXE标志拉高为高电平表示发送缓冲区的数据写入移位寄存器用以发送出去,而且此时表示缓冲区清空,此时又可以写入0xF2到缓冲区,当移位寄存器中的0xF1发送出去后,TXE标志拉高为高电平表示现在的缓冲区中的0xF2被清空写入移位寄存器发送出去,这样一个循环的过程就可以把很多字节发送出去,BSY标志用来检测总线是否忙中

接受过程

SPI是全双工的,所以接受和发送过程是同步进行的,软件等待至RXNE=1时,表示接受缓冲区有数据可读,可以通过SPI_DR寄存器读出数据,循环这个过程,假设我们只是接受数据我们也要往发送缓冲区写入数据,触发SCK时钟的产生