ARM-中断状态,中断响应流程(四大步三小步)

ARM-异常及中断处理

- 中断

- 中断

- 中断源

- 中断/异常优先级

- 异常和中断的区别

- 中断的状态

- ARM-7种异常类型

- ARM-异常中断的响应流程(四大步三小步)

- 软中断 汇编测试代码

中断

中断

1) 硬中断

在处理器中,中断是一个过程。即CPU在正常执行程序的过程中,遇到外部或内部的紧急事件需要处理,暂时中断(中止)当前程序的执行,而转去完成事件服务程序,待事件完毕后,再返回到暂停处(断点)继续执行原来的程序。事件服务程序又称中断处理程序或中断服务程序。严格意义上来说,上面的描述是针对硬件中断而言的。

2) 软中断

用软件方法引起的中断,即事先在程序中安排特殊的指令,CPU执行到该类指令的时候,会跳转去执行相应的一段预先安排好的程序,待程序执行完,再返回原来程序处。这种通过软件方法实现的中断叫软中断。

3) 软、硬中断和信号的区别

- 硬中断的出现过程是不可预测的,是随机的;而软中断是预先安排好的指令中断方式。

- “硬中断是外部设备对CPU的中断”,“软中断通常是硬中断服务程序对内核的中断”,“信号则是由内核(或其他进程)对某个进程的中断”。

中断源

把引起中断的原因,或者能够发出中断请求信号的来源统称为中断源。

中断/异常优先级

ARM处理器五种模式对应的7种异常源优先级顺序(从高到低):

1 复位异常(reset)

2 数据异常(Data Abord)

3 快速中断异常(FIQ)

4 外部中断异常(IRQ)

5 预取异常(prefetch Abord)

6 软中断异常(SWI)

7 未定义指令异常(Undefined)

异常和中断的区别

异常主要是从处理器被动接受异常的角度来考虑;中断带有主动请求处理器处理中断的意味。

共同点:都是打断当前程序执行,进入特定的程序处理事件的一种机制。

中断的状态

- 挂起态:中断已发生,但是中断没有被处理执行

- 激活态:中断发生,正在执行对应的中断处理函数,但是还没有执行结束

- 未激活态:中断没有发生。

ARM-7种异常类型

1) 复位异常(reset)

两种情况引起异常:系统上电/系统复位

复位异常中断处理程序完成的功能:

- 设置异常向量表

- 初始化栈和寄存器

- 初始化MMU,Cache

- 初始化关键的I/O设备

- 使能中断

- 切换到SVC模式

- 初始化C程序中的变量,跳转到相应程序的执行

2)数据异常(Data Abord)

存储器访问指令load/store访问外部数据时,出现地址不存在或不允许访问等时产生:取数据中止异常

3)快速中断异常(FIQ)

4)外部中断异常(IRQ)

5)预取异常(prefetch Abord)

取一条被标记无效的指令时:取指令中止异常

6)软中断异常(SWI)

软中断发生,系统进入SVC模式,跳转到处理程序

7)未定义指令异常(Undefined)

:未定义指令的异常,指令取出后通过译码器后未定义指令导致译码出错

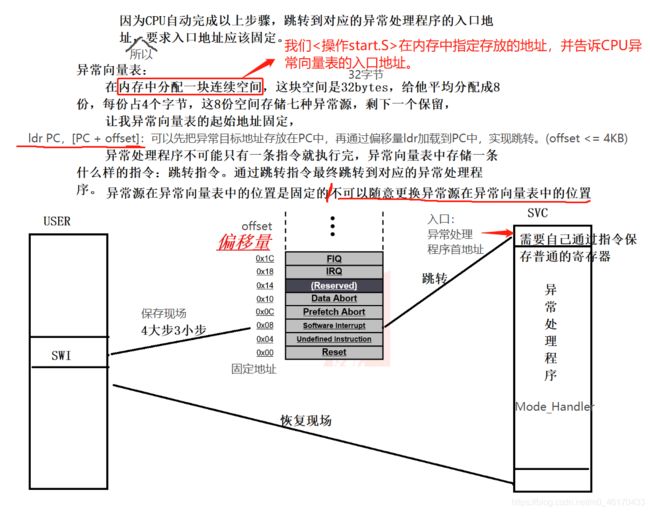

ARM-异常中断的响应流程(四大步三小步)

注意:

- User和System模式是不可通过异常进入的两种模式,即要进入这两种模式,必须要编程设置CPSR的模式状态。

- ARM处理器中cortex-A不支持中断嵌套,因为ARM处理器的处理中断处理速度较快;

- cortex-M系列支持中断嵌套,eg:stm32。

ARM异常处理:处理器对特定的异常事件进行的处理流程(CPU指导硬件自动完成:四大步三小步)。

一、保存现场(四大步):

1)保存CPSR到SPSR_mode

2)适当设置 CPSR 对应功能位(三小步):

- 1、切换处理器进入ARM状态:T[5]

- 2、根据需要,禁止中断位:F[6] / I[7]

- 3、根据异常切换到对应的异常模式:M[4:0]

3)保存返回地址:把当前 PC 保存到 lr_mode

4)设置PC = 存放跳转到对应的异常向量表的固定首地址。

二、恢复现场(必须手动恢复):

1)恢复 SPSR_mode 到 CPSR

2)恢复 lr_mode 到 PC

3)恢复普通寄存器:R0-R7,操作sp将栈中将数据恢复。

软中断 汇编测试代码

.text

.globl _start

_start:

b reset

b undefined_instruction

b software_interrupt

b prefetch_abord

b data_abord

b reserved

b irq

b fiq

reset:

@初始化SVC下的栈内存空间

ldr sp, =0x40000100

@切换到User模式下0xD3:SVC;0xD0:User

msr CPSR, #0xD0

@初始化User下的栈内存空间

ldr sp, =0x40000200

@执行用户代码

mov r0, #0x1

mov r1, #0x2

@swi软中断:swi <软中断号,取值范围:0-(2^24-1)>

swi 2

@执行用户代码:r2 = 1+2 = 3

add r2, r0,r1

undefined_instruction:

software_interrupt:

@保存现场

stmfd sp!,{r0-r1, lr}

@执行用户代码

mov r0, #0x5

mov r1, #0x6

add r3, r0,r1

@恢复现场:{r0-r1,pc}将lr恢复给pc,"^"是表示将SPSR恢复到CPSR

ldmfd sp!, {r0-r1,pc}^

prefetch_abord:

data_abord:

reserved:

irq:

fiq:

loop:

b loop

.end